Fターム[5F140BK21]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域形成後の処理 (2,202) | 熱処理 (1,739) | 活性化 (1,499)

Fターム[5F140BK21]に分類される特許

1,481 - 1,499 / 1,499

シリサイド成長ドーパント雪かき効果の使用による、デバイス中に階段接合の形成

トランジスタ(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に絶縁層(702)をたい積する。その後、絶縁層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

乱数生成素子

【課題】 増幅回路を用いなくても1Mbit/s以上の乱数生成レートが可能となるような物理現象中のランダムノイズを利用した乱数生成素子を提供することを目的とする。

【解決手段】 半導体表面との間で非常に薄いトンネル絶縁膜を介して電子の充放電が可能な導電性微粒子をチャネル上に設け、チャネル幅Wを狭く、かつ導電性微粒子の面密度Ddotを多く、かつチャネル〜導電性微粒子間のトンネル抵抗を小さくする。例えば、膜厚0.8nmのシリコン窒化膜をトンネル絶縁膜とするバルク基盤上の素子の場合、チャネル幅W=0.1μm、平均粒径d=8nm程度のSi微結晶粒子群を1.7×1012cm−2程度の面密度で形成すると、1MHzのノイズ成分を0.1%にできる。

(もっと読む)

シリサイドをソース/ドレインに用いた半導体素子

半導体素子において、非常に深い位置に達するゲルマニウムイオン注入及びゲルマニウムの活性化をニッケルシリサイド形成用のニッケルの堆積の前に行なう。ゲルマニウムを活性化させることにより、イオン注入領域の格子定数が、シリコンであることが好ましい母体基板の格子定数よりも大きくなる。このような変化が加えられた格子によって、ニッケルダイシリサイドの形成を防止することができるという効果が得られる。その結果、ニッケルシリサイドスパイクを防止することができる。  (もっと読む)

(もっと読む)

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

CMOSデバイスのための歪みSiを形成する方法及び構造体

【課題】 チャネルのNFET及びPFETにおいて、それぞれ大きい引張応力及び圧縮応力を生成するように、費用対効果が大きく、簡単化された方法を提供すること。

【解決手段】 n型デバイス及びp型デバイスを含むデバイスの製造方法である。本発明の一態様において、方法は、半導体基板の部分をドープするステップと、半導体基板のドープされた部分の少なくとも一部を除去することによって、該半導体基板内にギャップを形成するステップとを含む。この方法はさらに、半導体基板内のギャップの少なくとも一部に歪み層を成長させるステップをさらに含む。n型デバイスの場合には、歪み層は、少なくともn型デバイスのチャネルのほぼ真下にある部分の上に成長される。p型デバイスの場合には、歪み層は、少なくともp型デバイスのソース領域又はドレイン領域のほぼ真下にあり、p型デバイスのチャネルのほぼ下にはない部分の上に成長される。

(もっと読む)

半導体装置の製造方法

シリコン基板(101)上に、RTO法によりシリコン酸化物からなる下地層(103)を形成する。このとき、下地層(103)の膜厚を1.5nm以上とする。次に、下地層(103)上に、CVD法によりハフニウム窒化物を0.5乃至1.0nmの厚さに堆積させ、金属化合物層(104)とする。次に、水素雰囲気中において熱処理を施し、金属化合物層(104)から下地層(103)中にハフニウム元素を拡散させてシリケート化させ、ゲート絶縁膜(106)を形成する。その後、酸化雰囲気中において熱処理を行う。このとき、シリコン基板(101)とゲート絶縁膜(106)との界面には、ハフニウム元素が到達しないようにする。  (もっと読む)

(もっと読む)

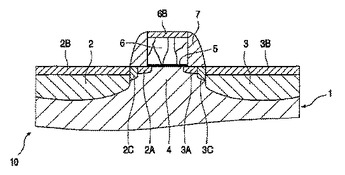

半導体装置とこの種の半導体装置の製造方法

この発明は、基板と半導体本体(1)とを有する半導体装置(10)に関し、半導体本体(1)がソース(2)及びドレイン(3)を有する第一のFET(3)を備え、ソース(2)及びドレイン(3)は、金属シリサイドを含む接続領域(2B,3B)が設けられ、そして、ゲート(6)下部のチャネル領域(4)と境界を成し且つソース(2)及びドレイン(3)より厚みが薄く且つドーピング濃度が低いソース及びドレイン領域拡張部(2A,3A)に接続されている。ソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)とは、第一の導電型で且つ厚み及びドーピング濃度がソース(2)及びドレイン(3)とソース及びドレイン領域拡張部(2A,3A)との間の中間領域(2C,3C)により互いに接続されている。このようにして、接続領域(2B,3B)と基板と間にリーク電流並びに短絡が起きるのが抑制され、一方で、ソース及びドレイン領域拡張部(2A,3A)を用いることの効果が維持される。好ましくは、中間領域(2C,3C)がゲート(6)直近のスペーサ(7)下部に位置し、好ましくは、これらは、なるべく傾けられたイオン注入により形成される。  (もっと読む)

(もっと読む)

シリコン領域に形成されたニッケル/コバルトシリサイド領域を有する半導体デバイス

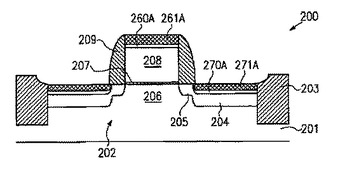

電界効果トランジスタのゲート電極などの、シリコン含有領域に、埋め込まれたニッケルシリサイド層(260A)、続いてコバルトシリサイド層(261A)を形成することによって、縮小されたシリコン回路構造のシート抵抗及び接触抵抗を過度に損なうことなく、デバイスを更に縮小することができるように、両シリサイドの優れた特性が組み合わせられる。  (もっと読む)

(もっと読む)

集積回路のトランジスタにおける金属ゲート構造および形成方法(高性能デバイスの金属置換ゲートのための構造および方法)

【課題】 高性能デバイスの金属置換ゲートのための構造および形成方法を提供する。

【解決手段】 まず、半導体基板(240)上に設けたエッチ・ストップ層(250)上に、犠牲ゲート構造(260)を形成する。犠牲ゲート構造(300)の側壁上に、1対のスペーサ(400)を設ける。次いで、犠牲ゲート構造(300)を除去して、開口(600)を形成する。続けて、スペーサ(400)間の開口(600)内に、タングステン等の金属の第1の層(700)、窒化チタン等の拡散バリア層(800)、およびタングステン等の金属の第2の層(900)を含む金属ゲート(1000)を形成する。

(もっと読む)

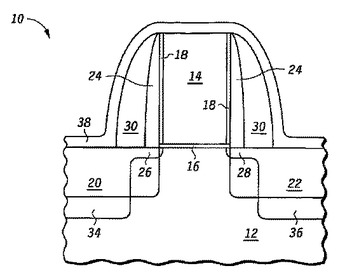

減少されたゲート高さを有するトランジスタを製造する方法

【課題】減少されたゲート高さを有する集積回路トランジスタを形成する方法およびシステムを開示すること。

【解決手段】本方法は、基板、基板の上のゲート導体(13)、およびゲート導体(13)の上の少なくとも1つの犠牲層(14〜16)を有する積層構造を形成する。このプロセスは、積層構造を基板から延びる少なくとも1つのゲート・スタックにパターン形成し、ゲート・スタックに隣接してスペーサ(60)を形成し、ゲート・スタックに隣接してソースおよびドレイン領域(71)を形成するようにスペーサで保護されていない基板の領域にドーピングし、そして、スペーサ(60)および犠牲層(14〜16)を除去する。

(もっと読む)

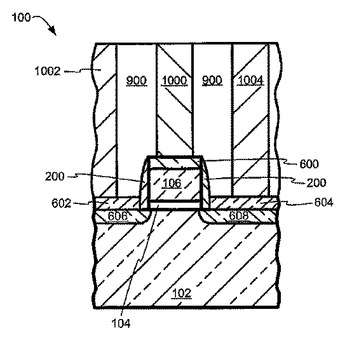

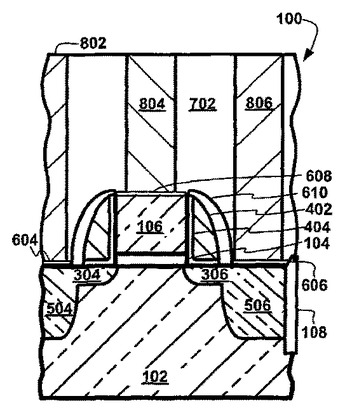

集積回路技術におけるシリサイド化スペーサ

集積回路(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に誘電体層(702)をたい積する。その後、誘電体層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

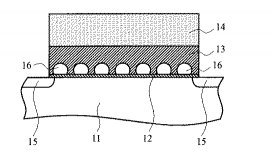

空洞を有するシリコン基板上の高移動度MISFET半導体装置及びその製造方法

MISFETの高性能化を実現する高移動度歪みシリコン構造に、低欠陥かつ低コストで移動度を向上した半導体装置を提供する。MISFETの高性能化を実現する高移動度歪みシリコン構造として、空洞を有するシリコン基板上に、格子緩和シリコン・ゲルマニウム膜/濃度傾斜シリコン・ゲルマニウム膜を形成し、さらにその上に歪みシリコン膜を形成する。これにより、空洞近傍の格子の束縛が緩み、自由度が増すことにより、シリコン・ゲルマニウム膜の薄膜化が実現できるため、低欠陥かつ低コストで移動度を向上した半導体装置を提供できる。 (もっと読む)

バンド設計超格子を有する半導体装置を製作する方法

複数の積層された層群を有する超格子を形成するステップによって、半導体装置を製作する方法である。また当該方法は、前記超格子を通って、前記積層された層群と平行な方向に、電荷キャリアの輸送が生じる領域を形成するステップを有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。前記エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取りこまれた、少なくとも一つの非半導体分子層を有し、前記超格子は、超格子が存在しない場合に比べて、前記平行な方向において大きな電荷キャリア移動度を有する。また前記超格子は、共通のエネルギーバンド構造を有しても良い。

(もっと読む)

(もっと読む)

半導体基板におけるドーパントの拡散を低速化する方法およびこれにより製造されたデバイス

【課題】 ひずみSi/Si1-XGeXデバイス基板において、極めて浅い接合を形成する方法およびそれによって得られる半導体構造を提供する。

【解決手段】 半導体デバイスを形成する方法(およびその結果として得られる構造)は、基板上に、ドーパントおよび少なくとも1つの種を注入するステップと、基板をアニールするステップであって、少なくとも1つの種が、基板のアニールの間のトーパントの拡散を遅らせるステップと、を含む。

(もっと読む)

電界効果トランジスタ及びその製造方法

SiC基板1と、SiC基板1表面に形成されたソース3a及びドレイン3bと、SiC表面に接して形成され厚さが1分子層以上のAlN層5と、その上に形成されたSiO2層とを有する絶縁構造と、この絶縁構造上に形成されたゲート電極15とを有しており、SiCとの間の界面状態を良好に保ちつつ、リーク電流を抑制することができる。 (もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置及びその製造方法

【課題】シリコン基板上のSi1−xGex層を用いた素子構造において、電流駆動能力の高いMISFETを含む半導体装置及びその製造方法を提供することにある。

【解決手段】シリコン基板101上に、Si1−xGex層103を形成し、このSi1−xGex層103にMISFETを形成する。ソース層及びドレイン領域106,107の接合深さを、前記Si1−xGex層103とシリコン層とが接する面を越えないようにする。

(もっと読む)

SiC半導体のイオン注入層及びその製造方法

【課題】 結晶の乱れ及び結晶表面の荒れを低減させたイオン注入層を提供する。

【解決手段】 本発明に係るSiC半導体1のイオン注入層2は、4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっている。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 サブミクロンCMOSトランジスタを、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗などと一緒に、それぞれの特性を劣化させることなく、同一基板上に混載すること。

【解決手段】 半導体基板1の一主面側にパンチスルーストッパー層を形成する際に、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗を形成する領域をマスクしてたとえばイオン注入をおこなう。それによって、サブミクロンCMOSトランジスタの形成領域にパンチスルーストッパー領域4を形成するとともに、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗の形成領域にパンチスルーストッパー領域が形成されるのを防ぐ。

(もっと読む)

1,481 - 1,499 / 1,499

[ Back to top ]