Fターム[5F140CA03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 配線 (1,162) | 材料 (584)

Fターム[5F140CA03]の下位に属するFターム

多結晶 (34)

超電導材料

Fターム[5F140CA03]に分類される特許

121 - 140 / 550

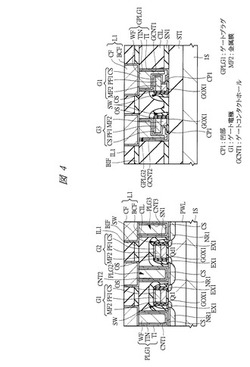

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置の製造方法

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

高耐圧半導体装置及びその製造方法

【課題】高耐圧と低オン抵抗を両立する高耐圧半導体装置及びその製造方法を提供する。

【解決手段】第1導電型であるp型の半導体基板100上に形成された第2導電型であるn型のソース領域200と、半導体基板100の表面領域に高濃度の第2導電型であるn型で形成された高濃度拡散層310を有し、半導体基板100の表面から高深度領域まで形成された第2導電型であるn型の電界緩和層300と、電界緩和層300の領域内においてソース領域200から遠い領域の上層領域に形成されたドレイン領域400と、ドレイン領域400とソース領域200の間で半導体基板100の表面の活性領域に形成されたゲート酸化膜500と、ドレイン領域400とゲート酸化膜500の間の半導体層表面に形成されたLOCOS酸化膜600と、ゲート酸化膜500上からLOCOS酸化膜600上に張り出して形成されたゲート電極510と、を有して構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】同一の半導体基板上に、高性能な低電圧MISFET、高信頼なMONOS型不揮発性メモリおよび高電圧MISFETを形成する。

【解決手段】ロジック回路などに使用される低電圧MISFETの形成領域において、キャップ酸化膜をマスクにすることによってダミーゲート電極上にシリサイドが形成されるのを防ぎ、ダマシンプロセスを用いて低電圧MISFETのゲートをhigh−k膜18およびメタルゲート電極20で形成する際の形成工程を簡略化する。また、ダミーゲート電極除去時のRIEによりダメージを受けたゲート絶縁膜を一旦除去し、新たにゲート酸化膜17を形成することで素子の信頼性を確保する。

(もっと読む)

高耐圧半導体装置及びその製造方法

【課題】チャネルの閾値調整が容易で、オン抵抗の小さい高耐圧半導体装置及びその製造方法を提供する。

【解決手段】第1導電型であるp型の半導体基板100上に形成された第2導電型であるn型のソース領域200と、半導体基板100の表面から所定の深さまで形成された第2導電型であるn型の電界緩和層300と、電界緩和層300の領域内においてソース領域200から遠い領域の上層領域に形成されたドレイン領域400と、ドレイン領域400とソース領域200の間で半導体基板100の表面の活性領域に形成されたゲート酸化膜500と、ゲート酸化膜500の下のチャネル部550の一部に形成される閾値調整用拡散部555と、ドレイン領域400とゲート酸化膜500の間の半導体層表面に形成されたLOCOS酸化膜600と、ゲート酸化膜500上からLOCOS酸化膜600上に張り出して形成されたゲート電極510と、を有して構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

半導体装置の製造方法

【課題】金属ゲート電極/高誘電体ゲート絶縁膜構造のMISトランジスタを有する半導体装置を高性能化する。

【解決手段】シリコン基板1上に、順に、ハフニウムおよび酸素を主体とする高誘電体膜hk1と、第1金属および酸素を主体とし、化学量論的組成よりも多くの第1金属を含むpMIS用キャップ膜Cp1を形成する。その後、シリコン基板1に、第1熱処理と第2熱処理とを順に施す。続いて、pMIS用キャップ膜Cp1上にゲート電極用金属膜EM1を形成し、これらを加工することでpMIS用金属ゲート電極pG1とpMIS用高誘電率ゲート絶縁膜pI1とを形成する。特に、第1熱処理では高誘電体膜hk1中の余剰酸素を除去し、第2熱処理では高誘電体膜hk1中にpMIS用キャップ膜Cp1中の第1金属を拡散させる。第1熱処理は、第2熱処理よりも低い温度で施す。

(もっと読む)

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】同一半導体チップ内に形成されたNチャネルパワーTDMOSトランジスタとPチャネルパワーTDMOSトランジスタの双方のオン電流に対するオン抵抗の低減を図る。

【解決手段】NチャネルパワーTDMOSトランジスタ用トレンチ4の長辺側とPチャネルTDMOSトランジスタ用トレンチ4の長辺側を45°傾けて形成する。これによりNチャネル側のトレンチ4の長辺側の側壁を(100)面とし、Pチャネル側のトレンチ4の長辺側の側壁を(110)面として、Nチャネル側の電流担体である電子及びPチャネル側の電流担体である正孔の移動度を高くする。移動度を高くすることによりチャネル部分の導電率を高める。

(もっと読む)

半導体装置

【課題】

活性領域と素子分離領域を別個の対象として応力を制御し,半導体装置の性能を向上する。

【解決手段】

半導体装置は、p−MOS領域を有する半導体基板と、半導体基板表面部に形成され、p−MOS領域内にp−MOS活性領域を画定する素子分離領域と、p−MOS活性領域を横断して,半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、p−MOSゲート電極構造を覆って、p−MOS活性領域上方に選択的に形成された圧縮応力膜と、p−MOS領域の素子分離領域上方に選択的に形成され,圧縮応力膜の応力を解放している応力解放領域と、を有し、p−MOSチャネル領域にゲート長方向の圧縮応力とゲート幅方向の引張応力を印加する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】微細なトレンチを採用するトレンチDMOSFETにおいて、ドレイン−ソース間の絶縁破壊電圧を高くするため、低濃度のドリフト層の形成領域を如何に確保するかが課題となる。

【解決手段】TNDMOS形成のためのトレンチT1の底部のN型ウエル層2の表面から内部に延在し、P型ボディ層3と接続するN型埋め込みドリフト層5を形成する。次にトレンチT1の両側壁にゲート電極7a、スペーサー8aを重畳して形成する。次に、ゲート電極7a及びスペーサー8aをマスクとしてリン等をイオン注入しN型埋め込みドリフト層5内にN+型ドレイン層11を形成する。これによりN+型ドリフト層11からP型ボディ層3底部まで延在する低濃度のN型埋め込みドリフト層5を確保する。なお、N+型ドレイン層11を形成しないで、トレンチT1の両側壁に、N型埋め込みドリフト層5を共通のドレイン層とする2つのTDMOSを形成しても良い。

(もっと読む)

半導体装置およびその製造方法

【課題】低オン抵抗かつ高耐圧で高速スイッチング可能な半導体装置をキャリアのライフタイムコントロールの為の格子欠陥を形成していない半導体基板で実現する。

【解決手段】P型Siからなる基板1の表面部に形成されたN型不純物層であるリサーフ領域2と、P型不純物層であるベース領域3と、高濃度のN型不純物層であるエミッタ/ソース領域8と、リサーフ領域2内に形成された低濃度のP型不純物層であるコレクタ領域4と、コレクタ領域4に隣接して形成され別断面に位置する高濃度のN型不純物層であるドレイン領域と、高濃度のP型不純物層であるベース接続領域10と、ゲート絶縁膜6と、ゲート電極7とからなる横型ハイブリットIGBTにおいて、コレクタ領域4が別断面に位置するドレイン領域よりも浅く形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】高誘電率ゲート絶縁膜として機能するHf含有絶縁膜4a,4b上にメタルゲート電極であるゲート電極GE1,GE2が形成され、ゲート電極GE1,GE2は、金属膜7a,7b,7cの積層膜からなる金属膜7とその上のシリコン膜8との積層構造を有している。金属膜7の最下層の金属膜7aは、窒化チタン膜、窒化タンタル膜、窒化タングステン膜、炭化チタン膜、炭化タンタル膜または窒化タングステン膜からなり、金属膜7bは、ハフニウム膜、ジルコニウム膜またはアルミニウム膜からなり、金属膜7cは、金属膜7aと同種の材料からなる膜である。

(もっと読む)

半導体装置の製造方法

【課題】比較的低い温度のもとで、良質で、かつ、薄いシリコン酸化膜等を均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】ステップ1では、半導体基板がモノシラン(SiH4)に暴露される。次に、ステップ2では、残存するモノシラン(SiH4)が排気される。そして、ステップ3では、半導体基板が亜酸化窒素プラズマに晒される。ステップ1〜3を1サイクルとして、必要とされる膜厚が得られるまでこのサイクルを繰り返すことで、所望のシリコン酸化膜が形成される。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、極めて高い歩留まりでゲート電極について均一で十分なフル・シリサイド化を確実に実現する。

【解決手段】ゲート電極104a,104b及びソース/ドレイン領域107a,107bのNiシリサイド化を行うに際して、1回目のNiシリサイド化の後に1回目のmsecアニール処理であるフラッシュランプアニール処理を行い、2回目のNiシリサイド化、更には必要であれば2回目のフラッシュランプアニール処理を行って、ソース/ドレイン領域107a,107b上には1回目のフラッシュランプアニール処理で形成されたNiSi層111bを維持した状態で、フル・シリサイドゲート電極115a,115bを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】LDMOSFETを有する半導体装置では、ソース電極が裏面にあることから、表面のソース・コンタクト領域と裏面のソース電極間の電気抵抗を低減するため、上面からP型エピタキシャル層を貫通してP+型基板内に伸びるボロンを高濃度にドープしたポリ・シリコン埋め込みプラグが設けられている。このポリ・シリコン埋め込みプラグの周辺のシリコン単結晶領域に転位が発生しており、これにより、リーク不良が誘発されていることが明らかとなった。

【解決手段】本願発明は、相互に不純物濃度の異なる第1及び第2の半導体層の境界面を貫通するシリコン系プラグを有する半導体装置であって、このプラグの少なくとも内部は多結晶領域であり、この多結晶領域表面の内、先の境界面の両側近傍は、固相エピタキシャル領域で覆われている。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】nチャネル型MISFETQnは、半導体基板1のp型ウエルPWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3aを介して形成されたゲート電極GE1を有し、pチャネル型MISFETQpは、n型ウエルNWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3bを介して形成されたゲート電極GE2を有している。ゲート電極GE1,GE2は、金属膜7とその上のシリコン膜8との積層構造を有している。Hf含有絶縁膜3aは、Hfと希土類元素とSiとOとNとからなる絶縁材料膜またはHfと希土類元素とSiとOとからなる絶縁材料膜であり、Hf含有絶縁膜3bは、HfとAlとOとNとからなる絶縁材料膜またはHfとAlとOとからなる絶縁材料膜である。

(もっと読む)

121 - 140 / 550

[ Back to top ]