Fターム[5F140CA03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 配線 (1,162) | 材料 (584)

Fターム[5F140CA03]の下位に属するFターム

多結晶 (34)

超電導材料

Fターム[5F140CA03]に分類される特許

81 - 100 / 550

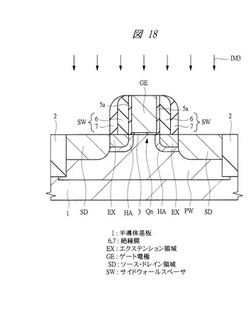

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】イオン注入により半導体基板1にエクステンション領域EXを形成してから、ゲート電極GEの側壁上にサイドウォールスペーサSWを形成し、その後、イオン注入により半導体基板1にソース・ドレイン領域SDを形成する。サイドウォールスペーサSWを形成するには、半導体基板1上にゲート電極GEを覆うように絶縁膜6を形成してから、この絶縁膜6を異方性エッチングし、その後、半導体基板1上にゲート電極GEを覆うように絶縁膜7を形成してから、この絶縁膜7を異方性エッチングすることで、ゲート電極GEの側壁上に残存する絶縁膜6,7からなるサイドウォールスペーサSWを形成する。絶縁膜6のエッチング工程では、絶縁膜6をアンダーエッチングまたはジャストエッチングし、絶縁膜7のエッチング工程では、絶縁膜7をオーバーエッチングする。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電材料のゲートトレンチへの埋め込みが容易な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上の絶縁膜と、絶縁膜に設けられた凹部と、凹部の底部であって半導体基板上に設けられたゲート絶縁膜とを形成する工程と、凹部の内壁面上と絶縁膜の上面上に、第1金属を含む導電材料で第1ゲート電極膜を形成する工程と、第1ゲート電極膜上に、凹部の側面部分の一部は覆わないように、導電材料の融点よりも高い融点を持つ材料でカバー膜を形成する工程と、カバー膜が形成された状態で、熱処理を行って、第1ゲート電極膜をリフローさせる工程とを有する。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】規則的に配列した複数の微細な開口部OPを有するフィルタFLを通過したイオンビーム22をレンズ26で収束して半導体ウエハ1Wに照射することにより、チャネルドープイオン注入を行なう。この際、フィルタFLには、イオンビーム22と同じ極性の電圧を印加する。フィルタFLの開口部OPの中央部に向かって入射した不純物イオンは、そのまま直進して開口部OPを通過することができるが、フィルタFLの開口部OPの中央部以外の領域に向かって入射する不純物イオンは、フィルタFLによる電場によって進行方向が曲げられて、開口部OPを通過することができない。このため、半導体ウエハ1Wに注入された不純物イオンは、規則的な配列を有したものとなり、MISFETのしきい値電圧のばらつきを抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率絶縁膜を含むゲート絶縁膜を備えた電界効果型トランジスタにおいてゲート絶縁膜におけるゲート電極の端部下に位置する部分の厚膜化を試みると、高誘電率絶縁膜が結晶化し、ゲートトンネルリーク電流の発生を抑制出来ない場合があった。

【解決手段】半導体装置では、半導体基板1上にはゲート絶縁膜2が形成され、ゲート絶縁膜2上にはゲート電極3が形成されている。ゲート絶縁膜2では、ゲート絶縁膜2におけるゲート電極3の両端部下に位置する厚膜部分2aの膜厚は、ゲート絶縁膜2におけるゲート電極3の中央部下に位置する中央部分2bの膜厚よりも厚い。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

半導体装置

【課題】半導体装置の大きさを大きくすることなく、増幅率の向上と、高耐圧化を図ることを課題とする。

【解決手段】基板上にドレイン部,ゲート部およびソース部が形成され、ゲート部は、基板上に形成されたゲート絶縁膜と、その上に形成されたゲート電極とからなり、ドレイン部は、ゲート電極の一方の端部に隣接した位置に設け、基板内部の表面近傍に形成された低濃度ドレイン領域と、より表面近傍に形成された中間濃度ドレイン領域と、基板の上の高濃度ドレイン領域とからなり、ソース部は、ゲート電極の他方の端部に隣接した位置に設け、基板内部の表面近傍に形成された低濃度ソース領域と、より表面近傍に形成された中間濃度ソース領域と、基板上の高濃度ソース領域とからなり、高濃度ソース領域は、ゲート電極の上方であって基板表面に平行な方向に延長されたアーム部を備え、アーム部の端部近傍の位置にコンタクト部を有する電極配線部を備える。

(もっと読む)

半導体装置

【課題】シリコン基板裏面をソース電極として使用するLDMOSFETにおいて、出力効率向上のため、基板抵抗を下げようとして高濃度ボロンドープ基板を用いると、ソースドレイン間のリーク不良が、多発することが、本願発明者等によって明らかにされた。更に、この不良解析の結果、ソース不純物ドープ領域からP型エピタキシ層を貫通してP型基板に至るP型ポリシリコンプラグに起因する不所望な応力が、このリーク不良の原因であることが明らかにされた。

【解決手段】本願発明は、LDMOSFETを含む半導体装置であって、LDMOSFETのソース不純物ドープ領域の近傍の上面から下方に向けてエピタキシ層内をシリコン基板の近傍まで延び、前記エピタキシ層内にその下端があるシリコンを主要な成分とする導電プラグを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 LDMOS型トランジスタなどの半導体装置が動作中に生ずる経時的な特性変動を抑制すると共に、高耐圧かつ低オン抵抗が実現される半導体装置およびその製造方法を提供する。

【解決手段】 N型半導体層102に、深さが1μmより小さいP型の第1ドレインオフセット領域103と、深さが第1ドレインオフセット領域103より小さく、不純物濃度が第1ドレインオフセット領域103より大きいP型の第2ドレインオフセット領域105と、第1ドレインオフセット領域103より深いN型のボディ領域106と、N型のソース領域107およびドレイン領域104とを設ける。またLOCOS酸化膜からなる絶縁膜110と、ゲート絶縁膜108を介して形成されたゲート電極109とをN型半導体層102上に備える構造とする。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のコンタクトプラグのゲート電極への短絡を防止する。第1の不純物拡散層と第1のコンタクトプラグの接続抵抗、及び第1と第2のコンタクトプラグの接続抵抗を低減することにより、縦型MOSトランジスタのオン電流を増加させる。

【解決手段】シリコンピラー上部に、非晶質シリコン層及び単結晶シリコン層を形成する。次に、2度の選択エピタキシャル成長法により、シリコンピラー上に順に非晶質シリコン層、及び非晶質シリコンゲルマニウム層を形成する。この後、熱処理により、シリコンピラー上部に単結晶シリコン層を有する第1の不純物拡散層を形成すると同時に、シリコンピラー上に単結晶シリコン層及び多結晶シリコンゲルマニウム層を有する第1のコンタクトプラグを形成する。次に、第1のコンタクトプラグに接続されるように、金属から構成される第2のコンタクトプラグを形成する。

(もっと読む)

半導体装置の製造方法

【課題】工程数が多く、煩雑になる問題を解決する半導体装置の製造方法を提供する。

【解決手段】半導体基板1に第1絶縁膜2を形成し、第1領域Aに第1導電型の第1ウエル層31を形成し、第1領域A以外の第1絶縁膜2上に第1半導体膜3を形成し、第1ウエル層31にトランジスタを形成し、第1半導体膜3及び第1領域Aの第1絶縁膜2の上に、トランジスタのビットコンタクトを兼ねる第2半導体膜7を形成する工程、第2半導体膜7上に、第2領域用B1のマスク8を積層してから、第1または第2導電型ドーパントを注入して第2ウエル層32を形成し、次いで、第2領域B1の少なくとも第2半導体膜7に、ドーパントを注入する工程、第2半導体膜7上に導電膜を積層してから、第1、第2半導体膜3,7及び導電膜を部分的にエッチングして、第1領域Aにトランジスタのビット配線層を、第2領域B1,B2に別の配線層を形成する工程、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】オフトラ型ESD保護素子のESD耐量を増加する。

【解決手段】第2導電型ドレイン高濃度拡散層となる領域にトレンチを備え、トレンチ内に第2導電型の多結晶シリコン膜を埋め込むことで、第2導電型ドレイン高濃度拡散層の実効的な体積を増加することを実現する。これより、ゲート電極からドレインコンタクト孔の距離を大きくしたことと同じ効果が得られ、本発明の半導体装置はオフトラ型ESD保護素子として、素子サイズを変更しなくてもESD耐量の増加が可能となる。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】全反応方式のサリサイドプロセスを用いず、部分反応方式のサリサイドプロセスによりゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の熱処理では、ランプまたはレーザを用いたアニール装置ではなく、カーボンヒータを用いた熱伝導型アニール装置を用いて半導体ウエハを熱処理することにより、少ないサーマルバジェットで精度良く薄い金属シリサイド層41を形成し、最初の熱処理によって金属シリサイド層41内にNiSiの微結晶を形成する。

(もっと読む)

半導体集積回路装置

【課題】ゲート絶縁膜の一部を高誘電体膜で構成した場合に好適な2種ゲート構造を提供する。

【解決手段】基板1上に窒化シリコン膜よりも比誘電率が大きい高誘電体膜、例えば酸化チタン膜6(内部回路のゲート絶縁膜)を堆積した後、酸化チタン膜6の上部に窒化シリコン膜7を堆積する。窒化シリコン膜7は、次の工程で基板1の表面を熱酸化する時に酸化チタン膜6が酸化されるのを防ぐ酸化防止膜として機能する。次に、内部回路領域に窒化シリコン膜7と酸化チタン膜6を残し、I/O回路領域の窒化シリコン膜7と酸化チタン膜6を除去した後、基板1を熱酸化することによって、I/O回路領域の基板1の表面に酸化シリコン膜8(I/O回のゲート絶縁膜)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】工程数の増加を回避し得る半導体装置及びその製造方法を提供する。

【解決手段】低濃度ドレイン領域28hを形成するためのドーパント不純物が導入される所定領域を除く領域に、所定領域から離間するようにチャネルドープ層22dを形成する工程と、半導体基板10上にゲート絶縁膜24を介してゲート電極26dを形成する工程と、ゲート電極の一方の側の半導体基板内に低濃度ソース領域28gを形成し、ゲート電極の他方の側の半導体基板の所定領域に低濃度ドレイン領域28hを形成する工程とを有している。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板10の上にゲート絶縁膜を形成する工程と、ゲート絶縁膜の上にゲート電極14cを形成する工程と、ゲート電極14cの側面にサイドウォール15a、15bを形成する工程と、サイドウォール15a、15bを形成した後に、有機アルカリ溶液又はTMAHをエッチング液として用いて、ゲート電極14cの横の半導体基板10に穴10a、10bを形成する工程と、穴10a、10bにソース/ドレイン材料層18a、18bを形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の低いパワーMOS等の半導体装置を提供する。

【解決手段】ゲート酸化膜を介しゲート電極22を形成するゲート電極形成工程と、ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する工程と、第1の開口部において露出している表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、ゲート電極間よりも狭い第2の開口部31を有する層間絶縁膜30を形成する層間絶縁膜形成工程と、第2の開口部よりも広い第3の開口部を有する第2のレジストパターン32を形成する工程と、第3の開口部33において露出している表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

(もっと読む)

81 - 100 / 550

[ Back to top ]