Fターム[5F152CE04]の内容

Fターム[5F152CE04]に分類される特許

41 - 60 / 298

配線基板およびその製造方法

【課題】製造コストおよび製造時間の低減を図りつつ、高性能な薄膜トランジスタを備えた配線基板およびその製造方法を提供することを目的とする。

【解決手段】 絶縁基板101と、絶縁基板101上の表示画素部DSPに配置され、非晶質の第1半導体層SC1Aと、第1半導層SC1Aの上に積層された微結晶または多結晶の第2半導体層SC1Bとを有する第1薄膜トランジスタTFT1と、絶縁基板101上の駆動回路部DCTに配置され、第2半導体層SC1Bより電子移動度が高い多結晶の第3半導体層SC2を有する第2薄膜トランジスタTFT2と、を備えたことを特徴とする。

(もっと読む)

炭化シリコン膜の製造方法

【課題】エッチングが困難な炭化シリコン膜をエッチングすることなく、一つのチップに炭化シリコンのデバイスとシリコンのデバイスを容易に混載させ、かつ、炭化シリコンのデバイスとシリコンのデバイスが電気的に絶縁された構造とすることが可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上に下地層12を形成する工程と、下地層12上にシリコン膜を形成する工程と、シリコン膜をパターニングするパターニング工程と、パターニング工程の後にシリコン膜を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、炭化シリコン膜13をマスクに用いて、マスクが形成されていない領域の下地層12をエッチングする工程と、を有することを特徴とする。

(もっと読む)

炭化シリコン膜の製造方法

【課題】緻密で均一な膜厚であり、しかも所望の膜厚の炭化シリコン膜を得ることができ、かつ低コストや大口径化が可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上にアモルファスシリコンとポリシリコンとの少なくとも一方を含むシリコン膜14を形成する工程と、シリコン膜14を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、を有することを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】大面積な半導体装置を低コストに提供することを目的の一とする。または、nチャネル型トランジスタ及びpチャネル型トランジスタに最適な結晶面をチャネル形成領域とすることにより、性能向上を図ることを目的の一とする。

【解決手段】絶縁表面上に(211)面から±10°以内の面を上面とする島状の単結晶半導体層を形成し、単結晶半導体層の上面及び側面に接して形成し、且つ絶縁表面上に非単結晶半導体層を形成し、非単結晶半導体層にレーザー光を照射して非単結晶半導体層を溶融し、且つ、単結晶半導体層を種結晶として絶縁表面上に形成された非単結晶半導体層を結晶化して結晶性半導体層を形成し、結晶性半導体層を用いて、nチャネル型トランジスタ及びpチャネル型トランジスタを形成する。

(もっと読む)

部分SOIウェーハの製造方法

【課題】活性層からバルク層に達した孔部で堆積中のアモルファスもしくは多結晶シリコンを単結晶化させる際に埋め込み酸化膜の領域での欠陥発生を抑制させる部分SOIウェーハの製造方法を提供する。

【解決手段】活性層を被う保護膜の一部に形成された窓部を通して、活性層と埋め込み酸化膜との各一部をエッチングして孔部を形成後、孔部にアモルファスシリコンを堆積させる。孔部内のアモルファスシリコンを、単結晶化させる場合に高エネルギ光の照射を行うことでエピタキシャル成長速度を速め、埋め込み酸化膜の領域を通過する際に発生する欠陥密度を抑制できる。

(もっと読む)

SOIウェーハの製造方法

【課題】 容易な方法により低コストで部分SOI構造を有するSOIウェーハを製造する方法等を提供する。

【解決手段】 シリコン単結晶ウェーハの表面に第1絶縁膜を形成する工程、該第1絶縁膜の表面に非単結晶シリコン膜を形成する工程、非単結晶シリコン膜の表面からシリコン単結晶ウェーハの表面まで達する開口部を形成することにより、第1絶縁膜及び非単結晶シリコン膜が部分的に表面上に積層されたシリコン単結晶ウェーハを得る工程、このシリコン単結晶ウェーハに対し水素ガス若しくは不活性ガス又はこれらの混合ガス雰囲気下でRTA処理を行うことにより、非単結晶シリコン膜を開口部のシリコン単結晶ウェーハが露出された部分に接するようにマイグレーションさせ、非単結晶シリコン膜を単結晶化して、第1絶縁膜を埋め込み絶縁膜とする部分SOI構造を形成する工程を含む、部分SOI構造を有するSOIウェーハを製造する方法。

(もっと読む)

混合層の部分的再結晶化によるハイブリッド基板生成方法

【課題】下地基板と、複数の群の異なる隣接エリアから形成された混合層とを含むハイブリッド基板を簡単かつ確実に生成する方法を提案する。

【解決手段】ハイブリッド基板生成方法が

単結晶の第1の基板が、2つの表面部分11および12を得るように分離されるステップと、

表面部分11に沿って延び、第1のエリア13で形成され、かつアモルファス材料の異なる第2のエリアに隣接する混合層を含む仮基板が準備され、これらの第2のエリアが、この第1の基板の自由表面の少なくとも一部を形成するステップと、

少なくともこれらのアモルファスエリア全体の分子接合によって、第1の表面部分と同じ結晶配向の他の表面部分12がこの第1の基板に接合されるステップと、

2つの表面部分の結晶配向にしたがったアモルファスエリアの少なくとも一部の固相再結晶化が第1のエリアに対して選択的に生じ、2つの表面部分が有利には分離されるステップとを含む。

(もっと読む)

貼り合わせウェーハの製造方法

【課題】貼り合わせ基板の活性層用ウェーハの表面に、結晶面が異なる領域を簡単に形成可能な貼り合わせウェーハの製造方法を提供する。

【解決手段】高エネルギ光を、活性層用ウェーハの素材は溶融しないが、吸光係数が高いアモルファスシリコンは溶融する条件で貼り合わせ基板の活性層用ウェーハ側の面に照射し、この窓部内のシリコンを溶融させて固化させる。このとき、アモルファスシリコンを単結晶シリコンに液相エピタキシーにより変質させれば、貼り合わせ基板の活性層用ウェーハの表面に、結晶面が異なる領域を簡単に形成できる。

(もっと読む)

半導体製造方法

【課題】ガラス上に高効率な薄膜多結晶シリコン(Si)太陽電池を実現することを目的とした半導体製造方法。

【解決手段】半導体励起(ダイオード励起)された固体連続波レーザーを利用して(110)と(111)に配向制御した大粒径多結晶シリコン(Si)薄膜をガラス上に形成し、このSi膜を種(シード)結晶として多結晶Si層を直接成長する。

その後、本薄膜に対してSi層が溶融しない条件でエネルギービームを照射してSiの固相成長を行うことを特徴とした太陽電池用半導体製造方法。

(もっと読む)

エピタキシャルシリコンウェーハの製造方法

【課題】エピタキシャル成長時の加熱に伴うスリップが発生せず、ウェーハ表面のボイド欠陥に起因したエピタキシャル膜の表面粗さの低下も解消可能なエピタキシャルシリコンウェーハの製造方法を提供する。

【解決手段】単結晶のシリコンウェーハの表面を研削し、ウェーハ表層に加工変質層を形成後、変質層を高エネルギ光の照射で溶融、固化する。変質層は、単結晶シリコンより吸光係数が高いので、光加熱でウェーハが溶ける前に溶融し、エピタキシャル膜に改質できる。その結果、エピ成長加熱によるスリップが発生せず、ウェーハ表面のボイド欠陥よるエピ膜の表面粗さの低下も解消できる。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】ガラス基板など耐熱温度が低い基板を用いた場合にも、実用に耐えうる単結晶半導体層を備えた半導体基板の製造方法を提供する。

【解決手段】単結晶半導体基板上に酸化膜を形成し、酸化膜を介して半導体基板に加速されたイオンを照射することにより、半導体基板中に脆化領域を形成し、酸化膜を間に挟んで単結晶半導体基板と向かい合うように支持基板を貼り合わせ、単結晶半導体基板を加熱することにより、脆化領域において、単結晶半導体層が貼り合わされた支持基板と単結晶半導体基板の一部とに分離し、支持基板に貼り合わされた単結晶半導体層の表面に対して、基板バイアスを印加して第1のエッチングを行い、単結晶半導体層に対してレーザビームを照射して、単結晶半導体層の少なくとも表面の一部を溶融した後、凝固させ、単結晶半導体層の表面に対して、基板バイアスを印加することなく第2のエッチングを行う。

(もっと読む)

薄膜トランジスタ、その製造方法および表示装置

【課題】大きなオン電流を維持したままオフ電流を低減するとともに、製造が容易なLDD領域を備える薄膜トランジスタを提供する。

【解決手段】平面視において、ドレイン電極171をゲート電極121から所定の距離だけ離して形成することによって、LDD領域165となるオーミックコンタクト層161を水平方向に形成する。この場合、LDD領域165は、ゲート電極121の電位に基づく電界の影響を受けにくくなり、実質的にドレイン電極171の電位に基づく電界による電界集中のみを緩和する。したがって、TFT100は、結晶性シリコン膜からなるチャネル領域141cを形成することにより、大きなオン電流を維持することができると同時に、オフ電流を十分低減することができる。

(もっと読む)

アクティブマトリクス型表示装置用基板、アクティブマトリクス型表示装置およびアクティブマトリクス型表示装置用基板の製造方法

【課題】レーザアニールによって結晶化された半導体膜を補助容量電極として用いたとしても、表示不良を解消、あるいは目立たなくさせることができ、歩留まりを向上させることができる。

【解決手段】各補助容量7の一方の電極をなすように上記複数の画素について共通に形成された直線状の補助容量配線6と、各補助容量7の他方の電極をなすように複数の画素について個別に、かつ補助容量配線6に対向するように形成された補助容量電極13fとを備え、各補助容量電極13fは、補助容量配線6の長手方向と交差する方向にラスタスキャンされる連続発振レーザビーム、あるいは擬似連続発振レーザビームによりレーザアニーリングされることによって多結晶化、あるいは結晶が改質された半導体膜からなる。

(もっと読む)

薄膜の結晶化のためのシステムおよび方法

本開示は、基板表面上で継続的に前進する、長く狭いビーム形状のパルス照射を使用する、薄膜の結晶化のためのシステムおよび方法を説明する。本方法は、結晶化領域の質および性能の変動が減少された結晶化膜を提供する。一態様において、本方法は、第1の走査において、x軸およびy軸を有する膜に、膜のx方向に複数の線状ビームレーザーパルスを継続的に照射して、第1のセットの照射領域を形成することと、該膜を、膜のy方向に、ある距離平行移動することであって、該距離が前記線状ビームの長さ未満である、平行移動することと、第2の走査において、膜の負のx方向に一連の線状ビームレーザーパルスを膜に継続的に照射して、第2のセットの照射領域を形成することと、を含み、第2のセットの照射領域のそれぞれが、第1のセットの照射領域の一部分と重複し、第1のセットおよび第2のセットの照射領域のそれぞれが、冷却時、1つ以上の結晶化領域を形成する。  (もっと読む)

(もっと読む)

プライミングおよび光束によって板状体の層を加熱するための方法および装置

本発明は、少なくとも1つの主光束パルスによって少なくとも局所的に加熱すべき少なくとも1つの層(2)を含み、前記加熱すべき層の前表面に比べて深く位置する少なくとも1つのプライミング領域(4)を含む板状体を、少なくとも局所的に加熱する方法および装置に関し、主光束(7)は、前記加熱すべき層(2)の温度が高温範囲(PHT)にあるときに前記加熱すべき層を加熱することができ、プライミング二次加熱手段(9)は、前記プライミング領域を低温範囲(PBT)内の温度から前記高温範囲(PHT)内の温度まで加熱することができる。  (もっと読む)

(もっと読む)

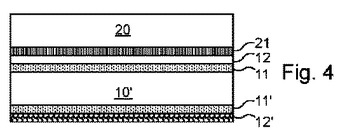

マイクロエレクトロニクス分野において単結晶膜を形成する方法

所定の材料の薄膜を形成する方法は次の工程を含む:表面上に上記所定の材料のアモルファスおよび/または多結晶膜12を有する第1の基板10が準備される;この第1の基板に疎水性直接結合(分子付着)によって、第2の基板20が結合され、上記第2の基板は、その表面上に所定の結晶配向の単結晶参照膜21を有する;少なくとも、アモルファスおよび/または多結晶膜に熱処理が適用され、上記熱処理は、このアモルファスおよび/または多結晶膜12の少なくとも一部に参照膜21の結晶配向に沿って固相再結晶を受けさせるように設計され、この参照膜は再結晶種として機能を果たす;少なくとも部分的に再結晶された膜は、参照膜の少なくとも一部から分離される。  (もっと読む)

(もっと読む)

エピタキシャルシリコンウェーハの製造方法

【課題】エピタキシャル成長時の加熱に伴うスリップが発生せず、ウェーハ表面のボイド欠陥に起因したエピタキシャル膜の表面粗さの低下も解消可能なエピタキシャルシリコンウェーハの製造方法を提供する。

【解決手段】単結晶シリコン製のシリコンウェーハの表面にアモルファスシリコン膜または多結晶シリコン膜を堆積後、この膜を高エネルギ光の照射で溶融、固化し、単結晶シリコンに変質させる。これにより、エピタキシャル膜の液層エピタキシャル成長を可能とし、エピ成長時の加熱に伴うスリップの発生を無くせる。しかも、仮にウェーハ表面にボイド欠陥が存在しても、溶融により、表面の平坦度が高いエピタキシャル膜が得られる。

(もっと読む)

半導体装置の作製方法

【課題】ガラス基板を使用したSOI基板上に形成しても、ゲート電極を形成する導電膜を成膜する際に該導電膜の加える応力により、ガラス基板上の絶縁膜及び半導体膜がはがれないような半導体装置の作製方法の提供を課題の一つとする。

【解決手段】ボンド基板上に第1の絶縁膜を形成し、ボンド基板の表面からイオンを添加することによって脆化層を形成し、ボンド基板を、第1の絶縁膜を介してガラス基板と貼り合わせ、ボンド基板を脆化層において分離してガラス基板上に第1の絶縁膜を介して半導体膜を形成し、第1の絶縁膜及び半導体膜の周辺領域を除去してガラス基板の一部を露出させ、半導体膜、第1の絶縁膜及びガラス基板上に接してゲート絶縁膜を形成し、ゲート絶縁膜上に接して2層構造の積層導電膜を形成し、2層構造の積層導電膜として、上層に引っ張り応力を有する導電膜、下層に圧縮応力を有する導電膜を用いて半導体装置を作製する。

(もっと読む)

SOI基板の作製方法

【課題】半導体膜が分離された後の分離ボンド基板を、SOI基板作製に用いることが可能な再生ボンド基板に再生する際に、分離ボンド基板の研磨工程を削減する方法を提供することを課題の一つとする。

【解決手段】SOI基板の作製工程と分離ボンド基板の再生処理工程からなるサイクルにおいて、エッジロールオフなどで基板周辺部の厚さが中央部より薄いボンド基板を用いてSOI基板を作製し、再生処理工程において低い研磨レートのCMP法による研磨で分離ボンド基板を、基板周辺部に凸部が形成された再生ボンド基板に再生する。凸部の高さは基板の中央部より低いので、再生ボンド基板を再びボンド基板として使用することができる。

(もっと読む)

基板の位置制御方法、および基板の位置制御装置

【課題】温度変化に伴う基板の位置変位に対して、基板上の任意の位置における位置変位を補正する。

【解決手段】基板ステージの各位置における温度変化による膨張や伸縮を位置変位として関数化し、基板上の所定位置での位置変位から、補正対象の位置変位に関わるパラメータ値を求め、このパラメータ値を関数に適用することによって基板上の任意の位置の位置変位を求める。基板ステージの各位置の温度変化による位置変位を、経過時間を変数とする関数で表し、この位置変位の関数をデータテーブルとして備えておき、基板ステージ上に載置される基板の任意の位置における位置変位を求める工程と、求めた位置変位に対応する基板の温度変化の経過時間を関数を用いて求める工程と、経過時間算出工程で求めた経過時間を基板ステージの各位置で定められた関数に代入して補正データを算出する工程とを含む。

(もっと読む)

41 - 60 / 298

[ Back to top ]