Fターム[5F152NN02]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 4族 (1,311)

Fターム[5F152NN02]の下位に属するFターム

Fターム[5F152NN02]に分類される特許

41 - 60 / 64

III族窒化物系半導体、その製造方法、発光素子及び照明装置

【課題】 P型不純物がドープされ活性化されたIII族窒化物系半導体をアニールを必要とせずに容易に製造可能なP型導電性のIII族窒化物系半導体等を提供すること。

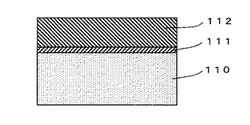

【解決手段】 基板110の一主面上に形成されたIII族窒化物系半導体(P型半導体層112)であり、III族窒化物系半導体に基板110からの不純物が含まれている。これにより、アクセプタ不純物としてのホウ素を、基板110から直接的にIII族窒化物系半導体に混入させることができる。

(もっと読む)

ダイヤモンド種モザイクからの成長ダイヤモンドの分離

本発明は、一実施形態では、合成ダイヤモンド、および複数の種ダイヤモンド上でそうしたダイヤモンドを成長させ、その成長ダイヤモンドにイオンを注入し、複数の種ダイヤモンドから成長ダイヤモンドを分離する方法を提供する。 (もっと読む)

歪み超格子とその上の応力層とを含む半導体デバイス、及びその製造方法

半導体デバイスは、積層された複数の層群を有する歪み超格子層(325)、及び歪み超格子層の上方の応力層を含んでいる。歪み超格子層の各層群は、ベース半導体部分を画成する積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体部分の結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。  (もっと読む)

(もっと読む)

加工基板上へのシリコンCMOS及びAlGaN/GaN広帯域増幅器を集積する新規方法

高速シリコンCMOS回路及び高電力AlGaN/GaN増幅器が、同じウェハー上に集積される。高抵抗シリコンの薄層が、基板上に結合される。ボンディングに続いて、AlGaN/GaN構造を結合したシリコン層上に成長させる。次いで、窒化シリコン又は酸化シリコン層をAlGaN/GaN構造上に堆積させる。これに続いて、シリコンの薄層を窒化シリコン/酸化シリコン層に結合させる。AlGaN/GaN装置の形成領域が規定され、シリコンがこれらの領域から離れてエッチングされる。これに続いて、CMOS装置がシリコン層上に形成され、AlGaN/GaN装置がAlGaN/GaN表面上に形成される。 (もっと読む)

電力用途へのウェハーボンディングを介して得られた多層基板

多層半導体装置は、ウェハーボンディングを介して移行させた単結晶膜の電気的特性を有する多結晶基板の良好な熱的及び電気的特性を利用している。装置構造は、研磨された多結晶、例えば炭化シリコン基板を含む。シリコンの平坦化層が表面に形成され、続いて化学的機械研磨される。次いで、基板は、バルクリシコンウェハー又はsilicon-on-insulator(SOI)ウェハーに結合される。シリコン(SOI)ウェハーは所望厚さに薄肉化される。 (もっと読む)

エピタキシャル基板、半導体素子、エピタキシャル基板の製造方法、およびIII族窒化物結晶における転位偏在化方法

【課題】結晶品質の良好なIII族窒化物結晶の生成に好適なエピタキシャル基板を提供する。

【解決手段】オフ角が与えられてなるサファイア基材の上にIII族窒化物からなる上部層2を形成したうえで、1500℃以上で、好ましくは1650℃以上で加熱処理を施すことにより、上部層2の結晶品質を向上させるとともに該上部層2の表面に数原子層高さよりも大きな繰り返し段差を与えたエピタキシャル基板10を、III族窒化物結晶層3の成長用下地基板として用いる。III族窒化物結晶は段差部分からステップフロー成長するので、上部層2からの貫通転位はこれに伴い屈曲させられ、その後の結晶成長につれて偏在化する。得られるIII族窒化物結晶層3は良好な表面平坦性を有し、かつ、表面近傍の大部分は転移密度が1×107/cm2程度の低転位領域RE2となる。すなわち、エピタキシャル基板10は結晶品質のよいIII族窒化物結晶形成に好適であるといえる。

(もっと読む)

基板上に歪層を製造する方法と層構造

【課題】

ウエーハ接着及び/又はウエーハ研磨なしに基板上に高い品質の歪層を製造する簡単な方法を提供すること。

【解決手段】

この発明は、歪をもたせる層に隣接した層に欠陥領域を形成する工程と、歪をもたせる層に少なくとも隣接した層を緩和させる工程とにより、基板上に歪層を製造する方法に関する。その歪層は別のエピタキシャル層に配置されることができる。そのように形成された層構造は種々の構成要素に好ましく適している。  (もっと読む)

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 単結晶半導体層の結晶品質を向上させつつ、単結晶半導体層を絶縁体上に安価に形成する。

【解決手段】 選択エピタキシャル成長を行うことにより、非晶質半導体層3と接触するように開口部5内に埋め込まれた単結晶半導体層6を形成した後、エッチングガスまたはエッチング液をシリコン酸化膜2、4に接触させることにより、シリコン酸化膜2、4をエッチング除去して、単結晶半導体基板1と非晶質半導体層3との間に空隙7を形成し、単結晶半導体層6を種として非晶質半導体層3の熱処理を行うことにより、非晶質半導体層3が単結晶化された単結晶化半導体層8を形成してから、単結晶半導体基板1と単結晶半導体層8との間の空隙7に埋め込み絶縁層9を形成する。

(もっと読む)

半導体ウエーハの製造方法

【課題】SGOIウエーハを作製する際に、製造装置でのGe汚染の発生を防ぐことができ、さらに貼り合わせ不良による歩留まりの低下を防止することができる半導体ウエーハの製造方法を提供する。

【解決手段】シリコン単結晶ウエーハ表面に傾斜組成Si1−XGeX層、緩和Si1−YGeY層、厚さ5nm未満のシリコン層が順次形成されたボンドウエーハを形成し、シリコン層表面から水素イオンまたは希ガスイオンの少なくとも一種類を注入することにより緩和Si1−YGeY層の内部又は緩和Si1−YGeY層と傾斜組成Si1−XGeX層との界面あるいは傾斜組成Si1−XGeX層の内部にイオン注入層を形成し、シリコン層をエッチング可能な洗浄液によりシリコン層が残存するようにボンドウエーハを洗浄し、洗浄後のボンドウエーハのシリコン層の表面とベースウエーハとを絶縁膜を介してまたは直接密着させ、その後イオン注入層で剥離を行う。

(もっと読む)

電子デバイス用のダイヤモンドベースの基板

本発明は、半導体層又はデバイスを加工するための基板を製造する方法に関するものであり、この方法は、CVDダイヤモンド合成の基板として使用するのに適している少なくとも1つの第1の表面を含むシリコンのウェハを形成する工程と、所定の厚さのCVDダイヤモンドの層を成長させ、成長面をシリコンウェハの第1の表面上に設ける工程と、前記シリコンウェハの厚さを所定のレベルまで薄くする工程と、電子デバイスにおいて使用するのに適している少なくとも1つの半導体層のさらなる合成又は第2の表面自体の上での電子デバイスの合成に適しているシリコンウェハ上に第2の表面を設ける工程とを含み、また本発明は、シリコン表面に密着しているCVDダイヤモンド層からなるGaNデバイス成長に好適な基板に関するものである。  (もっと読む)

(もっと読む)

半導体ウェーハの製造方法

【課題】ミスフィット転位が発生せず、十分な歪みを有し、様々な仕様のデバイス設計に対応できる厚さの歪Si層が形成された半導体ウェーハの製造方法を提供する。

【解決手段】半導体ウェーハの製造方法であって、少なくとも、シリコン単結晶ウェーハの表面に層の堆積温度における臨界膜厚以下のSi1−XGeX層(0<X<1)及び後の緩和熱処理温度における臨界膜厚以下のSi層を順次形成し、前記Si層を通して水素イオン、希ガスイオン、またはSiイオンの少なくとも一種類を注入することにより前記シリコン単結晶ウェーハ内部に緩和用イオン注入層を形成し、その後緩和熱処理を行なうことにより前記Si1−XGeX層を格子緩和させるとともに前記Si層に格子歪を導入して歪Si層を形成した後、前記歪Si層の表面にSiを堆積させて該歪Si層の厚さを増加させることを特徴とする半導体ウェーハの製造方法。

(もっと読む)

構造均一性を有する半導体構造

組成変動を有する半導体層を備えている半導体構造を形成する。この半導体層の最上表面は、実質的にヘイズを有していない。  (もっと読む)

(もっと読む)

ダイヤモンド上の窒化ガリウム発光デバイス

白熱灯および蛍光灯の代用品としての発光ダイオードなどのためにダイヤモンド基板上に窒化ガリウムデバイスを形成する。一つの実施形態として、少なくとも2つの方法でダイヤモンド上に窒化ガリウムダイオード(もしくは他のデバイス)を形成する。第1の方法は、ダイヤモンド上に窒化ガリウムを成長させ、その窒化ガリウム層にデバイスを設けることを含んでいる。第2の方法は、ダイヤモンド上に窒化ガリウム(デバイスもしくはフィルム)を接合し、接合した窒化ガリウム上にデバイスを設けることをともなっている。これらのデバイスは、白熱光や蛍光よりもかなり効率がよく、他の技術よりも光密度もしくはエネルギー密度がかなり高い。同様の方法および同様の構造により他の窒化ガリウム半導体デバイスをつくることができる。 (もっと読む)

ウェハ接合技術を用いて欠陥のない高Ge含有量のSiGeオン・インシュレータ(SGOI)基板を製造する方法

【課題】 低温ウェハ接合技術を用いて、約25原子%より大きい高Ge含有量を有するSiGe層を含むほぼ欠陥のないSGOI基板を達成する方法を提供すること。

【解決手段】 低温ウェハ接合技術を用いて、約25原子%より大きい高Ge含有量を有するSiGe層を含むほぼ欠陥のないSGOI基板を達成する方法が説明される。本出願において説明されるウェハ接合プロセスは、SiGe層と低温酸化物層との間に、Si、Ge及びOの元素を含む接合界面、すなわち界面SiGeO層を形成することができる最初の接合前アニール・ステップを含む。本発明はまた、SGOI基板及びこれを含む構造体も提供する。

(もっと読む)

二枚のウエハを結合する前の熱処理

【課題】有機物や無機物又はガスの気泡が二枚のウエハーの界面に混入しないようにする方法を提供する。

【解決手段】第一のウエハ10から第二のウエハ20への層を転送する方法であって、第一のウエハの表面に、転送すべき層の厚みに近いか、より大きい厚みを有する半導体材料から選ばれた材料の層を確定する脆弱領域を第一のウエハが備え、転送すべき層の厚みに近いか、より大きい厚みを有する層が第二のウエハに接触するように二枚のウエハの表面を接触させる工程と、実質的に大気温度より高く200°Cから400°Cの範囲の第一の温度で約30分より長い第一の時間熱エネルギを供給する工程と、さらなる熱エネルギを供給して温度を第一の温度より高くして脆弱領域において第一のウエハから前記転送すべき層を剥がす工程とを備えたことを特徴とする。

(もっと読む)

イオン注入および熱アニーリングによるシリコンまたはシリコン・オン・インシュレータ基板上の緩和SiGe層

【課題】Siまたはシリコン・オン・インシュレータ(SOI)基板上に、薄い(300nm未満)歪み緩和Si1-xGexバッファ層を形成する方法を提供する。

【解決手段】これらのバッファ層は、歪みを緩和し、著しく平坦な表面を有し、貫通転位(TD)密度が低い、すなわち106cm-2未満である、一様な分布の不整合転位を有する。この手法は、擬似格子整合またはほぼ擬似格子整合したSi1-xGex層すなわち不整合転位が存在しない層を成長させることから開始し、次いでHeまたは他の軽元素を注入し、続いてアニーリングを行って、実質的な歪み緩和を得る。この方法によって機能する極めて有効な歪み緩和機構は、Si/Si1-xGex界面の下に、Si(001)表面に平行な、Heが誘導した小板(泡でない)における転位核化である。  (もっと読む)

(もっと読む)

緩和SiGe層の形成方法

【課題】 緩和SiGe合金層において、積層欠陥およびマイクロツイン等の平面欠陥の形成を抑えるための方法を提供すること。

【解決手段】 平面欠陥密度を低下させた、実質的に緩和したSiGe合金層を製造する方法を開示する。本発明の方法は、Si含有基板の表面上に歪みGe含有層を形成するステップと、Ge含有層/Si含有基板の界面にまたは界面の下にイオンを注入するステップと、加熱を行って、平面欠陥密度が低下した、実質的に緩和したSiGe合金層を形成するステップと、を含む。また、平面欠陥密度が低下したSiGe層を有する実質的に緩和したSiGe−オン−インシュレータおよびこれを含むヘテロ構造も提供する。

(もっと読む)

埋め込みp+シリコン・ゲルマニウム層の陽極酸化による歪みシリコン・オン・インシュレータ

【課題】ウエハ・ボンディングを回避し、歪み半導体オン・インシュレータ(SSOI)基板を製造する、コスト効率がよく製造実施可能な方法と、この方法によって製造されたSSOI基板とを提供する。

【解決手段】本方法は、基板の上にさまざまなエピタキシャル半導体層を成長させる工程であって、半導体層の少なくとも一つはひずみ半導体層の下にあるドープされた緩和半導体層である工程と、ドープされた緩和半導体層を電解陽極酸化プロセスによって多孔質半導体に変換する工程と、酸化して多孔質半導体層を埋め込み酸化物層に変換する工程と、を含む。本方法は、基板の上の緩和半導体層と、緩和半導体層の上の高品質埋め込み酸化物層と、高品質埋め込み酸化物層の上の歪み半導体層と、を備えるSSOI基板を提供する。本発明によれば、緩和半導体層と歪み半導体層とは同一の結晶配向を有する。

(もっと読む)

ダイアモンド基板上炭化珪素並びに関連するデバイス及び方法

ワイドバンドギャップ材料内に、接合温度低下、動作中の高電力密度化、及び定格電力密度における信頼性向上を達成する高電力デバイスを形成する方法を、結果的に得られる半導体構造及びデバイスと共に開示する。本方法は、ダイアモンドの層を炭化珪素ウェハに添加して、得られる複合ウェハの熱伝導率を高め、その後、炭化珪素の上におけるエピタキシャル成長を支持するためにその十分な厚さを保持しつつ、複合ウェハの炭化珪素部分の厚さを削減し、複合ウェハの炭化珪素面を、その上におけるエピタキシャル成長のために、準備し、第III族窒化物ヘテロ構造を、ウェハの準備した炭化珪素面に添加することを含む。  (もっと読む)

(もっと読む)

埋込多孔質シリコン層の酸化によるシリコン・ゲルマニウムオンインシュレータ構造の形成

【課題】Ge含有層の下に生成される多孔質シリコンの層(または領域)を酸化することによりSiGeオンインシュレータを形成する簡単で直接的な方法を提供すること。

【解決手段】この方法は、正孔を多く含む領域が中に形成されたSi含有基板、およびこのSi含有基板の上のGe含有層を備える構造を提供するステップと、この正孔を多く含む領域を多孔質領域に転換するステップと、実質的に緩和したSiGeオンインシュレータ材料を提供するために、この多孔質領域を含む構造をアニールするステップとを含む。

(もっと読む)

41 - 60 / 64

[ Back to top ]