Fターム[5F152NN02]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 4族 (1,311)

Fターム[5F152NN02]の下位に属するFターム

Fターム[5F152NN02]に分類される特許

21 - 40 / 64

低底面転位バルク成長SiCウェハ

【課題】SiCの高品質単結晶ウェハを提供する。

【解決手段】少なくとも直径約3インチ(75mm)と、4°オフ軸のウェハに対して、約500cm−2未満の底面転位密度を有する少なくとも1平方インチ(6.25cm2)の連続した表面領域とを有するSiCウェハであって、その製造方法は、3インチよりわずかに大きい直径を有するSiCブールを形成するステップと、0001平面に対して約2°と12°の間の角度で、該ブールをスライスして、ウェハにするステップであって、該ウェハは、各ウェハ上に、500cm−2未満の底面転位密度を有する少なくとも1平方インチの連続した表面領域を有する、ステップとを包含する。前記方法で背蔵した高品質シリコンカーバイド半導体前駆体ウェハ4は、追加的に、1つ以上の少なくとも一つのIII族窒化物層6を有する。

(もっと読む)

炭化珪素基板、半導体装置、配線基板及び炭化珪素の製造方法

【課題】電子素子等のデバイスを実装するには、炭化珪素基板の高周波損失が大きく、実際には電子素子を炭化珪素基板に実装できなかった。

【解決手段】20GHzにおける高周波損失が2.0dB/mm以下の炭化珪素基板であれば、電子素子を実装して十分に動作させることができることを見出し、2.0dB/mm以上の高周波損失特性を有する炭化珪素基板を2000℃以上で加熱する。この熱処理により20GHzにおける高周波損失を2.0dB/mm以下にすることができた。また、ヒーターに窒素を流さないで、CVDにより炭化珪素基板を作製することによって高周波損失を2.0dB/mm以下にすることができた。

(もっと読む)

半導体装置の製造方法

【課題】性能を確保しながらコストを低減することができる半導体装置の製造方法を提供する。

【解決手段】貫通穴2が形成された基板1上にAlN層3、GaN層4、i−AlGaN層5、n−AlGaN層6及びn−GaN層7を形成する。更に、ソース電極9s、ドレイン電極9d及びゲート電極9gを形成し、半導体素子を形成する。その後、HF溶液中において、貫通穴2に向けて紫外線を照射することにより、AlN層3を基板1から分離する。その後、AlN層3を除去し、GaN層4の裏面に絶縁性の基板を貼り合わせる。

(もっと読む)

表面改質単結晶SiC基板、エピ成長層付き単結晶SiC基板、半導体チップ、単結晶SiC成長用種基板及び単結晶成長層付き多結晶SiC基板の製造方法

【課題】元となる単結晶SiC基板の結晶多形の如何にかかわらず、その表面を4H−SiC単結晶に改質することが可能な気相技術を提供する。

【解決手段】結晶多形が3C、4H、又は6Hの何れかよりなる単結晶SiC基板5を高真空環境において加熱して、当該単結晶SiC基板の表面に炭化層5aを形成させる。次に、炭素ゲッター効果を有する嵌合容器に前記単結晶SiC基板を収容し、前記嵌合容器の内部をシリコンの飽和蒸気圧下かつ高温真空下とし、更に前記嵌合容器の内部圧力が外部圧力よりも高くなる状態を維持しながら加熱することで、前記炭化層5aをシリコンと反応させてアモルファスSiC層5bを生成させる。また、前記嵌合容器に前記単結晶SiC基板を収容した状態で上記と同様の条件で加熱することで、前記犠牲成長層のアモルファスSiCの少なくとも一部を再結晶させて単結晶4H−SiC層5cを生成させる。

(もっと読む)

膜移し変えプロセス

【課題】エピタキシャル成長の表面にできた欠陥を貼りあわせ基板に持ち込まない製造方法を提供する。

【解決手段】表面近傍の域に欠陥を有する第一基板4から、第二材料でできたホスト基板20上に、第一材料の層を移し変えるプロセスであって:a)第一の薄化基板24を形成するために、第一基板を薄化する段階;b)注入面6を形成するために前記第一基板にイオンまたは原子注入し、移し変えるべき層を画定する段階;c)注入面に沿って基板を破断することにより、ホスト基板20上に前記層を移し変える段階;を含むプロセスによって欠陥をなくした貼りあわせ基板を作ることができる。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】放熱性が極めて良好で、かつ、結晶性が良好なGaN系材料を用いたデバイス、および、その製造方法を提供する。

【解決手段】窒化物半導体装置の製造方法であって、シリコン基板60の表面にダイヤモンド層61を気相成長させるステップと、ダイヤモンド層61の表面にSOI基板62を圧着するステップと、SOI基板62を薄層化する薄層化ステップと、薄層化されたSOI基板62上に、GaN層をエピタキシャル成長させるステップと、シリコン基板60を除去するステップと、シリコン基板60より熱伝導率の大きい材料をダイヤモンド層61の裏面に圧着するステップとを含み、SOI基板62は、最表面層621とシリコン酸化層622とを有し、前記薄層化ステップにおいて、選択的にシリコン酸化層622までを除去し最表面層621のみを残してSOI基板62を薄層化する。

(もっと読む)

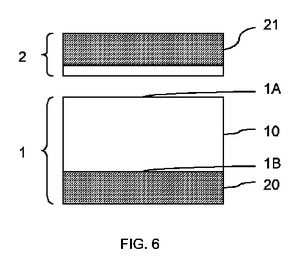

基板とその一方の面上に堆積させた層とを含む構造体の製造方法

本発明は、電子工学、光学、光電子工学または光起電力工学用の、基板(10)と前記基板(10)の一方の面上に材料を堆積させることにより形成された層(20)とを含む構造体(1)の製造方法に関し、この方法は、前記基板(10)の面(1B)が堆積した材料の層(20)により覆われ、前記基板の他の面(1A)が露出している前記構造体(1)を形成するように、−一方で前記基板(10)を、他方で残りの部分を画定する脆化区域を含む脆化された基板を形成する工程、−前記脆化された基板の2つの面のそれぞれの上に前記材料の層を堆積させる工程、−前記脆化された基板をへき開する工程を含むことを特徴とする。  (もっと読む)

(もっと読む)

SiGeオンインシュレータ基板材料

【課題】 向上された緩和、かなり低い欠陥密度、および改善された表面品質を有する

緩和されたSiGeオンインシュレータ基板を形成する方法を提供すること。

【解決手段】 方法が、第1の単結晶Si層の表面上にSiGe合金層を形成するステ

ップを含む。第1の単結晶Si層は、Ge拡散に対する耐性がある下の障壁層との界面を

有する。次に、界面での、または界面付近での機械的な分断を可能にする欠陥を形成する

ことができるイオンが構造内に注入され、その後、注入されたイオンを含む構造に、第1

の単結晶Si層およびSiGe層を通るGeの相互拡散を可能にする加熱ステップを施し

て、障壁層の上に、実質的に緩和された単結晶であり均質のSiGe層を形成する。改善

された性質を有するSiGeオンインシュレータ、およびそれを含むヘテロ構造も提供さ

れる。

(もっと読む)

多結晶シリコン、多結晶シリコン基体およびその製造方法、ならびに多結晶シリコン基体を用いた光電変換素子

【解決手段】窒素ドープされた多結晶シリコンおよび該多結晶シリコンからなる多結晶シリコン基体。好ましくは、赤外吸収スペクトルにおいて、963±5cm-1および/または938±5cm-1の波数位置にピークを有する。ならびに、窒素含有シリコン融液を調製する工程を含む多結晶シリコン基体の製造方法、および上記基体を用いた光電変換素子。

【効果】窒素ドープされた多結晶シリコン基体を用いた光電変換素子は、従来と比較して変換効率が高く、コストパフォーマンスが高い。

(もっと読む)

高性能CMOS技術のための低コストの歪みSOI基板

【課題】エピタキシャル成長及びその後のウェハ接合処理ステップを回避するSSOI構造の製造方法を提供する。

【解決手段】歪み半導体オン・インシュレータ(SSOI)構造体を製造する。SOI基板上に歪み半導体領域を生成するために、歪み記憶技術が用いられる。半導体領域が歪んでいるので、歪み半導体領域上に形成されたトランジスタは、より高いキャリア移動度を有する。(i)薄いアモルファス化層を生成するためのイオン注入と、(ii)アモルファス化層上への高応力膜の堆積と、(iii)アモルファス化層を再結晶させるための熱アニールと、(iV)高応力膜の除去とを含む。再結晶化プロセスの間、SOI基板は応力を受けたので、最終的な半導体層も、応力を受ける。応力の量及び応力の極性(引張又は圧縮)は、高応力膜のタイプ及び厚さによって制御することができる。

(もっと読む)

AlN系III族窒化物単結晶厚膜の作製方法

【課題】結晶品質に優れ、かつクラックのないAlN系III族窒化物単結晶厚膜を作製する方法を提供する。

【解決手段】エピタキシャル基板上に、HVPE法によってAlN系III族窒化物厚膜を得る場合に、通常の成長条件で厚膜層の形成を行う第1の工程と、その時点で形成されている厚膜層を第1の工程における厚膜層の形成温度T1以上の高温状態T2で保持することを主目的とする第2の工程とを適宜のタイミングで切り替えつつ繰り返し行うようにする。これにより、それぞれの第1の工程において厚膜層に内在する歪を第2の工程で逐次に緩和させつつ厚膜層を形成することができる。厚膜層の形成後に面内方向に作用する引張応力を、あらかじめ緩和させた状態の厚膜層を形成することができるので、厚膜層におけるクラックの発生を抑制することができる。

(もっと読む)

多層半導体ウエハ及びその製造方法

本発明は、ハンドルウエハ(5)と、ハンドルウエハ(5)に結合する炭化ケイ素を含む層(40)とを含む多層半導体ウエハの製造方法に関し、前記方法は、a)ハンドルウエハ(5)を提供するステップ;b)ドナーウエハのドナー層(2)と残部(3)とを含み、ドナー層(2)が単結晶シリコンを含むものである、ドナーウエハ(1)を提供するステップ;e)ハンドルウエハ(5)にドナーウエハ(1)のドナー層(2)を結合させるステップ、及びf)ハンドルウエハ(5)に結合したままのドナー層(2)を露出させるためにドナーウエハの残部(3)を除去するステップを含み、前記方法は、更にc)注入炭素を含む層(4)を作製するためにドナー層(2)に炭素イオンを注入するステップ、及びd)ドナー層(2)の少なくとも一部に炭化ケイ素ドナー層(44)を形成するために注入炭素を含む層(4)を含むドナー層(2)を熱処理するステップを含むことを特徴とする。本発明はまた、ハンドルウエハ(5)と、ハンドルウエハ(5)に結合する炭化ケイ素ドナー層(44)とを含む多層半導体ウエハに関し、ここで炭化ケイ素ドナー層(44)は、X線回折によって決定されるように、双晶を含まず、更なる炭化ケイ素ポリタイプを含まない。  (もっと読む)

(もっと読む)

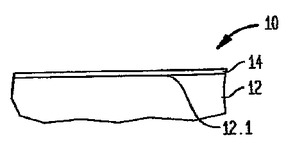

GaN薄膜貼り合わせ基板およびその製造方法、ならびにGaN系半導体デバイスおよびその製造方法

【課題】本発明は、半導体デバイスの製造コストを低減するために、GaNと化学組成の異なる異種基板にGaN薄膜が強固に貼り合わされているGaN薄膜貼り合わせ基板およびその製造方法、ならびに、GaN薄膜上に形成されている少なくとも1層のGaN系半導体層を含むGaN系半導体デバイスおよびその製造方法を提供する。

【解決手段】本GaN薄膜貼り合わせ基板1の製造方法は、GaNバルク結晶10にGaNと化学組成の異なる異種基板20を貼り合わせる工程と、異種基板20との界面から0.1μm以上100μm以下の距離を有する面10tでGaNバルク結晶10を分割して異種基板20上にGaN薄膜10aを形成する工程とを含み、GaNバルク結晶の貼り合わせ面の最大表面粗さRmaxが20μm以下であることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】SBSI法において第1半導体層及び第2半導体層の膜形成の所要時間を短縮で

きるようにした半導体装置の製造方法を提供する。

【解決手段】単結晶の半導体基板1の表面領域2上にアモルファス又は多結晶構造の第1

半導体層11を形成する工程と、第1半導体層11上にアモルファス又は多結晶構造の第

2半導体層12を形成する工程と、第2半導体層12上から半導体基板1の表面領域2に

向けてSi又はArをイオン注入して、半導体基板1の表面領域2と、第1半導体層11

及び第2半導体層12をアモルファス化する工程と、イオン注入によるアモルファス化を

行った後で半導体基板1に熱処理を施して、半導体基板1の表面領域2と、第1半導体層

11及び第2半導体層12を単結晶化する工程と、を含む。

(もっと読む)

AlN系III族窒化物結晶の作製方法およびAlN系III族窒化物厚膜

【課題】比較的簡便な手法によって低転位のAlN系III族窒化物厚膜を得ることができる方法を提供する。

【解決手段】所定の基材上にMOCVD法によってAlN系III族窒化物成長下地層が形成されてなるエピタキシャル基板の上に、HVPE法によってAlN系III族窒化物厚膜をエピタキシャル形成する場合に、MOCVD法における加熱温度よりも高い温度で該エピタキシャル基板を加熱処理した上で、厚膜層の形成を行うようにすることで、厚膜層の低転位化を実現することができる。すなわち、HVPE法を用いた厚膜成長に先立って、加熱処理という比較的簡便な処理を施すだけで、HVPE法による成長に際して特別の構成を有する装置を用いたり、あるいは成長条件に特段の限定を加えたりしなくとも、低転位のAlN系III族窒化物からなる厚膜層を形成することができる。

(もっと読む)

単結晶基板上にエピタキシャル成長したグラフェン層を含むデバイス

電子デバイスは、物質の主表面に単結晶領域を含む物質を含む。単結晶領域は、グラフェンと実質的に格子整合している六方晶格子を有し、グラフェンの少なくとも1つのエピタキシャル層がこの単結晶領域に配置される。現在好ましい実施形態では、単結晶領域は多層の六方晶BNを含む。このような電子デバイスの作製方法は、物質の主表面に単結晶領域を含む物質を提供し、単結晶領域は、グラフェンと実質的に格子整合している六方晶格子を有するステップ(a)と、この領域に少なくとも1つのグラフェン層をエピタキシャル形成するステップ(b)を含む。現在好ましい実施形態では、ステップ(a)は、グラファイトの単結晶基板を提供するステップ(a1)と、基板に多層の単結晶六方晶BNをエピタキシャル形成するステップ(a2)とをさらに含む。六方晶BN層はグラフェンと実質的に格子整合した表面領域を有し、ステップ(b)は六方晶BN層の表面領域に少なくとも1つのグラフェン層をエピタキシャル形成するステップを含む。FETへの応用が説明されている。  (もっと読む)

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】半導体基板に汚染物質が付着することを抑えトランジスタの特性を劣化させることなく製造することができる半導体基板の製造方法及び半導体装置の製造方法を提供する。

【解決手段】半導体基板41の製造方法は、シリコン基板11上におけるSOI素子形成領域13のみに、シリコンバッファ層18及びシリコンゲルマニウム層15が成長する条件でエピタキシャル成長させる。次に、シリコン基板11上の全面にシリコン層16を成長させる。そのあと、シリコンゲルマニウム層15に代えて埋め込み絶縁層31を埋め込む。これにより、引き続く工程において、シリコン基板11上に汚染の原因であるシリコンゲルマニウム層15が残ることを少なくすることができ、処理を行う炉の中にゲルマニウムが広がることを抑えることが可能となる。

(もっと読む)

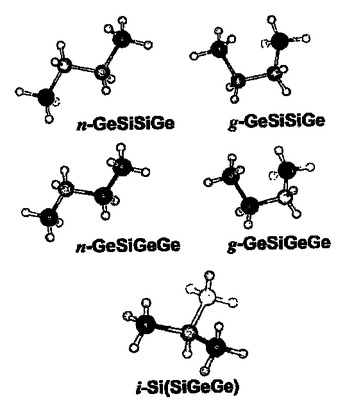

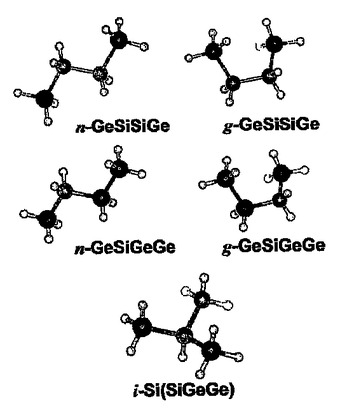

新規な水素化シリコンゲルマニウム、その製造法および使用法

本発明は、水素化シリコンゲルマニウム化合物、それらの合成法、それらの成膜法、およびそれらの化合物を用いて作製された半導体構造を提供する。これらの化合物は、式:SiHn1(GeHn2)yによって定義される。式中、yは2,3または4であり;n1は、0,1,2または3であって原子価を満たし;n2は、化合物中の各Ge原子に関して独立に0,1,2または3であって原子価を満たす。  (もっと読む)

(もっと読む)

新規な水素化シリコンゲルマニウム、その製造法および使用法

本発明は、新規水素化シリコンゲルマニウム化合物、それらの合成法、それらの成膜法、およびそれらの新規化合物を用いて作製された半導体構造を提供する。これらの化合物は、式:(SiHn1)x(GeHn2)yによって定義される。式中、xは2,3または4であり;yは1,2または3であり;x+yは3,4または5であり;n1は、化合物中の各Si原子に関して独立に0,1,2または3であって原子価を満たし;n2は、化合物中の各Ge原子に関して独立に0,1,2または3であって原子価を満たし;但し、yが1のとき、n2は0ではなく;さらに、xが3、かつ、yが1のとき、n2は2または3であり;さらに、xが2、かつ、yが1のとき、n2は3である。  (もっと読む)

(もっと読む)

III族窒化物結晶の形成方法、積層体、およびエピタキシャル基板

【課題】従来よりも結晶品質の優れたIII族窒化物結晶およびその形成方法を提供する。

【解決手段】所定の基材に第1のIII族窒化物結晶を成長下地層2としてエピタキシャル形成してなる下地基板に対して、1250℃以上の所定の温度で熱処理を行う。これにより、成長下地層2の表面には、島状結晶2Iによる三次元的な微細な凹凸形状が形成される。係る下地基板の上に、結晶層4として、第2のIII族窒化物をエピタキシャル形成する。結晶層4と下地基板3との界面には多数の微細な空隙5を介在することになるが、該空隙5の存在により、下地基板3からの転位の伝搬が抑制されるので、結晶層4の転位密度は低下する。結果的に、良好な結晶品質の結晶層4を得ることが出来る。

(もっと読む)

21 - 40 / 64

[ Back to top ]