Fターム[5F152NQ10]の内容

再結晶化技術 (53,633) | 動作層、活性層、素子構成層の材料 (2,604) | 半導体 (2,300) | 2−6族 (68)

Fターム[5F152NQ10]に分類される特許

1 - 20 / 68

半導体ウェハ

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】II族酸化物半導体を用いた半導体素子における新規な絶縁層形成技術を提供する。

【解決手段】半導体素子の製造方法は、(a)基板上方に、II族酸化物半導体層を成長させる工程と、(b)II族酸化物半導体層上に、窒素をドープしつつOリッチ条件での成長を行い抵抗率が105Ωcm以上のII族酸化物絶縁層を成長させる工程とを有する。

(もっと読む)

複合基板の製造方法および複合基板

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成し、転写先基板に接することとなる前記半導体結晶層形成基板の第1表面と、前記第1表面に接することとなる前記転写先基板の第2表面と、が向かい合うように、前記半導体結晶層形成基板と前記転写先基板とを貼り合わせ、前記半導体結晶層形成基板および前記転写先基板の全部または一部をエッチング液に浸漬して前記犠牲層をエッチングし、前記半導体結晶層を前記転写先基板側に残した状態で、前記転写先基板と前記半導体結晶層形成基板とを分離する。ここで、前記転写先基板が、非可撓性基板と有機物層とを有し、前記有機物層の表面が、前記第2表面であるものとする。

(もっと読む)

半導体材料、半導体材料の製造方法及び半導体素子

【課題】pn接合のI−V特性を向上させる半導体材料を提供すること。

【解決手段】本発明に係る半導体材料は、酸化亜鉛の結晶を含有する粒子を備え、酸化亜鉛の結晶子の大きさが5〜50nmであり、酸化亜鉛の結晶における窒素の含有率が500〜10000質量ppmである。

(もっと読む)

複合基体および複合基板

【課題】焼結基体と半導体結晶層とが貼り合わせられた複合基板およびかかる複合基板に好適に用いられる複合基体を提供する。

【解決手段】本複合基体1は、焼結基体10と、焼結基体10上に配置された基体表面平坦化層12と、を含み、基体表面平坦化層12の表面のRMS粗さが10nm以下である。本複合基板は、複合基体1と、複合基体1の基体表面平坦化層12側に配置された半導体結晶層と、を含み、焼結基体10の熱膨張係数と半導体結晶層の熱膨張係数との差が4.5×10-6K-1以下である。

(もっと読む)

半導体ウエハの製造方法、複合基体および複合基板

【課題】半導体デバイスを効率よく製造するために、基体の種類の如何を問わずに効率よく半導体ウエハを製造することができる半導体ウエハの製造方法、ならびにかかる製造方法に好適に用いられる複合基体および複合基板を提供する。

【解決手段】本半導体ウエハの製造方法は、基体10上に、表面のRMS粗さが10nm以下の基体表面平坦化層12を形成して複合基体1を得る工程と、複合基体1の基体表面平坦化層12側に半導体結晶層20aを貼り合わせて複合基板3A,3B,3Cを得る工程と、複合基板3A,3B,3Cの半導体結晶層20a上に少なくとも1層の半導体層30を成長させる工程と、基体表面平坦化層12をウェットエッチングで除去することにより、基体10から半導体結晶層20aを分離して、半導体結晶層20aおよび半導体層30を含む半導体ウエハ5を得る工程と、を含む。

(もっと読む)

半導体ウェハ及びその製造法

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを課題の一とする。

【解決手段】絶縁表面上に膜厚が1nm以上10nm以下の第1の材料膜(六方晶の結晶構造を有する膜)を形成し、第1の材料膜を核として、六方晶の結晶構造を有する第2の材料膜(結晶性酸化物半導体膜)を形成し、第1の材料膜と第2の材料膜の積層を形成する。第1の材料膜としては、ウルツ鉱型結晶構造を有する材料膜(例えば窒化ガリウム、或いは窒化アルミニウム)、或いはコランダム型結晶構造を有する材料膜(α−Al2O3、α−Ga2O3、In2O3、Ti2O3、V2O3、Cr2O3、或いはα−Fe2O3)を用いる。

(もっと読む)

半導体積層体とこれを含むHFETおよびそれらの製造方法

【課題】半導体積層体に含まれるチャネル層下の化合物半導体層を不純物ドーピングでp型化することなく、その半導体積層体を含むHFETのリーク電流の低減や耐電圧の向上などを可能とする。

【解決手段】半導体積層体は、基板(11)上において順次堆積された第1、第2および第3の化合物半導体層(13、14、15)を少なくとも含み、その第1化合物半導体層(13)の少なくとも部分的層(16)は非晶質に改質されており、第2化合物半導体層(14)は第1化合物半導体層(13)に比べて小さなバンドギャップを有して光吸収層として作用し得る。

(もっと読む)

半導体基板、半導体基板の製造方法、および電磁波発生装置

【課題】複数の異なる周波数を出力する半導体基板を提供する。

【解決手段】p型半導体またはn型半導体を含む第1の不純物半導体と、第1の不純物半導体に接する複数の空乏領域を有する空乏化半導体とを備え、複数の空乏領域のそれぞれは、第1の不純物半導体との第1界面と、第1界面と対向する表面とを有し、複数の空乏領域のそれぞれは、第1界面に垂直な方向における第1界面と表面との平均距離および組成の少なくとも一つが異なる半導体基板を提供する。

(もっと読む)

半導体基板及び半導体基板の製造方法

【課題】半導体基板のアライメントマークを繰り返し使用する。

【解決手段】ベース基板にアライメントマークを形成する段階と、アライメントマークを形成する段階の後に、ベース基板上のアライメントマークを含む領域に、結晶成長を阻害する阻害層を形成する段階と、アライメントマークの位置を基準とする開口を形成すべき位置を示す情報に基づいて、阻害層におけるアライメントマークが設けられていない領域に、ベース基板を露出する開口を形成する段階と、開口内に半導体結晶を成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体デバイスおよび半導体構造の製造方法

【課題】 半導体結晶材料の作製またはこの半導体結晶材料を含む構造を提供する。

【解決手段】 第1の半導体結晶材料の表面の粗さは、低減されている。半導体デバイスは、第1の結晶材料の表面上に低欠陥の歪んだ第2の半導体結晶材料を含む。歪んだ第2の半導体結晶材料の表面の粗さは、低減されている。一実施例は、第1および第2の半導体結晶材料間の界面境界の不純物を減少させるプロセスパラメータを作成することによって、粗さが低減された表面を得ることを含む。一実施の形態では、第1の半導体結晶材料は、アスペクト比トラッピング技術を用いて欠陥をトラップするのに十分なアスペクト比を有する絶縁体の開口によって限定されることができる。

(もっと読む)

ナノ/微小球リソグラフィによって製造されるナノ/マイクロワイヤ太陽電池

【課題】 ナノ/微小球リソグラフィによって製造されるナノ/マイクロワイヤ太陽電池を提供する。

【解決手段】 ナノワイヤ/マイクロワイヤ・ベースの太陽電池を製造する技術が提供される。一実施形態において、太陽電池を製造する方法が提供される。本方法は、以下のステップを含む。ドープ基板を準備する。基板の上に球の単層を堆積させる。球は、ナノ球、微小球、又はそれらの組み合わせを含む。球をトリミングして単層内の個々の球の間に空間を設ける。トリミングされた球をマスクとして用いて、基板内にワイヤをパターン形成する。ワイヤは、ナノワイヤ、マイクロワイヤ、又はそれらの組み合わせを含む。ドープ・エミッタ層をパターン形成されたワイヤ上に形成する。上部コンタクト電極をエミッタ層の上に堆積させる。底部コンタクト電極を基板のワイヤとは反対の側に堆積させる。

(もっと読む)

炭化シリコン膜の製造方法

【課題】良好な膜質であり所望の導電型や導電性に制御された炭化シリコン膜を低コストで効率よく製造する方法を提供する。

【解決手段】本発明の炭化シリコン膜の製造方法は、不純物領域を有する炭化シリコン膜の製造方法である。表層にシリコン膜16aを有する基板11のシリコン膜16aを炭化処理して、炭化された膜を含んだ炭化シリコン膜13を形成する工程を有する。不純物領域になる部分のシリコン膜を炭化処理する前に、この部分に不純物を注入する。

(もっと読む)

炭化シリコン膜の製造方法

【課題】緻密で均一な膜厚であり、しかも所望の膜厚の炭化シリコン膜を得ることができ、かつ低コストや大口径化が可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上にアモルファスシリコンとポリシリコンとの少なくとも一方を含むシリコン膜14を形成する工程と、シリコン膜14を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、を有することを特徴とする。

(もっと読む)

炭化シリコン膜の製造方法

【課題】エッチングが困難な炭化シリコン膜をエッチングすることなく、一つのチップに炭化シリコンのデバイスとシリコンのデバイスを容易に混載させ、かつ、炭化シリコンのデバイスとシリコンのデバイスが電気的に絶縁された構造とすることが可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上に下地層12を形成する工程と、下地層12上にシリコン膜を形成する工程と、シリコン膜をパターニングするパターニング工程と、パターニング工程の後にシリコン膜を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、炭化シリコン膜13をマスクに用いて、マスクが形成されていない領域の下地層12をエッチングする工程と、を有することを特徴とする。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】単一半導体基板上にHBTおよびFETのような複数異なる種類のデバイスを形成するに適した半導体基板を製造する方法を提供する。

【解決手段】半導体を結晶成長させる反応容器内に第1不純物原子を構成要素として有する単体または化合物を含む第1不純物ガスを導入する段階を含む複数の段階を繰り返して、複数の半導体基板を製造する方法であって、第1不純物ガスを導入する段階の後に、製造された半導体基板を取り出す段階と、反応容器内に第1半導体を設置する段階と、反応容器内に、第1半導体内で第1不純物原子と反対の伝導型を示す第2不純物原子を構成要素として有する単体または化合物を含む第2不純物ガスを導入する段階と、第1半導体を第2不純物ガスの雰囲気中で加熱する段階と、加熱した前記第1半導体上に第2半導体を結晶成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体装置の作製方法

【課題】外部から局所的に圧力がかかっても破損しにくい半導体装置を提供する。また、

外部からの局所的押圧による非破壊の信頼性が高い半導体装置を歩留まり高く作製する方

法を提供する。

【解決手段】非単結晶半導体層を用いて形成された半導体素子を有する素子層上に、有機

化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体を設け、加熱圧着す

ることにより、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体

及び素子層が固着された半導体装置を作製する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に化合物半導体の結晶成長を阻害する阻害層が設けられ、阻害層はSi結晶層にまで貫通する開口を有し、開口の内部にシード結晶を備え、化合物半導体はシード結晶に格子整合または擬格子整合している半導体基板を提供する。サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられ化合物半導体の結晶成長を阻害する阻害層であって、Si結晶層にまで貫通する開口を有する阻害層と、開口の内部に設けられたシード結晶と、シード結晶に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

3次元集積回路装置及びその製造方法

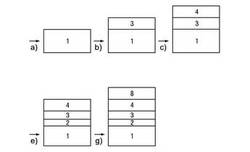

【課題】ガラス基板上に薄膜半導体層を形成した3次元集積回路装置を提供する。

【解決手段】ガラス基板11上に、単結晶もしくは準単結晶の2層の薄膜半導体層13,16が層間絶縁層14を介して積層され、2層の薄膜半導体層13,16は、下層の第1層の薄膜半導体層13と上層の第2層の薄膜半導体層16とが異なる材料であり、2層の薄膜半導体層13,16が、層間絶縁層14に形成された開口内を埋めて形成された、エピタキシャル層15によって接続され、エピタキシャル層15の表面部は、第2層の薄膜半導体層16と同じ材料の層であり、第1層の薄膜半導体層13及び第2層の薄膜半導体層16のうち、1層以上に能動素子Tr21,Tr22が形成されている3次元集積回路装置10を構成する。

(もっと読む)

1 - 20 / 68

[ Back to top ]