Fターム[5H420NA27]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 基準生成部 (1,182) | 基準生成形式 (1,136) | FETを用いるもの (161)

Fターム[5H420NA27]の下位に属するFターム

閾値の異なるFETをミラー接続したもの (45)

閾値の異なるFETを差動接続したもの (6)

Fターム[5H420NA27]に分類される特許

1 - 20 / 110

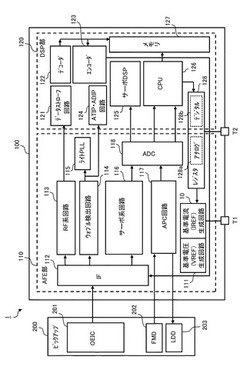

半導体装置、光ディスク装置及び半導体装置のテスト方法

【課題】コストの低減を図りつつ、かつ、精度よく基準電流を生成することが可能な半導体装置、光ディスク装置及び半導体装置のテスト方法を提供する。

【解決手段】半導体装置100は、基準電流を生成する電流生成回路と、記生成された基準電流をテスタ300へ出力する外部端子T1と、基準電流の電流値を制御するための電流制御データを、外部端子T1から出力された基準電流に応じてテスタ300により設定される外部端子T2と、テスタ300により設定された電流制御データにしたがって、電流生成回路により生成される基準電流が所定値となるように調整する電流制御部14と、を備える半導体装置。

(もっと読む)

昇降圧回路、スイッチ回路

【課題】駆動用のMOSトランジスタのオン抵抗が小さく、リーク電流の発生を防ぎ、しかも小型化、低消費電力化に適した昇降圧回路を提供する。

【解決手段】入力電圧IN2が入力される入力端子104、入力電圧IN2に基づいてVCCまたはGNDを出力するMOSトランジスタ201、203、入力電圧IN2に基づいて2VCCまたはGNDを出力するMOSトランジスタ202、204、MOSトランジスタ201、202に一端が接続され、他端がMOSトランジスタ202、204に接続される容量素子206、ソース・ドレイン端子の一方に2VCCが供給され、ソース・ドレイン端子の他方にVCCが供給され、2VCCまたはGNDがゲート端子に供給され、2VCCまたはGNDによってオン、オフされるMOSトランジスタ205と、によって昇圧回路を構成する。

(もっと読む)

バンドギャップ参照電源回路および非接触型デバイス

【課題】バンドギャップ参照電源回路の応答を速くすること。

【解決手段】温度係数が正の絶対温度比例電流を生成する絶対温度比例電流生成回路と、前記絶対温度比例電流のミラー電流を生成するミラー電流生成部と、前記ミラー電流に基づいて生成される温度係数が正の絶対温度比例電圧及び係数が負の相補的電圧から温度係数の絶対値が前記絶対温度比例電圧より小さいバンドギャップ参照電圧を生成するバンドギャップ参照電圧生成部とを有し、前記ミラー電流生成部と前記バンドギャップ参照電圧生成部の間の接続ノードから共通の出力ノードに接続され、当該出力ノードから前記バンドギャップ参照電圧を出力する複数のバンドギャップ参照電圧出力回路とを有し、前記複数のバンドギャップ参照電圧出力回路のうちの一部の回路は、前記ミラー電流生成部と前記接続ノードの間及びバンドギャップ参照電圧生成部と前記接続ノードの間それぞれに設けられた1及び第2のスイッチ回路を有すること。

(もっと読む)

定電流回路及び基準電圧回路

【課題】高温時でもエンハンスメント型Nチャネルトランジスタが弱反転状態で動作できる定電流回路を提供する。

【解決手段】カレントミラー回路と定電流生成ブロック回路とオフリーク回路を備えた定電流回路において、オフリーク回路は、ゲートとソースが接地端子に接続され、ドレインが定電流回路の出力に接続される第一のエンハンスメント型Nチャネルトランジスタで構成される。これにより、定電流を生成するエンハンスメント型Nチャネルトランジスタのゲート−ソース間電圧の上昇を抑えることで、弱反転状態での動作を保つ。

(もっと読む)

基準電圧発生回路

【課題】比較回路の基準値を調整するのに、抵抗成分の異なるMOSのトランジスタを利用することにより、低コストの製造を可能とし、しかも、こうした基準値設定回路やこれを含む制御回路等のワンチップ化を可能にする。

【解決手段】 入力信号の電圧を基準値と比較する比較回路において、所定電圧間に、抵抗成分の合計値が共通する複数のMOSトランジスタを直列接続した組を複数組並列に接続する。MOSトランジスタの各組において、各MOSトランジスタの抵抗成分の比率を変更することにより、各MOSトランジスタの組毎に異なる基準電圧を比較回路に出力する基準値設定回路を設けた。

(もっと読む)

基準信号発生回路

【課題】温度特性の校正に必要なパラメータの可変範囲を小さくすることが可能な基準信号発生回路を提供する。

【解決手段】第1の基準電圧を発生する第1の非線形素子1と、第2の基準電圧を発生する第2の非線形素子2と、出力電圧Voに基づいて第1の非線形素子1および第2の非線形素子2に流れる電流を制御する電流制御回路3と、電流制御回路3の出力電圧Voの温度特性を別個に調整する温度特性調整素子6−1、6−2とを備える。

(もっと読む)

半導体集積回路

【課題】電源の立ち上がりが遅くても安定に動作する半導体集積回路を提供する。

【解決手段】PチャンネルMOSトランジスタMP1のソース電極Sを電源に接続し、そのドレイン電極DにデプレッショントランジスタND1のドレイン電極Dを接続する。さらに、デプレッショントランジスタND1のソース電極Sを、抵抗R1を介して電位VSSとするとともに、PチャンネルMOSトランジスタとデプレッショントランジスタ双方のゲート電極Gを電位VSSとした電源起動回路部11を設ける。そして、PチャンネルMOSトランジスタMP1のドレイン電極DとデプレッショントランジスタND1のドレイン電極Dの相互接続点を定電流回路部12及びスタートアップ回路部14の電源ノードとして、定電流回路部12及びスタートアップ回路部14に動作電源を供給する構成とする。

(もっと読む)

定電圧出力回路

【課題】電源瞬停時に出力ノードの電圧が低電位電源端子の電圧よりも大きく低下することを防止する。

【解決手段】基準電流発生回路10と、該基準電流発生回路10で発生した基準電流を基準電圧に変換して出力ノードN1から出力する電流電圧変換回路20とを備えた定電圧出力回路において、出力ノードN1と低電位電源端子2との間に、アノードが低電位電源端子1に接続されカソードが出力ノードN1に接続されるダイオードD1を接続する。

(もっと読む)

半導体集積回路

【課題】電源回路が発熱により破壊されることを抑制する、電源回路の発熱による破壊を抑制する保護回路を提供する、占有面積の小さい保護回路及び電源回路を得る、作製コストの低い保護回路及び電源回路を得る。

【解決手段】電圧変換回路と、分圧回路及び保護回路を有する制御回路とを有し、保護回路は、温度が上昇するとオフ電流が増大する第1の酸化物半導体トランジスタと、オフ電流を電荷として蓄積する容量素子と、第2の酸化物半導体トランジスタと、非反転入力端子に参照電圧が入力されるオペアンプとを有し、第1の酸化物半導体トランジスタは、電圧変換回路又は制御回路の発熱する素子に隣接して配置される電源回路に関する。

(もっと読む)

内部電源電圧生成回路

【課題】ロジック回路の動作時、貫通電流が、製造ばらつきの影響により過大とならず、消費電流を抑えることが可能な、内部電源電圧生成回路の提供。

【解決手段】内部電源端子の内部電源電圧を生成し、前記内部電源電圧をロジック回路に供給する内部電源電圧生成回路であって、ゲートに与えられる電圧をソースフォロワ出力するトランジスタと、前記ゲートに与えられる電圧をソースフォロワ出力するトランジスタの最大電流を制限する電流制限回路と、を備え、ロジック回路への最大電流、及び消費電流を抑えることが可能な構成とした。

(もっと読む)

内部電源電圧生成回路

【課題】ロジック回路の動作時の貫通電流が、ロジック回路を構成するP型トランジスタとN型トランジスタの閾値電圧ばらつきの影響により過大とならず、消費電流を抑えることが可能な、内部電源電圧生成回路の提供。

【解決手段】内部電源端子の内部電源電圧を生成し、前記内部電源電圧をロジック回路に供給する内部電源電圧生成回路であって、ゲートに与えられる電圧をソースフォロワ出力するトランジスタを有し、内部電源電圧の値が、N型トランジスタの閾値電圧と、P型トランジスタの閾値電圧の絶対値の和に基づいて与えられ、前記N型トランジスタは、前記ロジック回路内部のN型トランジスタと同一の製造プロセスで形成され、前記P型トランジスタは、前記ロジック回路内部のP型トランジスタと同一の製造プロセスで形成される、内部電源電圧生成回路、とした。

(もっと読む)

定電圧回路

【課題】安定起動と低消費電力とを両立させた定電圧回路を提供すること。

【解決手段】バイポーラトランジスタのバンドギャップ電圧を利用して基準電圧を生成する第1の基準電圧発生部(2)と、電界効果トランジスタを用いて基準電圧を生成する第2の基準電圧発生部(3)と、第1の基準電圧発生部(2)の出力電圧、または第2の基準電圧発生部(3)の出力電圧のいずれかを参照して定電圧を生成する定電圧生成部(4)と、第1の基準電圧発生部(2)、第2の基準電圧発生部(3)、および定電圧生成部(4)を制御する制御部(5)と、を備え、起動初期期間において第1の基準電圧発生部(2)と第2の基準電圧発生部(3)とを動作させ、その後の動作期間において第1の基準電圧発生部(2)を停止させることを特徴とする。

(もっと読む)

電圧調整回路機構および関連する動作方法

【課題】従来技術の低ドロップアウト電圧調整器が所望の調整電圧を正確に維持する能力は、減少してしまう。

【解決手段】電圧調整回路の装置および関連される動作方法が提供された。例示的電圧調整回路は電圧調整構成を含み、該電圧調整構成は、入力電圧基準に基づく調整された出力電圧と、電圧調整構成の位相マージンとを増加するように構成され、電圧調整構成に接続された位相補償構成、位相補償構成に接続された検出回路を備えられる。検出回路は、閾値を満たさない出力電流を検出することに応答して、位相補償構成を無効化するように構成される。

(もっと読む)

スタートアップ回路及び基準電圧発生回路

【課題】リーク電流の増大を抑制等しつつ、コア面積が小さいスタートアップ回路を提供すること。

【解決手段】本発明にかかるスタートアップ回路は、基準電圧Voutを発生する基準電圧発生部20に対して電源電圧供給開始時にスタートアップ電流Isrtupを供給し、基準電圧Voutを安定化させるスタートアップ回路10であって、基準電圧Voutを検出し、検出結果に応じた制御電圧Vstを出力するモニタ回路13と、電源電圧VDDに応じた電圧レベルの中間電圧Vnを生成し出力するレベルシフタ11と、中間電圧Vnに応じたスタートアップ電流Isrtupを、基準電圧発生部20に対して供給するか否かを制御電圧Vstに基づいて制御するスイッチ回路12と、を備える。

(もっと読む)

基準電位生成装置

【課題】 安定した基準電位を供給し得る基準電位生成装置を提案する。

【解決手段】 基準電位生成装置1は、基準とすべき位置の周りに回転対称に配されるm個(mは4以上の偶数)の電極21A〜21Dと、基準とすべき位置を含む近傍範囲での強度が所定値未満となる電荷を、m個の電極21A〜21Dに印加する印加手段と、当該範囲に配される複数の導体31A、31Bと、複数の導体31A、31Bから得られる信号の差分を増幅する増幅手段33とを備える。

(もっと読む)

電流源回路

【課題】回路面積が小さな電流源回路を提供する。

【解決手段】この電流源回路では、直流電圧V1に応じた値の参照電流I1を生成し、その電流I1のうちの電流IrをダイオードD1に流し、残りの電流I1−IrをダイオードD2に流し、ダイオードD1,D2のアノードの電圧VR1,VR2を差動増幅回路のトランジスタQ1,Q2のベースに与える。また、直流電圧V2に応じた値の参照電流I2を生成し、その電流I2を差動増幅回路の駆動電流とする。トランジスタQ1のコレクタに流れる定電流Io=Ir・(V2/V1)が電流源回路の出力電流Ioとなる。したがって、外付け用の端子および外部抵抗器が不要となる。

(もっと読む)

定電流回路及び基準電圧回路

【課題】スタートアップ回路を必要とせず、入力安定度の良い定電流回路及び基準電圧回路を提供する。

【解決手段】定電流回路は、定電流生成ブロック回路112と、差動増幅回路111と、デプレッション型NMOSトランジスタ13及び14で構成され、差動増幅回路111は、出力端子をデプレッション型NMOSトランジスタ13及び14のゲート端子に接続され、反転入力端子をデプレッション型NMOSトランジスタ13のソース端子と定電流生成ブロック回路112に接続され、非反転入力端子をデプレッション型NMOSトランジスタ14のソース端子と定電流生成ブロック回路112に接続される。定電流源ブロック回路112は、ゲート端子同士を接続したエンハンスメント型NMOSトランジスタ11及び12と、抵抗15を備えている。デプレッション型NMOSトランジスタ14のソース端子が定電流回路の定電流出力端子102に接続される。

(もっと読む)

基準電圧発生回路

【課題】大きな抵抗を使わずに消費電力の少ない基準電圧を発生する。

【解決手段】PチャネルトランジスタM3のドレイン電流をI1とし、PチャネルトランジスタM4のドレイン電流をI2とすると、接合D1に生ずる電圧VD1と接合D2に生ずる電圧VD2の関係はVD1−VD2=(k×T÷q)×ln(10×I1÷I2)となり、絶対温度Tに比例する電圧が得られる。Nチャネルトランジスタ差動対M6及びM7と、Pチャネルトランジスタの能動負荷M1及びM2なる差動アンプで、負帰還をかけることにより、PチャネルトランジスタM10のゲート・バックゲート間電圧がVD1−VD2と等しくなる。PチャネルトランジスタM4とM5の電流を等しく設定すると、PチャネルトランジスタM11〜M20のそれぞれのゲート・バックゲート間の電圧はPチャネルトランジスタM10と等しくなり、Voutは温度係数がほぼゼロの基準電圧となる。

(もっと読む)

特にナノアンペアオーダーの電流を生じる電流発生器、およびそのような発生器を用いる電圧調整器

【課題】特にナノアンペアオーダーの電流を生じる電流発生器、およびそのような発生器を用いる電圧調整器を提供する。

【解決手段】電圧調整器は、電流ミラーとして接続されていて、電源Vddに接続可能な3個のトランジスタP1、P2、P3の第1組41と、電流ミラーとして接続された2個のトランジスタN1、N2の第2組であって、各トランジスタが第1組のトランジスタに直列に接続されているトランジスタの第2組とを含み、第2組の第1トランジスタN1が、第1組の最後のトランジスタP3に直列に接続されたトランジスタN4に電流ミラーとして接続されたトランジスタN3Rに直列に接続されている。トランジスタN3Rは自身の線形領域で動作し、発生される電流の値は当該トランジスタの等価抵抗に依存し、2個のトランジスタが超長チャネルを有することにより比率L/Wが極めて大きい。

(もっと読む)

基準電流源回路

【課題】従来技術に比較して、回路面積を削減し、出力電流の温度特性が室温においてゼロになるように制御することができる基準電流源回路を提供する。

【解決手段】基準電流源回路1において、追加バイアス電圧生成回路10は、出力電流IREFが温度変化に対して一定となるように追加バイアス電圧VSRを生成する。ドレインバイアス電圧生成回路DB1は、サブスレッショルド飽和領域で動作するnMOSトランジスタMN21及びMN22を備え、ドレインバイアス電圧を生成し、当該ドレインバイアス電圧に追加バイアス電圧VSRに加算して、加算結果の電圧をMOS抵抗MRのドレインに印加する。

(もっと読む)

1 - 20 / 110

[ Back to top ]