Fターム[5H740MM12]の内容

電力変換一般 (12,896) | 保護 (1,231) | 電流に関する検出、保護 (427) | 突入電流、過電流の抑制 (175)

Fターム[5H740MM12]の下位に属するFターム

タイマによるもの (8)

出力に応答するもの (16)

非線形素子によるもの (3)

リアクタンスによるもの (6)

Fターム[5H740MM12]に分類される特許

1 - 20 / 142

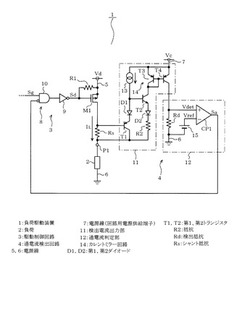

過電流検出回路および負荷駆動装置

【課題】回路用電源電圧としてむやみに高い電圧を用いることなく、シャント抵抗の低電位側端子の電圧がグランド電位付近となる異常が原因で生じる過電流を検出する。

【解決手段】検出電流出力部11は、シャント抵抗Rsの各端子電圧を入力し、その入力した電圧から負荷2に流れる電流に応じた検出電流を出力する。過電流判定部12は、検出電流に基づいて負荷2に過電流が流れているか否かを判定する。検出電流出力部11において、通常時に駆動用電源電圧Vdに近い電圧が印加される部分と、回路用電源電圧Vcに近い電圧が印加される部分との間の経路に第1ダイオードD1および第2ダイオードD2を逆方向に介在させることにより、第1トランジスタT1および第2トランジスタT2がブレークダウンして電流が流れることを阻止する。

(もっと読む)

電力変換装置

【課題】スイッチング素子のゲート電圧閾値が変動しても、スイッチング素子が十分な放電能力を発揮できる、電力変換装置を提供すること。

【解決手段】ハイサイドのスイッチング素子Q1とローサイドのスイッチング素子Q2が直列に接続された直列回路11を備え、スイッチング素子Q1,Q2が両サイドとも重複してオンすることで、直列回路11に接続されるコンデンサ12を放電させる電力変換装置であって、スイッチング素子Q1、Q2に所定の電流値が流れるゲート電圧を測定し、コンデンサ12を放電させるとき、測定したゲート電圧測定値にスイッチング素子Q1のゲート電圧を制御する制御部とを備えることを特徴とするもの。

(もっと読む)

電力変換装置

【課題】指令制御装置の出力した駆動指令信号に関連する回路が誤動作した場合でもアーム短絡を抑止でき、かつ誤動作したことを検知する電力変換回路を提供する。

【解決手段】直列接続された第1、第2スイッチング素子と、前記スイッチング素子を駆動制御する第1、第2駆動制御装置と、駆動制御装置に指令を与える指令制御装置からなる電力変換装置であって、前記駆動制御装置は、指令制御装置の指令信号と他の駆動制御装置の出力するインターロック信号を演算する駆動回路と、スイッチング素子の導通状態を判定する状態判定回路と、指令信号と他の駆動制御装置のインターロック信号と状態判定回路の出力の少なくとも1つを入力するインターロック信号生成回路と、前記指令信号とインターロック信号と状態判定回路の出力の少なくとも2つを入力するフィードバック信号生成回路とを備え、フィードバック信号生成回路の出力を指令制御装置に供給する。

(もっと読む)

トランジスタ保護回路

【課題】スイッチング周波数が高くても、適切にトランジスタの保護を行うことが可能なトランジスタ保護回路を提供する。

【解決手段】本発明の一実施形態に係るトランジスタ保護回路10は、駆動回路30によって電源40の高電位側電圧または低電位側電圧がゲート端子に印加されて、スイッチング制御される電圧駆動型のトランジスタ20の保護を行うためのトランジスタ保護回路である。このトランジスタ保護回路10は、トランジスタ20の保護を実行する保護指令を受けたときに、電源40の高電位側電圧を次第に低下させる電源制御部12を備える。

(もっと読む)

半導体電力変換装置

【課題】本発明の目的は、突入電流抑制回路のバイパス手段(サイリスタ)の制御線から商用電源側へ流出するノイズを抑制することが可能な半導体電力変換装置を提供することである。

【解決手段】本発明では、整流回路4と、整流回路4からの入力を平滑化する平滑コンデンサ5と、半導体素子6aのスイッチングにより平滑コンデンサ5の電圧を変換する電力変換回路6と、整流回路4と平滑コンデンサ5との間に配置されている突入電流抑制回路7とを備えている半導体電力変換装置1において、バイパス手段7bの切替動作を制御する制御線V,Wに配置され、バイパス手段7bの制御線V,Wから商用電源2側へ伝播するノイズを低減させるように構成された第1のノイズフィルタ回路11と、突入電流抑制回路7と前記平滑コンデンサ5との間に配置され、電力変換回路6から商用電源2側へ伝播するノイズを低減させるように構成された第2のノイズフィルタ回路12とを備えている半導体電力変換装置1が提供される。

(もっと読む)

電子装置

【課題】スイッチング素子をオフするように制御しているにもかかわらず、オフできない異常状態を検出し、スイッチング素子の熱破壊を防止することができる電子装置を提供する。

【解決手段】IGBT110dに流れる電流が電流閾値より大きくなると、電流検出回路125は、IGBT110dに電流が流れていると判断する。制御回路128は、駆動信号がIGBT110dのオフを指示しているにもかかわらず、電流検出回路125がIGBT110dに電流が流れていると判断すると、IGBT110dをオフできない異常状態にあると判断する。そして、オフ保持用FET123aをオンする。その結果、IGBT110dのゲートから電荷が放電され、IGBT110dがオフする。そのため、駆動信号がIGBT110dのオフを指示しているにもかかわらず、IGBT110dをオフできない異常状態を検出し、IGBT110dの熱破壊を防止できる。

(もっと読む)

スイッチングデバイスの制御装置

【課題】スイッチングデバイスが過電流の状態ではないが、過電流からの保護に先立ち、スイッチングデバイスの遮断時のサージ電圧を抑制するようにする。

【解決手段】本発明は、電流センサ10と、コンパレータ501と、タイマラッチ502と、制御回路80と、トランジスタ95とを備える。電流センサ10は、スイッチングデバイスQ1の電流を検出し、これに応じた検出電圧ESを出力する。コンパレータ501は、検出電圧ESが基準電圧ER1以上のときに信号を出力する。タイマラッチ502は、その出力信号の継続時間が設定時間以上の場合に、サージ抑制検出信号S3を出力する。制御回路80は、そのサージ抑制検出信号S3を基に、スイッチングデバイスQ1をターンオフさせる駆動信号S12を、トランジスタ95に出力する。基準電圧ER1は、スイッチングデバイスQ1に流れる過電流検出時の基準電圧ER2よりも小さい。

(もっと読む)

電流検出回路、およびモータ制御装置

【課題】プリント配線基板上に搭載されるFETに流れる電流を、FETオン時のオン抵抗Ronと配線パターン抵抗Rpによる電圧降下VDGを基に検出する際に、配線パターンの抵抗Rpにより発生する電圧降下分(オフセット分)をキャンセルして、FET(Qo)のドレイン・ソース間電圧VDSを検出する。

【解決手段】本発明の電流検出回路1は、FET(Qo)のドレイン端子Dと回路グランドGとの間に、第1の抵抗Rdと第2の抵抗Roの抵抗直列回路を接続する。そして、第2の抵抗Ronと第1の抵抗Rdの抵抗値の比(Ro/Rd)が、FET(Qo)のオン抵抗Ronと配線パターンRpの抵抗値の比(Ron/Rp)に一致するように設定する。そして、この第1の抵抗Rdと第2の抵抗Roとの接続点(ノードN1)と回路グランドGとの間の電圧VRoを、FET(Qo)に流れる電流の検出信号として出力する。

(もっと読む)

電源スイッチ保護回路及び車載機器

【課題】過電流から電源スイッチ回路を適切に保護する技術を提供する。

【解決手段】電源スイッチ保護回路は、電源スイッチ回路と、第1回路素子及び第2回路素子の両方がオン状態を示す場合に電源スイッチ回路をオン状態とし、第1回路素子及び第2回路素子の少なくとも一方がオフ状態を示す場合に電源スイッチ回路をオフ状態とする電源スイッチ制御回路と、電源スイッチ回路の出力側の短絡を検出し、短絡が検出されているか否かを示しかつ第1回路素子のオフ状態及びオン状態を切り換えるための短絡検出信号を出力する短絡検出回路と、所定時間内における短絡検出信号の状態変化に応じて、短絡が発生しているか否かを判定し、短絡が発生していると判定すると、第2回路素子がオフ状態を維持するように電源スイッチ制御回路を制御する制御部と、を備える。

(もっと読む)

ゲート駆動回路、電力変換回路、3相インバータ、及びゲート駆動方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】ハイサイドトランジスタ21とローサイドトランジスタ22の少なくとも一方は、ノーマリオン型トランジスタである。2つのゲート駆動回路11、12の少なくとも一方は、正電源から供給される第1電源電圧VDDと、負電圧源30から供給され接地電圧GNDよりも低い第2電源電圧VNEGとに応じた駆動電圧GH、GLを、ノーマリオン型のトランジスタのゲートに出力する。制御回路40は、第2電源電圧VNEGが参照電圧Vrefよりも高い場合、ハイサイドトランジスタ21に流れるドレイン電流を遮断する。

(もっと読む)

電流制限回路

【課題】ノイズ耐性が高く、且つ、製造プロセス、電源、及び電源電圧が変動するような場合においても精度が高い、出力トランジスタに対する電流制限回路を提供する。

【解決手段】電流制限回路が、基準トランジスタと、基準トランジスタに所定の電流を流す電流源と、出力トランジスタがオンした時の両端の第1の電位差と基準トランジスタの両端の第2の電位差を比較する比較器であって、第1の電位差が第2の電位差よりも大きくなった場合に、出力トランジスタをオフするように制御する電流制限信号を出力する、比較器とを備える。基準トランジスタは、出力トランジスタとは素子サイズの異なる同型のトランジスタであり、基準トランジスタがオンした時のオン抵抗は、出力トランジスタがオンした時のオン抵抗の1/Nの大きさ(Nは1より大きい数)であり、更に、基準トランジスタがオンするように基準トランジスタのゲートにバイアスがかけられている。

(もっと読む)

スイッチング素子用ゲート駆動装置

【課題】同時オン防止回路を有し、かつ3レベル電力変換装置の構成部品を少なくし信頼性を向上した3レベル電力変換装置のゲート駆動装置を提供する。

【解決手段】3レベル電力変換装置は、一対の直流電源端子間に順次直列に接続された第一ないし第四の半導体スイッチング素子4〜7をそれぞれ、第一ないし第四のゲート駆動回路28〜31により駆動し、第一及び第二の半導体スイッチング素子4、5のみをオンしたときプラス出力、第二及び第三の半導体スイッチング素子5、6のみをオンしたとき零出力、そして、第三及び第四の半導体スイッチング素子6、7のみをオンしたときマイナス出力を出力する。その際、第一の駆動回路28と第三の駆動回路29、第二の駆動回路30と第四の駆動回路31をそれぞれ同一の基板に実装し、各基板上において、通信線を介して相互に論理回路に接続し、いずれか一方のゲート駆動回路がオンしている時に他方のゲート駆動回路をオフする。

(もっと読む)

電源回路

【課題】過電流や発熱の発生を未然に回避するという電源回路の保護動作を、CPUを利用したソフトウェア制御によることなく行えるようにする。

【解決手段】電流検出部243は、負荷電流に対応する検出電流Idtが閾値Th以上となるのに応じて電力供給を停止させる。準異常状態判定部244は、電源電圧を定常的に供給すべき機能部に対応する定電圧回路から電源電圧の出力が停止している状態、または、バッテリ電圧の異常に応じてCPUにリセットを指示するリセット信号が出力されている状態が発生している場合に準異常状態が発生していると判定する。レベル設定部250は、上記判定に応じて、検出電流Idtに対する閾値Thのレベルが相対的に低くなるように設定を行う。

(もっと読む)

電力変換装置

【課題】両極性ブートストラップ回路のキャパシタ充電を短絡電流が流れることがなく安全かつ確実に実施できる電力変換装置を提供する。

【解決手段】各レグ2〜4を構成する上下の各アームのスイッチング素子SuH、SuL、・・・に対しオン/オフ駆動用の正負両極の電圧を印加するアーム駆動回路DRuH、DRuL、・・・を個別に設け、直流電源Vg1〜Vg3からの電力により正負の各電圧を充電する各キャパシタC1u、C2u、・・・を上下の各アームに設け、かつ各レグ2〜4に両極性ブートストラップ回路5〜7を配置し、キャパシタ充電制御を行う制御回路8は、多相交流電源1の各相の電圧の中で最も高い電圧が入力されているレグの上段アーム側のスイッチング素子と、最も低い電圧が入力されているレグの下段アーム側のスイッチング素子のみをオンする制御信号を各相の電圧変化に応じて繰り返し出力する。

(もっと読む)

半導体装置の短絡保護装置

【課題】半導体素子、特にIGBTの特性の違いや温度変化があっても、最適なパラメータを自動的に設定することのできる半導体装置の短絡保護装置を提供する。

【解決手段】IGBTのゲート電荷QGに対応する電圧VQGを検出する電荷検出手段22と、IGBTの定格動作時の入力部の電荷から負荷短絡が発生したかどうかを判断するための基準電圧VREFを発生する基準電圧発生手段25と、電荷検出手段22で検出された電圧VQGがIGBTの定格動作時の電荷に対応する電圧か、あるいは負荷短絡時の電荷に対応する電圧かを判断する判断手段27と、判断手段27が短絡状態を検出したときにIGBTを動作停止する信号を出力するゲート駆動手段21とを持つ半導体装置の短絡保護装置において、基準電圧発生手段25に、IGBTの定格動作時の入力部の電荷に対応するゲート電荷電圧VQGのハイレベルで安定した電圧VPEAKを検出して記憶する記憶手段26を設ける。

(もっと読む)

過電流保護電源装置

【課題】直流電源17からスイッチ用のFET18を経て負荷16へ電力を供給する電源装置においては、2種類の保護回路が設けられていた。第1は、該FETの温度を検出し、所定温度に達したら該FETをオフする回路である。第2は、デッドショート時のような大過電流が流れた場合には、電流を所定電流に制限する電流制限回路である。保護回路を2種類設けると、部品コストが大になっていた。

【解決手段】比較基準電圧生成回路40を電流供給部41と比較基準電圧発生抵抗部46とで構成し、比較基準電圧VX を生成する。過電流検出電圧生成回路50を電流供給部51と過電流検出抵抗部54とで構成し、FET18の電圧VDSが増大すると減少する電流検出電圧VY を生成する。電圧VDSの増大を検出してFET18をオフすれば、過電流保護も過熱保護も可能となる。

(もっと読む)

直流電源装置

【課題】ワイドバンドギャップ半導体を用いたFETを使用した、非常に大きな電力を直流に変換する直流電源装置において、1つの駆動電源にて各FETに正と負の駆動電圧を与えることで、低価格で小型かつ高効率の直流電源装置を得る。

【解決手段】入力段に突入電流保護回路1を有し、各FET3〜6に対し独立した駆動回路D3〜D6を有する。高電圧側のFET3、5をドライブトランス14により駆動し、低電圧側のFET4、6においては、駆動電源17およびFET4、6に流れる電流で充電される負バイアス用コンデンサ24によりゲート電圧を供給可能に構成する。

(もっと読む)

電源供給装置および電源供給方法

【課題】部品点数を削減し低コストで実現可能な過電流保護回路を備えた電源供給装置および電源供給方法を提供する。

【解決手段】タイマ回路6は、比較回路5から出力される過電流信号Scを所定時間連続して受信した時、遮断信号Sを出力する。制御回路7は、タイマ回路6から出力される遮断信号Sを入力すると、チャージポンプ回路8への制御信号の出力を停止する。これにより、スイッチング素子1のゲート端子への電圧印加がなくなり、スイッチング素子1が遮断される。

(もっと読む)

スイッチング素子の駆動回路

【課題】スイッチング素子S*#のオン状態への切り替えによってこれを流れる電流が急激に大きくなると、ツェナーダイオード40およびクランプ用スイッチング素子42を備えて構成されるクランプ回路による対処が間に合わなくなるおそれがあること。

【解決手段】ドライブIC20に端子T6を介して入力される操作信号g*#がオン操作指令に切り替わることで、定電流用スイッチング素子22をオン操作して、スイッチング素子S*#のゲートを充電する。スイッチング素子S*#のゲートの充電期間の初期において、クランプ用スイッチング素子42をオン状態としておく。

(もっと読む)

ゲート回路

【課題】本発明は、パワー素子の過電流を速やかに抑制しつつ、di/dtを小さくしてパワー素子をオフすることができるゲート回路を提供することを目的とする。

【解決手段】本発明に係るゲート回路は、パワー素子の過電流発生と同時にパワー素子のゲート電圧の一部を抵抗素子に負担させる過電流抑制手段を有する。さらに、パワー素子の過電流を抑制した後は、抵抗値の高い抵抗素子を用いてパワー素子をゆっくりオフするオフ動作遅延手段を有する。

(もっと読む)

1 - 20 / 142

[ Back to top ]