Fターム[5J022CB01]の内容

アナログ←→デジタル変換 (13,545) | 基準電圧・バイアス系 (1,329) | 基準電圧発生回路 (518)

Fターム[5J022CB01]の下位に属するFターム

分圧・レベル調整回路 (222)

Fターム[5J022CB01]に分類される特許

61 - 80 / 296

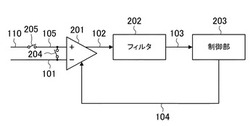

コンパレータのオフセット補正装置

【課題】コンパレータのオフセット補正装置において、ノイズの影響などに起因して、入力しようとしている電圧と実際入力されている電圧との間に差異がある場合にも、正常に閾値オフセット量を補正する。

【解決手段】コンパレータ201のオフセット補正に際しては、開放スイッチ205を開き、短絡スイッチ204を閉じる。この状態において、制御部203はコンパレータ201に対して、2つの入力端子に入力される同一値のリファレンス電圧同士を比較する動作を複数回繰り返させる。フィルタ202は前記複数回の比較結果を平滑化した頻度信号を出力する。前記制御部203は、前記フィルタ202からの頻度信号に基づいて、コンパレータ201での複数回の比較結果のハイレベルとローレベルとの比率が50%になるように、閾値制御信号をコンパレータ201に出力する。

(もっと読む)

半導体装置

【課題】 ADコンバータとともに半導体装置に搭載される機能ブロックの動作に依存せず、ADコンバータの変換精度を一定にする。

【解決手段】 半導体装置は、抵抗ラダーを有するADコンバータと、消費電流が異なる複数の動作モードを有する少なくとも1つの機能ブロックと、ADコンバータおよび機能ブロックに接続され、第1電源電圧を受ける第1電源端子と、機能ブロックの動作モードに応じて第1制御信号を出力する抵抗制御部と、第1電源端子と抵抗ラダーの間に配置され、第1制御信号に応じて抵抗値が変化する第1可変抵抗素子とを有している。機能ブロックの消費電流が動作モードに応じて変化するときにも、第1可変抵抗素子の抵抗値を変化させることで、抵抗ラダーに供給される基準電源電圧を一定にできる。

(もっと読む)

並列型A/D変換器

【課題】 動作の高速化を図ることができ、かつ後段の電圧設計の制約を緩和した並列型A/D変換器を提供する。

【解決手段】 本発明にかかる並列型A/D変換器の代表的な構成は、量子化レベルの段数に応じて並列に配置された複数のコンパレータと、差動入力信号を分岐して複数のコンパレータにそれぞれ入力する複数の信号ライン対と、複数のコンパレータごとに配置された複数のトラック・ホールド回路と、複数の信号ライン対に、コンパレータごとに電位差が段階的に異なる電圧を加算する電圧加算器と、を備えたことを特徴とする。

(もっと読む)

デコーダ及びそれを用いた表示装置のデータドライバ

【課題】出力可能な電圧レンジを拡大し、スイッチトランジスタのゲートサイズを縮減可能とし、面積の削減を可能とする。

【解決手段】互いに重複しない第1、第2の電圧区間にそれぞれ属する第1及び第2の参照電圧群20A、20Bを出力する参照電圧発生回路20と、第1及び第2の参照電圧群を入力し、入力デジタル信号に対応した参照電圧を選択するデコーダ10を備え、デコーダは第1の参照電圧群20Aを受ける第1のサブデコーダ11と、第2の参照電圧群20Bを受ける2のサブデコーダ12と、第2のサブデコーダ12で選択された参照電圧を受け第1のサブデコーダ11又は出力端子5に出力する第3のサブデコーダ13を含む。各サブデコーダ11、12、13はバックゲートに電源電圧Vbp1、Vbp2が供給されたトランジスタMP1、MP2、MP3を含む。

(もっと読む)

固体撮像装置および固体撮像装置の駆動方法

【課題】TADが出力するデジタル信号の線形性を補正するための補正式の算出処理を軽減することができる。

【解決手段】第2の補正計算部210は、A/D変換器20が出力するデジタル信号に基づいて、A/D変換器20が出力するデジタル信号の線形性を補正するための第2の補正式を算出する。判定部220は、第2の補正計算部210が算出した第2の補正式の係数と、この第2の補正式よりも前に算出した第2の補正式の係数とを比較した結果に基づいて、第1の補正式を算出するか否かを判定する。アップデート信号出力部230は、第1の補正式を算出すると判定された場合、第1の補正計算部110に第1の補正式を算出させるための信号を出力する。

(もっと読む)

ディジタルアナログ変換器

【課題】低消費電力で、素子の相対的なばらつきによって発生する信号歪みやSNR劣化が少ないディジタルアナログ変換器を提供する。

【解決手段】1ビットレジスタ103と、1ビットディジタルΔΣ信号及び、1ビットレジスタ103の出力信号を一対の入力信号とし、一対の出力信号を出力するスイッチ回路104、この一対の出力信号を入力し、ノイズを除去して第1出力信号、第2出力信号を出力する2端子対インピーダンス素子105、反転入力端子108a、非反転入力端子108b、出力端子108cを有する演算増幅器108、反転入力端子108aと出力端子108cとの間に接続されるインピーダンス素子106、非反転入力端子108bに一端が接続され、他端に基準電圧が与えられるインピーダンス素子107によってディジタルアナログ変換器を構成する。

(もっと読む)

アナログデジタルコンバータ

【課題】本発明はフォールディングアナログデジタルコンバータを提供する。

【解決手段】本発明のフォールディングアナログデジタルコンバータは、基準電圧発生部と、アナログ前処理部と、比較部と、エンコード部を備え、前記アナログ前処理部のフォルダの各々は前記アナログ入力信号を前記基準電圧と比べる複数のフォールディングユニットを含む。前記フォールディングユニットは従属的に接続され、以前のフォールディングユニットの出力によって自分の電流源を駆動して次のフォールディングユニットの電流源を動作モードに駆動する反面、前記アナログ入力信号が前記基準電圧より小さければ、前記次のフォールディングユニットの電流源をスリープモードに転換させる。

(もっと読む)

車載制御装置

【課題】簡易な構成で高精度な部品を用いることなくアナログ入力電圧の異常を検出することができる車載制御装置を提供する。

【解決手段】本発明に係る車載制御装置では、アナログ電圧出力部が出力するアナログ電圧のデジタル変換値を、動作開始前の時点であらかじめ記憶部に格納しておく。動作開始後に、アナログ電圧出力部が実際に出力するアナログ電圧のデジタル変換値と記憶部内の値との差分を求め、差分が所定閾値を超えていればADコンバータまたはアナログ電圧出力部に異常が発生していると判断する。

(もっと読む)

アナログデジタル変換装置

【課題】アナログデジタル変換器を2系統備えたアナログデジタル変換装置において、連続的なアナログデジタル変換処理を行ないつつ、オフセット電圧誤差をキャンセルできるようにする。

【解決手段】第2アナログデジタル変換器への入力を、入力アナログ信号と基準電位とで切り替えるスイッチと、スイッチが基準電位に切り替えられた際の第2アナログデジタル変換器の出力値を記憶する第2レジスタと、第1アナログデジタル変換器における入力アナログ信号の変換結果と第2レジスタの記憶値との和から、スイッチが入力アナログ信号に切り替えられた際の第2アナログデジタル変換器の出力値を差し引く第1演算部と、第1演算部の出力値を記憶する第1レジスタと、第1アナログデジタル変換器における入力アナログ信号の変換結果から第1レジスタの記憶値を差し引いて出力デジタル信号とする第2演算部とを備える。

(もっと読む)

A/D変換方法、A/D変換装置および読出回路

【課題】低い分解能のA/D変換ICを使用しても高い分解能でのA/D変換結果が得られるA/D変換装置の実現。

【解決手段】アナログ出力信号Voutをデジタル信号に変換するA/D変換装置であって、アナログ出力信号の電圧レベルが、複数のレベル領域A,B,C,Dのいずれに該当するかを判定する領域判定回路41,42,43と、該当するレベル領域に対応するシフト電圧を発生するシフト電圧発生回路44,45,47と、アナログ出力信号をシフト電圧変化させると共に、A/D変換入力レンジに対応するように増幅して増幅シフトアナログ信号を発生する演算増幅回路48,R1-R4と、増幅シフトアナログ信号をA/D変換して予備A/D変換値を算出する初段A/D変換回路11と、予備A/D変換値から該当するレベル領域に応じて最終A/D変換値を算出する最終A/D変換値算出回路31と、を備える。

(もっと読む)

信号発生装置および試験装置

【課題】雑音の小さい精度の良い電圧を出力する。

【解決手段】与えられる入力データに応じた出力電圧を出力端から出力する信号発生装置であって、与えられるデータに応じた電圧を出力するDA変換器と、出力端と基準電位との間に設けられたキャパシタ部と、DA変換器の電圧発生端と出力端との間を接続および切断する転送スイッチと、転送スイッチの接続および切断を繰返して入力データに応じた電圧を出力させたDA変換器によりキャパシタ部をチャージしていき、キャパシタ部の電圧を入力データに応じた出力電圧に順次に近づける制御部と、を備える信号発生装置を提供する。

(もっと読む)

D/Aコンバータ

【課題】抵抗ストリングが有する単位抵抗の相対精度に起因する変換誤差を低減させる抵抗ストリング型D/Aコンバータを提供すること。

【解決手段】本発明にかかる抵抗ストリング型D/Aコンバータ1は、上位抵抗ストリング10、第1の上位スイッチ11、上位デコーダ12、下位デコーダ13、変換部14を備える。上位抵抗ストリング10は、単位抵抗101を介して接続された複数の電圧取り出し点102を有する。上位デコーダ12は、上位ビットの値に応じて、第1の上位制御信号121を生成し、当該第1の上位制御信号121に基づいて、1つ以上の電圧取り出し点102を介して隣り合う一対の電圧取り出し点102に接続された第1の上位スイッチ11を導通させる。下位デコーダ13は、変換部14を制御する下位制御信号131を生成する。変換部14は、一対の電圧取り出し点102から出力される一対の上位アナログ電圧を分圧する。

(もっと読む)

信号処理回路

【課題】入力信号の大きさが温度に応じて変化する場合であっても、入力信号を精度良く量子化できる信号処理回路を提供する。

【解決手段】信号処理回路は、温度に応じて大きさが変化する入力信号を、設定される電圧範囲内で量子化してデジタル信号へと変換するADコンバータと、温度に応じて入力信号が大きくなると電圧範囲が広くなり、温度に応じて入力信号が小さくなると電圧範囲が狭くなるように、電圧範囲を設定する設定回路と、を備える。

(もっと読む)

入力回路及びそれを備えたアナログ/デジタルコンバータ

【課題】 n個のオフセット補正用キャパシタで3のn乗段階のオフセット補正を行うことが可能な入力回路及びそれを備えたアナログ/デジタルコンバータを提供する。

【解決手段】 オフセット補正キャパシタに接続される電位を3段階に切り替えることにより、1つのオフセット補正キャパシタで3段階のオフセット補正量を実現することが可能となる。これにより、n個の3進重み付けオフセット補正キャパシタを具備することによって3のn乗段階のオフセット補正量を実現することができる。

(もっと読む)

逐次比較型A/D変換器

【課題】コンパレータへの精度要求を緩和し、高速化を可能とした逐次比較型A/D変換器を提供する。

【解決手段】逐次比較型A/D変換器1を、CP構造部105_1〜(n+1)と制御部101と出力レジスタ102とコンパレータ104とを含む構成とし、各CP構造部を、キャパシタ201_11〜(2M)(n-2)(2M)と、スイッチ202a_11〜(2M)(n-2)(2M)と、スイッチ202b_11〜(2M)(n-2)(2M)と、スイッチ群203_1〜(2M)(n-2)と、スイッチ202c_12〜(2M)(n-2)(2M)とを含む第1〜第(2M)(n-2)の単位回路107_1〜107_(2M)(n-2)から構成し、制御部101によって各CP構造部を制御して、キャパシタ201_11〜201_(2M)(n-2)(2M)の接続構成を変更することで、コンパレータ104の被判定電圧を2M倍に昇圧する。

(もっと読む)

アナログ−デジタル変換器

【課題】高速動作可能な逐次比較型ADCの精度の向上。

【解決手段】サンプリング時にアナログ入力信号が印加される入力端子と、基準電位に接続される基準端子と、を有し、サンプリング時にアナログ入力信号の電圧に対応した電荷量を保持する入力信号容量Csと、サンプリング時に参照電圧の電圧に対応した電荷量を保持し、各参照容量の2つの端子は入力端子と基準端子に順接続状態または逆接続状態で接続可能な1個以上の参照容量23-1,23-10と、入力端子の電圧が基準電位より高いか低いかを判定するコンパレータ12と、判定結果に基づいて、入力端子の電圧が基準電位に近づくように、1個以上の参照容量の接続状態を選択しながら順次接続し、コンパレータの判定結果を合わせた結果からデジタル値を算出する制御回路と、を備えるAD変換器であって、入力信号容量および1個以上の参照容量の容量値は、非2進で設定されている。

(もっと読む)

逐次比較型A/D変換器

【課題】簡易な回路構成で、必要最低限の制御期間によるスイッチ群の駆動制御を実現するのに好適な逐次比較型A/D変換器を提供する。

【解決手段】逐次比較型A/D変換器1を、第1〜第nのキャパシタ106_1〜106_nと、スイッチ群105_1〜105_(n−1)と、制御部101と、コンパレータ104とを含む構成とし、制御部101を、カウンタ301aと、制御回路301bとを含む遅延量制御回路301と、任意遅延回路302と、制御信号生成回路303とを含む構成とし、遅延量制御回路301は、カウンタ値に基づき任意遅延回路302の遅延量を制御し、任意遅延回路302は、発振器からのクロック信号MCLKを制御された遅延量で遅延して遅延クロック信号DCLKを出力し、制御信号生成回路303は、DCLKに基づき必要最低限の制御期間Tkの制御信号CTRL105_1〜105_(n−1)を生成する。

(もっと読む)

DA変換回路用の基準電圧調整回路

【課題】 デジタル・アナログ(DA)変換回路の主要な用途のひとつに、機器を駆動するアナログ回路の制御がある。DA変換回路の分解能を最大限利用するため、DA変換回路の出力電圧の範囲(基準電圧と呼ぶ)の設定が重要である。アナログ回路に要求される出力電圧の範囲の値を使用者が入力することにより、DA変換回路の基準電圧を自動的に設定する基準電圧調整回路を得る。

【解決手段】 アナログ回路4と等価な入出力特性を有するダミー回路5と、ダミー回路5の出力電圧14と使用者が入力した電圧16とを比較して差分を出力する差動増幅回路6と、前記差分を減少させる電圧を発生して、帰還電圧としてダミー回路5に入力する電圧発生回路3とから成る基準電圧調整回路2により、自動的にDA変換回路1の基準電圧を調整する。

(もっと読む)

バンドギャップリファレンス回路及びこれを備えるADコンバータ、並びに、バンドギャップリファレンス回路の調整方法

【課題】温度依存性を持たないバンドギャップリファレンス回路を提供する。

【解決手段】第1及び第2の入力端に供給される電位差に基づいて電流経路PA,PBに流れる電流量を制御することによりリファレンス電圧を生成するオペアンプOPと、第1及び第2の入力端が電流経路PA,PBに含まれる接続点A,Bにそれぞれ接続されている場合に得られるリファレンス電圧VREF1と、第1及び第2の入力端が接続点B,Aにそれぞれ接続されている場合に得られるリファレンス電圧VREF2との中間値を生成するローパスフィルタLPFとを備える。これにより、オペアンプOPのオフセット電圧がキャンセルされることから、オフセット電圧がゼロである場合に得られる理想的なリファレンス電圧VREFを生成することが可能となる。

(もっと読む)

逐次比較型A/D変換器を内蔵する半導体集積回路およびその動作方法

【課題】下位ビットデジタル変換信号の精度の劣化を軽減する。

【解決手段】逐次比較型A/D変換器は、比較器1と逐次近似レジスタ2とローカルD/A変換器3と制御D/A変換器5と制御ユニット6を具備する。制御D/A変換器5の制御基準レベルVref´が基準電圧Vrefと同一の状態で、ローカルD/A変換器3のキャパシタアレイの上位アレイ31と下位アレイ32に既知の電圧レベルVin_Calを有するアナログ入力電圧が供給される。逐次近似レジスタ2の上位・下位ビットデジタル変換信号UB_0…、LB_0…とその理想値の誤差から、誤差を補償するコード値を有する制御デジタル信号CB_0…が制御ユニット6から制御D/A変換器5に供給され、コード値で制御された制御基準レベルVref´が下位アレイ32に供給され、実際のA/D変換が実行される。

(もっと読む)

61 - 80 / 296

[ Back to top ]