Fターム[5J022CB01]の内容

アナログ←→デジタル変換 (13,545) | 基準電圧・バイアス系 (1,329) | 基準電圧発生回路 (518)

Fターム[5J022CB01]の下位に属するFターム

分圧・レベル調整回路 (222)

Fターム[5J022CB01]に分類される特許

21 - 40 / 296

AD変換回路、光電変換装置、撮像システム、およびAD変換回路の駆動方法

【課題】より簡単な回路構成で高分解能な変換が実現できるAD変換回路を提供する。

【解決手段】参照信号とアナログ信号とを比較する比較部107と、増幅部106と、を有し、1段階目のAD変換によってi−bit(i≧2の整数)のデジタルコードを得、2段階目のAD変換によってj−bit(j≧2の整数)のデジタルコードを得ることで、前記アナログ信号を(i+j)−bitのデジタル信号に変換するAD変換回路であって、該AD変換回路は、前記1段階目のAD変換において、前記比較部で前記アナログ信号と前記参照信号との比較を行い、前記増幅部は、前記アナログ信号と、前記i−bitのデジタルコードに対応するアナログ信号と、の差分を増幅した増幅残差信号を出力し、前記2段階目のAD変換において、前記増幅残差信号を前記参照信号と前記比較部で比較する。

(もっと読む)

AD変換器、ダイヤル式入力装置、及び抵抗−電圧変換回路

【課題】ポテンショメータの抵抗値や電流源による電流が変化した場合でも、製造バラツキや使用環境等の影響を受けないデジタル出力を得ることができるAD変換器を提供する。

【解決手段】被第1積分電圧Vinが入力されているときに被第1積分電圧Vinと基準電圧Vcomとの差分の電圧を積分する第1積分を行い、第1積分の実行後、被第2積分電圧Vrefが入力されているときに被第2積分電圧Vrefと基準電圧Vcomとの差分の電圧を積分する第2積分を行い、少なくとも第2積分に応じた積分電圧を出力する積分器12と、第2積分を開始してから積分電圧と基準電圧Vcomとが等しくなるまでの時間を計測して出力するコンパレータ13及びLOGIC14と、を備えた2重積分型ADコンバータ10と、被第1積分電圧Vinを変化させるとともに、被第2積分電圧Vref及び基準電圧Vcomを変化させる抵抗−電圧変換回路30と、を備える。

(もっと読む)

パイプライン型A/D変換器、パイプライン型A/D変換器用校正装置

【課題】小型で演算にかかる負荷が小さい校正装置を備えたパイプライン型A/D変換器を提供する。

【解決手段】A/D変換器がモード1のとき第1デジタル信号を第1参照値と比較し、A/D変換器がモード2のとき第2デジタル信号を第2参照値と比較する比較器306、307、A/D変換器がモード1、モード2のいずれに設定されているかを判定するAND回路308、309、モード1、モード2の設定回数の合計が所定の回数に達した後、第1デジタル信号と第1参照値との大小関係、第2デジタル信号と第2参照値との大小関係、判定されたモード1またはモード2の別に応じて、第1参照値及び第2参照値を調整するヒットアキュムレータ310、調整後の第1参照値と第2参照値との差分を使って誤差を算出する加算回路312、314、レジスタ313によってパイプライン型A/D変換器用校正装置を構成する。

(もっと読む)

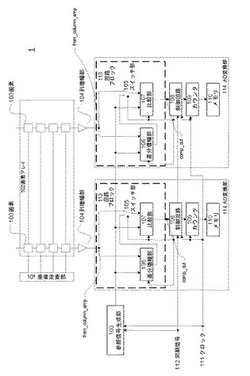

AD変換回路および撮像装置

【課題】誤カウントの発生を抑制することができるAD変換回路および撮像装置を提供する。

【解決手段】上位カウンタ101は、遅延回路から出力される第1の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行い、さらに下位カウンタ103から出力されるカウントクロックに基づいてカウントを行って第1の上位計数値を取得する。第1の上位計数値を構成する各ビットの値が反転された後、上位カウンタ101は、遅延回路から出力される第2の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行い、さらに下位カウンタ103から出力されるカウントクロックに基づいてカウントを行って第2の上位計数値を取得する。また、上位カウンタ101は、カウントクロックの切換えの際に保持している上位計数値を保護するデータ保護機能を有する。

(もっと読む)

A/Dコンバータの試験装置および試験方法

【課題】A/Dコンバータの試験時間の短縮にある。

【解決手段】Nビット(Nは自然数)のA/Dコンバータ1を試験する試験装置2が提供される。電圧生成部10は、A/Dコンバータ1に対して、2N階調のアナログ電圧VINを出力する。キャプチャユニット20は、各階調におけるA/Dコンバータ1の出力コードDOUTをキャプチャする。信号処理部30は、各階調においてキャプチャされた出力コードDOUTを対応する期待値コードEXPと比較し、比較結果に応じて各階調のアナログ電圧VINの値を補正し、電圧生成部10に補正後のアナログ電圧VINを出力させる。

(もっと読む)

アナログデジタル変換器

【課題】高速のAD変換器を提供する。

【解決手段】アナログ入力信号をデジタル出力信号に変換するAD変換器であって,アナログ入力信号と参照電圧とを比較して当該比較結果に応じたデジタル出力信号の各ビットを順次出力するN段の比較ユニットと,比較ユニットが出力するデジタル出力信号の各ビットに基づいて参照電圧に対応する参照電圧生成デジタル信号を順次生成する論理回路と,参照電圧生成デジタル信号に基づいて前記参照電圧を生成するDA変換器とを有する。そして,N段の比較ユニットは,それぞれ,前段からの状態制御信号の判定状態に応答してリセット状態から判定状態になる比較器と,比較器が判定状態で比較結果を出力したときに後段の比較ユニットへの状態制御信号を判定状態にする状態制御信号生成部とを有し,トリガクロックに応答して,N段の比較ユニットの比較器が上位のビットから下位のビットまで順次比較動作を行う。

(もっと読む)

アナログデジタル変換器

【課題】入力容量が小さく、バッファ回路の消費電力を削減したアナログデジタル変換器を提供する。

【解決手段】本発明の一態様としてのアナログデジタル変換器は、入力端子と、第1コンパレータと、第1出力端子と、第2コンパレータと、第2出力端子とを備える。第1コンパレータは、入力端子で受けた入力信号と第1参照信号を比較して、第1論理信号および制御信号を生成する。第1トランジスタは、入力信号に応じた電流を生成する。第1スイッチおよび第2スイッチは制御信号に応じて互いに短絡および開放が逆になるように切り替えられる。第2トランジスタは、第1スイッチがオンのとき、第2参照信号に応じた電流を、端子に供給する。第3トランジスタは、第2スイッチがオンのとき、第3参照信号に応じた電流を、端子に供給する。出力部は、第1トランジスタで生成された電流を、端子に供給された電流と比較して、第2論理信号を生成する。

(もっと読む)

キャリブレーション回路およびアナログ−デジタル変換器

【課題】多数の同一構成の回路のキャリブレーションを小面積・低電力・高精度に行う技術を提供する。

【解決手段】キャリブレーション回路において、各コンパレータ21〜2N毎に有する、アナログ制御電圧値を一定時間保持可能な容量を含むアナログ電圧保持回路151〜15Nと、各コンパレータ21〜2N毎に有する、現在のデジタル制御値を記憶するデジタルメモリ121〜12Nと、デジタルメモリ121〜12Nに記憶されている現在のデジタル制御値を入力として、デジタル制御値をアナログ制御電圧値に変換して出力する1個の高精度なDAC20と、DAC20に各コンパレータ21〜2Nのデジタルメモリ121〜12Nに記憶されている現在のデジタル制御値を順番にセットし、アナログ電圧保持回路151〜15Nの容量を定期的にリフレッシュするコントローラ30とを有する。

(もっと読む)

DA変換装置

【課題】複数のDA変換器のそれぞれの積分非直線性誤差の影響を抑えて高速動作できるとともに、SFDRを拡大させることができるDA変換装置を提供する。

【解決手段】デジタル信号源2で生成されたデジタルデータ及びクロック信号がDA変換装置1に入力される。DA変換装置1は、データ選択用スイッチ11と、複数のDA変換器としての第1のDA変換器12及び第2のDA変換器13と、切替手段としてのアナログ信号切替用スイッチ14と、分周器15とを有している。各DA変換器12,13の積分非直線性誤差特性の非線形歪特性は、互いに逆の特性である。第1,2のDA変換器12,13の積分非直線性誤差特性は、第1,2のDA変換器12,13の両方の積分非直線性誤差を平均すると、ゼロに近づくような特性である。

(もっと読む)

A/Dコンバータ

【課題】アナログ入力信号の信号レベルに応じてFSR電圧を変化させることにより、D/Aコンバータの基準電圧を切り替える基準電圧発生回路の有無に関係なく、電圧変動の小さなアナログ入力信号に対する分解能を充分に向上させることができるA/Dコンバータを提供すること。

【解決手段】A/Dコンバータは、複数のアナログ入力信号のうちのいずれか1つを選択して出力する選択部の出力を第1比較基準電圧と比較する比較部と、前記複数のアナログ入力信号のうちのいずれか1つのアナログ入力信号の電圧変動範囲に応じた第2比較基準電圧を出力するD/Aコンバータと、前記選択部で選択されたアナログ入力信号の電圧変動範囲に応じて、前記D/Aコンバータが出力する第2比較基準電圧を前記第1比較基準電圧に切り替えて前記比較部に出力する切替部とを含む。

(もっと読む)

A/D変換回路

【課題】温度変化にかかわらず高い変換精度を得る。

【解決手段】第1パルス周回回路6はアナログ入力電圧Vinで動作し、第2パルス周回回路7は規定電圧Vcとアナログ入力電圧Vinとの差電圧で動作する。第3パルス周回回路8は参照電圧Vrで動作する。クロック信号CLKの周期ごとに、カウンタ23〜25は各パルス周回数をカウントし、ラッチ&エンコーダ17〜19は各パルス位置をラッチする。パルス周回数とパルス位置とからなる周回データの今回値と前回値の差分値を演算してデジタルデータD1、D2、D4(=Yr)とし、D1−D2よりD3(=Y)を演算する。その後、Y/(Yr−Y0)を演算してA/D変換データを得る。Y0はROMから読み出され、パルス周回回路6、7、8の温度特性が0となる電圧に対する周回データである。

(もっと読む)

二重積分型A/D変換器

【課題】両極性の入力電圧を変換可能であり、且つ、ディジタル値として異常値が出力されるのを防止することが可能な二重積分型A/D変換器を提供する。

【解決手段】両極性の入力電圧を変換可能な二重積分型A/D変換器であって、入力電圧Vinを積分する第1積分期間が終了する直前において積分器1の出力電圧Voutが基準電圧VAGNDよりも高い第1の比較基準電圧VHと基準電圧VAGNDよりも低い第2の比較基準電圧VLとの範囲VH〜VL内にあり、且つ、基準電圧VAGNDよりも高い第1の参照電圧VREF+あるいは基準電圧VAGNDよりも低い第2の参照電圧VREF-を積分する第2積分期間において一定周期のクロックパルスをカウントし積分器1の出力電圧Voutが基準電圧VAGNDに戻るまでのカウント値をディジタル値として出力するカウンタ4がオーバーフローしたときに、カウンタ4のカウント値をゼロにリセットさせる補正手段8を備えている。

(もっと読む)

二重積分型A/D変換器

【課題】両極性の入力電圧を変換可能であり、且つ、カウンタのカウント値が異常値であるか否かを判定することが可能な二重積分型A/D変換器を提供する。

【解決手段】第1積分期間の終了時におけるコンパレータ3の出力に基づいて積分器1の出力電圧Voutの基準電圧VAGNDに対する大/小に基づく極性を“H”/“L”として判定して出力するとともに極性判定結果に応じて入力切替部2を制御する制御回路(制御部)5と、積分器1の出力電圧Voutを基準電圧VAGNDよりも高い第1の比較基準電圧VH、基準電圧VAGNDよりも低い第2の比較基準電圧VLそれぞれと比較して各比較結果ごとに大/小に応じて“H”/“L”の出力を発生する比較手段7とを備える。ディジタル回路8は、カウンタ4のカウント値が最大値であり、且つ、制御回路5での極性判定結果と比較手段7による両方の比較結果とが異なるときに、カウント値を異常値と判定する異常判定手段を有する。

(もっと読む)

電池電圧測定システム及び電池電圧測定方法

【課題】電池電圧測定システムの規模を縮小化することができる、電池電圧測定システム及び電池電圧測定方法を提供する。

【解決手段】レギュレータ14が電池電圧VDDに基づいて生成した定電圧VregがA/Dコンバータ12のアナログ入力端子Ainに入力される。また、A/Dコンバータ12の基準電圧端子には、電源電圧20から端子(パッド)18を介して直接、電池電圧VDDが入力される。A/Dコンバータ12は、電池電圧VDDを基準電圧Vrefとして、当該基準電圧Vrefに対する入力電圧Ain=定電圧Vregのレベルを判定し、A/D変換した変換結果Doutを出力する。電池電圧VDDの低下に伴い、変換結果Doutは大きくなるため、処理部16では、変換結果Doutに基づいて電池電圧VDDの測定・監視を行う。

(もっと読む)

量子化器及びそれを備えたデルタシグマ変調器

【課題】回路規模の増大を抑制等しつつ、入力電圧を精度良くサンプリングすることが可能な量子化器を提供すること。

【解決手段】本発明にかかるデルタシグマ変調器は、リファレンス電圧を生成するリファレンス電圧生成部と、基準クロックをN倍に逓倍した逓倍クロックに同期して、リファレンス電圧と外部入力電圧とを比較し、比較結果を出力するコンパレータと、基準クロックに同期して比較結果を検出し、バイナリコードに変換して外部に出力する出力部と、を備え、リファレンス電圧生成部は、複数のプリリファレンス電圧を生成する抵抗部と、複数のプリリファレンス電圧のうち比較結果に基づいて選択された何れかの電圧を、リファレンス電圧として出力するスイッチ部と、を有する。

(もっと読む)

A/D変換回路

【課題】動作用電源電圧の中央付近の電圧を含む広範囲のアナログ入力電圧に対し、温度変化にかかわらず高い変換精度を得られ、補正演算や事前の特性測定を不要とする。

【解決手段】第1パルス周回回路2は規定電圧Vccとアナログ入力電圧Vinとの差電圧で動作し、第2パルス周回回路3はアナログ入力電圧Vinで動作する。第1カウンタ20はパルス周回回路2、3のパルス周回数差を出力する。第3パルス周回回路4は規定電圧と設定電圧Vsetとの差電圧で動作し、第4パルス周回回路5は設定電圧Vsetで動作する。第2カウンタ21はパルス周回回路4、5のパルス周回数差を出力する。パルス周回回路2〜5を同時に周回動作させ、第2カウンタ21の出力値が規定値Yに達すると変換データ出力処理信号Saを出力し、その時の第1カウンタ20の出力値をA/D変換データとして出力する。

(もっと読む)

電子制御装置

【課題】A/D変換器の異常を検出することができるとともに、A/D変換用の基準電圧の異常も検出することができる電子制御装置を提供する。

【解決手段】メインマイコン異常判定手段14は、メインマイコンA/D変換器11からのデジタルデータ11aに基づくVccの電圧値が閾値13a以上であるか否かを確認することによって、メインマイコンA/D変換器11及びVrefの異常判定を行う。サブマイコン異常判定手段24は、サブマイコンA/D変換器21からのデジタルデータ21aに基づくVccの電圧値が閾値23a以上であるか否かを確認することによって、サブマイコンA/D変換器21及びVrefの異常判定を行う。異常識別手段15は、メインマイコン異常判定手段14及びサブマイコン異常判定手段24の両方の異常判定結果を用いて、異常発生部位を識別する。

(もっと読む)

信号監視システム

【課題】信号監視システムを提供する。

【解決手段】信号監視システムは、変換回路と、前記変換回路に連結された制御器とを備える。前記変換回路は、調整基準値の実時間のレベルに基づいて、基準入力値を基準出力値に変換すると共に、監視される信号を出力信号に変換する。前記制御器は、前記基準出力値に従って、そして、あらかじめ定義された基準値に従って、前記出力信号を較正する。前記あらかじめ定義された基準値は、前記基準入力値により、及び前記調整基準値のあらかじめ調整されたレベルにより決定される。

(もっと読む)

AD変換器及びAD変換回路の電圧制御方法

【課題】AD変換の際のアナログ入力振幅の収束時間を短縮させつつ、AD変換回路が想定する量子化分解能を最大限に活用することが可能なAD変換器を提供する。

【解決手段】アナログ信号からデジタル信号に変換するAD変換回路へ、アナログ信号の入力の振幅を可変させて出力するAGC回路と、AGC回路が出力するアナログ信号の出力範囲と、既定の電圧の範囲と比較して、該比較の結果に基づいてAGC回路が出力するアナログ信号の出力範囲を制御する第1検波部と、を備える、AD変換器が提供される。これにより、AD変換の際のアナログ入力振幅の収束時間を短縮させつつ、AD変換回路が想定する量子化分解能を最大限に活用することが可能なAD変換器を提供することができる。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスからの検出信号の精度の高いA/D変換を実現できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、電源電圧VDDAを生成する電源回路60と、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAに基づいて動作し、電源電圧VDDAにより規定されるA/D変換範囲で、センサーデバイス30からの検出信号に対応する信号についてのA/D変換を行うA/D変換器ADCと、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAをセンサーデバイス30に供給する電源端子PVDAを含む。

(もっと読む)

21 - 40 / 296

[ Back to top ]