Fターム[5J022CB01]の内容

アナログ←→デジタル変換 (13,545) | 基準電圧・バイアス系 (1,329) | 基準電圧発生回路 (518)

Fターム[5J022CB01]の下位に属するFターム

分圧・レベル調整回路 (222)

Fターム[5J022CB01]に分類される特許

41 - 60 / 296

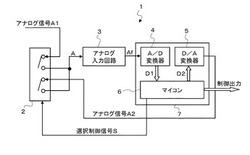

アナログ信号入力装置

【課題】アナログ入力回路及びA/D変換器を含むアナログ信号入力装置の故障を、高精度かつ汎用性をもって診断できるようにすることを目的とする。

【解決手段】アナログ信号入力装置1は、マルチプレクサ2、アナログ入力回路3、A/D変換器4、D/A変換器5、マイコン6を備えている。そして、故障診断時には、マイコン6からD/A変換器5に対してディジタル信号D2を出力し、D/A変換器5が、ディジタル信号D2をD/A変換して得たアナログ信号A2を、マルチプレクサ2を介してアナログ入力回路3に入力させる。そして、アナログ入力回路3が出力するアナログ信号Afを、A/D変換器4でA/D変換して得たディジタル信号D1をマイコン6に取り込ませる。マイコン6は、ディジタル信号D1が、ディジタル信号D2に見合う範囲内の信号であるか否かに基づいて、マルチプレクサ2、アナログ入力回路3、A/D変換器4、D/A変換器5を含む回路における故障の有無を診断する。

(もっと読む)

比較回路及び信号変換装置

【課題】アナログデジタル変換の分解能を向上させる比較回路及び信号変換装置を提供する。

【解決手段】比較回路22は、コンパレータ22aが、第1の入力端子に接続される第1の電圧源により、第1の入力端子に印加される電圧と、第2の入力端子に入力される入力信号の電圧とを比較する。コンデンサ22bが、第1の入力端子に一方の端子が接続され、第1の電圧源側に他方の端子が接続される。スイッチ22cが、第1の入力端子への基準電圧源22の接続を選択的に遮断する。スイッチ22dが、コンデンサ22bの他方の端子への第1の電圧源の接続を選択的に遮断する。基準電圧源22fが、コンデンサ22bの他方の端子に接続される。スイッチ22eが、基準電圧源22fによりコンデンサ22bの他方の端子に印加される電圧を選択的に遮断する。

(もっと読む)

スイッチトキャパシタ型回路及びそれを用いたAD変換回路

【課題】消費電力を増大させることなく、高精度な基準電圧の下で動作するスイッチトキャパシタ型回路を提供する。

【解決手段】(1)第1のスイッチトキャパシタ(スイッチ11〜13及び帰還容量Cf)とサンプリング容量Csと増幅回路100とを含むスイッチトキャパシタ型増幅回路110aと、(2)スイッチトキャパシタ型増幅回路110aに基準電圧Vrefを供給する基準電圧回路110bとを備え、基準電圧回路110bは、基準電圧Vrefを出力するバッファ回路1と、バッファ回路1の出力端子111とスイッチトキャパシタ型増幅回路110aに基準電圧Vrefを供給するための基準電圧入力端子112との間に接続された第2のスイッチトキャパシタ(スイッチ10及び容量Cc)とを有する。

(もっと読む)

二重積分型AD変換器および積分型AD変換器

【課題】本発明によれば、クロックパルス発生器の周波数が比較的低い場合にも、自身の積分回路のコンデンサの静電容量を、ICに内蔵可能となる程度に小さくすることが可能な二重積分型AD変換器を実現することができる。

【解決手段】本発明は、測定電圧またはこの測定電圧と逆極性の標準電圧のいずれかを選択し出力するセレクタと、このセレクタの出力を積分する積分回路と、クロックパルスを発生するクロックパルス発生器とを有し、前記積分回路の積分値が予め定められた値となるまでの時間を前記クロックパルスで計測し、計測した時間に基づいてアナログデジタル変換する二重積分型AD変換器において、前記クロックパルスに基づいてこのクロックパルスよりもパルス幅の小さい微小パルスを生成する微小パルス発生回路と、前記セレクタと前記積分回路との間に設けられ、前記微小パルスを入力し、そのパルス幅に相当する期間においてのみ前記セレクタと前記積分回路とを接続するスイッチと、を備えたことを特徴とする。

(もっと読む)

デジタルアナログ変換回路及び表示ドライバ

【課題】CMOS化するスイッチ数、ゲート幅増加を抑制し、面積増加を抑制可能とする、デジタルアナログ変換器、データドライバ、表示装置を提供。

【解決手段】参照電圧集合体80は第1、第2の参照電圧群81、82を含み、デコーダ100は、mビットのデジタル信号の上位側(m−n)ビットの信号を共通に入力する第1乃至第2のサブデコーダ部10、20と、前記mビットのデジタル信号の下位側nビットの信号を共通に入力する第3乃至第4のサブデコーダ部30、40と、を備え、前記第1及び第3のサブデコーダ部10、30は第1導電型のトランジスタよりなり、前記第2及び第4のサブデコーダ部20、40は第2導電型のトランジスタよりなり、増幅回路50は入力に受けた電圧を、予め定められた重み付けで平均し、前記重み付け平均した電圧、前記mビットのデジタル信号に対応したアナログ信号として出力端子51から出力する。

(もっと読む)

AD変換器を備えた温度検知回路及び半導体集積回路

【課題】AD変換器を備えた温度検知回路において、温度依存性のあるアナログ電圧のように定常的で変化の遅い信号を前記AD変換器を用いて検知する場合に、そのAD変換器の分解能を劣化させずに、消費電力の削減や信号処理時間の短縮を図る。

【解決手段】動作開始時に一旦逐次比較型AD変換器1を動作させて、電圧発生回路BGR1からの温度依存性のあるアナログ電圧について前記AD変換器1でAD変換して、そのデジタル信号の全ビットを確定する。その後、電力制御回路2は、前記アナログ電圧の電位を挟む上下隣り合う基準電圧が入力されたコンパレータの出力変化のみを検出し、前記アナログ電圧の電位を挟む上下隣り合う基準電圧が入力されたコンパレータ以外のコンパレータへの電源供給を遮断する。

(もっと読む)

アナログディジタル変換器およびアナログ信号に対応したディジタル信号を生成する方法

【課題】一サンプリング当たりにA/D変換時間を短縮すること可能なアナログディジタル変換器を提供することを目的とする。

【解決手段】A/D変換ステージ101でのサンプル値Rに変換操作Bを施して変換結果D3を生成しこの変換結果D3にA/D変換ステージ103でサンプリング操作Aを施す。A/D変換ステージ105でのサンプル値に変換操作Bを施して変換結果D4を生成しこの変換結果D4にA/D変換ステージ107でサンプリング操作Aを施す。A/D変換ステージ107でのサンプル値に変換操作Bを施して変換結果D5を生成しこの変換結果D5にA/D変換ステージ101でサンプリング操作Aを施す。A/D変換ステージ103でのサンプル値に変換操作Bを施して変換結果D6を生成しこの変換結果D6にA/D変換ステージ105でサンプリング操作Aを施す。

(もっと読む)

A/D変換ステージおよびA/D変換ステージにおける変換誤差を示す信号を生成する方法

【課題】一サンプリング当たりにA/D変換時間を短縮すること可能なアナログディジタル変換器を提供することを目的とする。

【解決手段】A/D変換ステージ101でのサンプル値Rに変換操作Bを施して変換結果D3を生成しこの変換結果D3にA/D変換ステージ103でサンプリング操作Aを施す。A/D変換ステージ105でのサンプル値に変換操作Bを施して変換結果D4を生成しこの変換結果D4にA/D変換ステージ107でサンプリング操作Aを施す。A/D変換ステージ107でのサンプル値に変換操作Bを施して変換結果D5を生成しこの変換結果D5にA/D変換ステージ101でサンプリング操作Aを施す。A/D変換ステージ103でのサンプル値に変換操作Bを施して変換結果D6を生成しこの変換結果D6にA/D変換ステージ105でサンプリング操作Aを施す。

(もっと読む)

入力セレクタおよび信号処理回路

【課題】さまざまな入力形式の信号に柔軟に適応可能な汎用性の高い入力セレクタを提供する。

【解決手段】第1抵抗R1〜第4抵抗R4は、それぞれの第1端子が対応する入力ポートPi1〜Pi4に接続される。第1スイッチSW1〜第4スイッチSW4はそれぞれ、対応する抵抗と第1演算増幅器10の反転入力端子の間に設けられる。第5スイッチSW5、第6スイッチSW6はそれぞれ、対応する抵抗と、第2演算増幅器12の反転入力端子の間に設けられる。第5抵抗R5および第7スイッチSW7は第1演算増幅器10の出力端子と第2演算増幅器12の反転入力端子の間に直列に設けられる。第6抵抗R6は第1演算増幅器10の出力端子と反転入力端子の間に設けられ、第7抵抗R7は第2演算増幅器12の出力端子と反転入力端子の間に設けられる。

(もっと読む)

アナログ信号に対応したディジタル信号を生成する方法

【課題】一サンプリング当たりにA/D変換時間を短縮すること可能なアナログディジタル変換器を提供することを目的とする。

【解決手段】A/D変換ステージ101でのサンプル値Rに変換操作Bを施して変換結果D3を生成しこの変換結果D3にA/D変換ステージ103でサンプリング操作Aを施す。A/D変換ステージ105でのサンプル値に変換操作Bを施して変換結果D4を生成しこの変換結果D4にA/D変換ステージ107でサンプリング操作Aを施す。A/D変換ステージ107でのサンプル値に変換操作Bを施して変換結果D5を生成しこの変換結果D5にA/D変換ステージ101でサンプリング操作Aを施す。A/D変換ステージ103でのサンプル値に変換操作Bを施して変換結果D6を生成しこの変換結果D6にA/D変換ステージ105でサンプリング操作Aを施す。

(もっと読む)

アナログデジタル変換用ランプ波発生器ユニット素子

【課題】傾きを段階的に増加したランプ波発生する新しいユニット素子のアプローチを提案する。

【解決手段】ランプ波発生のための方法は、基準電源を提供する段階と、加算増幅器を提供する段階と、前記基準電源と加算増幅器との間に並列に接続されたn個のスイッチトキャパシタ素子を提供する段階と、まず動作状態となった各スイッチトキャパシタ素子に電荷を充電し、次に繰り返し処理におけるタイムスロットの固定整数回の各回ごとに前記動作状態となったスイッチトキャパシタ素子の電荷総量を測定するため所定の数のスイッチトキャパシタ素子を選択的に動作させる段階とを具備しており、前記所定の数は、0からnの範囲となっている。

(もっと読む)

AD変換回路およびAD変換方法

【課題】ラッチコンパレータを用いた補間型のAD変換回路において、AD変換回路の高ビット化に伴う較正用回路の回路規模の増大を抑制する。

【解決手段】 AD変換の各段階に対応する刻み幅で設定された参照電圧と入力アナログ信号電圧とを比較する複数の比較器のうち2つの出力がそれぞれ入力される少なくとも一つの補間比較器と、各補間比較器の一致判定誤差を補正するための補正値を、複数の段階それぞれについて求める補正値取得部と、AD変換の段階ごとに、各補間比較器にそれぞれの補正値を設定する補正値適用部とを備え、補正値取得部は、AD変換の段階の一つにおける判定レベルに相当する個別テスト電圧の入力に応じて前記補正対象の補間比較器の出力として得られる前記判定レベルに対応する一致判定誤差と、前記共通テスト電圧を比較器に共通に入力した際に得られる一致判定誤差とに基づいて、前記各段階における判定レベルに対応する補正値を算出する補正値算出部を備える。

(もっと読む)

ΣΔ型AD変換器を用いた角速度センサ

【課題】本発明は、電源電圧変化や温度変化の影響により、DA変換手段、積分回路からの出力信号が変動するということはなく、出力特性が安定しているΣΔ型AD変換器およびそれを用いた角速度センサを提供することを目的とするものである。

【解決手段】本発明は、センサ素子30と、ドライブ回路131と、センス回路74とを備えた角速度センサにおいて、ドライブ回路131を、入力切替手段132、DA変換手段133、積分手段134、比較手段135、DA切替手段136を有するΣΔ変換器151と、デジタルバンドパスフィルタ137と、AGC回路138および駆動回路139とにより構成した。

(もっと読む)

A/D変換器

【課題】高速な参照クロック発振器やアナログ波形発生器を必要とせずに、回路規模や消費電力、高周波ノイズの増大を抑えることのできる単一スロープ型A/D変換器を提供する。

【解決手段】回路構成の簡易な定電流源23を内蔵したS/H回路12を用いることによりアナログ信号Vinの電圧レベルと参照ランプ波Rinの電圧レベルとを比較する。また、遅延素子31−1〜31−15を内蔵した遅延回路・デコーダ16とを用いることにより、時間が経過するのにつれて異なるステップ信号D0〜D15の合成値D[15:0]を基にして、ディジタル出力信号Doutを求める。このため、高速な参照クロック発生器やアナログ波形発生器を用いることなく、単一スロープ型A/D変換処理を行うことができる。

(もっと読む)

逐次比較型AD変換器

【課題】低電圧動作時に適切に動作可能な逐次比較型AD変換器を提供する。

【解決手段】逐次比較型AD変換器は、入力電圧と第1の電圧との差に応じた電荷を蓄えた複数の容量素子の接続を切り換え、指定の割合の容量を第2の電圧と中間ノードとの間に接続し、残りの容量を前記中間ノードと第3の電圧との間に接続する容量DA変換器を含み、第1の電圧は第2の電圧よりも第3の電圧に近く、制御ユニットは、第2の電圧から第3の電圧までの範囲を1:3に分割した点の比較対象電圧よりも入力電圧のほうが前記範囲の中心に近い場合には、容量DA変換器に対して指定の割合を0.5に設定して最上位ビットを判定してからデジタル値の他のビットを判定し、比較対象電圧よりも入力電圧のほうが前記範囲の中心から遠い場合には、容量DA変換器に対して指定の割合を0.5に設定した最上位ビットの判定をスキップしてデジタル値のビットを判定する。

(もっと読む)

パイプライン型A/Dコンバータ

【課題】熱雑音および演算増幅器に要求されるオープンループゲインを大きくさせることなく、入力レンジおよびディジタル出力信号のビット数を大きくすることのできるパイプライン型A/Dコンバータを提供する。

【解決手段】サンプルホールド用のコンデンサの個数MをN分割し、さらに基準電圧をN倍することで、基準電圧を加減算するために用いることが出来るコンデンサの数を増加させて入力レンジを広げ、ディジタル出力信号のビット数を大きくする。この場合、全てのコンデンサでアナログ信号をサンプルするため、コンデンサを分割する前後で熱雑音を劣化させない。さらに、アナログ信号を増幅するための帰還素子として用いるコンデンサと、残りのコンデンサとの比はコンデンサを分割する前後で変わらないため、演算増幅器128に要求されるオープンループゲインを増加させない。

(もっと読む)

A/D変換器および信号処理回路

【課題】D/A変換機能を有するものであって、回路構成の変更を伴うことなくA/D変換およびD/A変換の分解能を変更可能なA/D変換器を提供する。

【解決手段】巡回型A/D変換器1は、外部から与えられるADC/DAC機能切替信号に応じて制御回路10がスイッチS1〜S11の切り替えを制御することにより、外部より信号入力端子3を介して入力される入力信号電圧VinをA/D変換して12ビットのA/D変換値を出力するA/D変換動作と、外部より与えられるデジタル値をD/A変換して得られるアナログ電圧Voutを信号出力端子9を介して出力するD/A変換動作とを選択的に実行可能に構成される。

(もっと読む)

AD変換回路、及び、誤差補正方法

【課題】AD変換誤差を確実に補正し、アナログ信号をより高精度でデジタルデータに変換可能なAD変換回路、および、誤差補正方法を提供する。

【解決手段】入力電圧Vinをデジタルデータに変換し、このデジタルデータの誤差を補正するマイコン10において、電圧変動を含まない標準電源が供給された場合にAD変換器15が基準電圧VrefをAD変換することで得られる第1の変換値と、通常動作用の電源Vccが供給された状態でAD変換器15が基準電圧VrefをAD変換して得られる第2の変換値とをもとに、電源Vccが有する電圧変動ΔVccを算出し、算出した電圧変動ΔVccに基づいて、AD変換器15がアナログ信号をAD変換した変換値を補正する。

(もっと読む)

A/D変換装置

【課題】装置構成に要する費用が嵩んだり、装置が大型化することを防止し、変換周期を短縮する。

【解決手段】A/D変換装置10の記憶部12は、アナログ信号が入力される複数のチャンネルCH1,…,CHn毎に対応付けられた複数の基準電圧Vrefを予め記憶する。電圧選択部13は、記憶部12に記憶された複数の基準電圧Vrefの何れか1つを選択して基準電圧出力部14から出力させ、全チャンネルCH1,…,CHnのA/D変換が完了する毎に基準電圧Vrefの選択を変更して、全て基準電圧Vrefを順次出力させる。A/D変換器15は、全ての基準電圧Vrefと全チャンネルCH1,…,CHnとの組み合わせ毎のデジタル信号のうち、予め記憶部12に記憶された基準電圧Vrefと各チャンネルとの対応付けに等しい組み合わせのデジタル信号を出力する。

(もっと読む)

コンパレータのオフセット補正装置

【課題】コンパレータのオフセット補正装置において、ノイズの影響などに起因して、入力しようとしている電圧と実際入力されている電圧との間に差異がある場合にも、正常に閾値オフセット量を補正する。

【解決手段】コンパレータ201のオフセット補正に際しては、開放スイッチ205を開き、短絡スイッチ204を閉じる。この状態において、制御部203はコンパレータ201に対して、2つの入力端子に入力される同一値のリファレンス電圧同士を比較する動作を複数回繰り返させる。フィルタ202は前記複数回の比較結果を平滑化した頻度信号を出力する。前記制御部203は、前記フィルタ202からの頻度信号に基づいて、コンパレータ201での複数回の比較結果のハイレベルとローレベルとの比率が50%になるように、閾値制御信号をコンパレータ201に出力する。

(もっと読む)

41 - 60 / 296

[ Back to top ]