Fターム[5J024KA02]の内容

Fターム[5J024KA02]に分類される特許

21 - 40 / 139

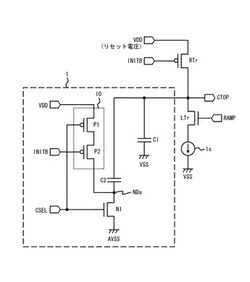

可変容量素子

【課題】従来の可変容量素子は、容量値の精度が低い問題があった。

【解決手段】本発明の可変容量素子は、第1の電源端子と出力端子CTOPとの間に接続される第1の容量素子C1と、容量切替信号CSELに応じて導通状態が切り替えられる容量選択スイッチN1と、第1の容量素子C1と並列に接続され、かつ、容量選択スイッチN1と直列に接続される第2の容量素子C2と、容量選択スイッチN1が遮断状態とされる状態において、出力端子CTOPをリセット電圧にリセットする電荷リセット信号INITBに応じて、第2の容量素子C2と容量選択スイッチN1とを接続する容量切替ノードNDaの電圧と出力端子CTOPの電圧とを実質的に同じ電圧に設定する誤差補正回路10と、を有する。

(もっと読む)

接続部品、電子機器及び板部材

【課題】グリッドアレイ型電子部品と実装基板とを接続する、製造容易でノイズ耐性が優れた接続部品を提供する。

【解決手段】上端面10uに長手方向に沿って第1のピッチで第1の嵌合溝が設けられた長方形板状の複数の横桁板1hと、下端面10dに長手方向に沿って第2のピッチで第2の嵌合溝が設けられた長方形板状の縦桁板1vと、第1の嵌合溝の内面から第1の嵌合溝の周囲の横桁板上に延在する第1の導電体膜11と、第2の嵌合溝の内面から第2の嵌合溝の周囲の縦桁板上に延在する第2の第2の導電体膜11と、隣接する第1又は第2の導電体膜間を接続するチップ部品12とを有し、平行配置された複数の横桁板1h及び縦桁板1vを互いに嵌合溝に嵌合させて格子体に組立てた接続部品20。

(もっと読む)

積層型フィルタ

【課題】インダクタンスの大きさを増加させ,小型化による共振周波数の変化を最小化させる積層型フィルタの提供。

【解決手段】積層型フィルタ200は、複数の誘電体層が積層されたセラミック本体と、上記セラミック本体の外部面に形成されてグラウンドに連結される外部接地電極と、上記誘電体層のうち少なくとも1つに形成され、一端が上記外部接地電極に連結されるインダクタパターン電極35と、上記誘電体層のうち少なくとも1つに形成されるキャパシタパターン電極55と、上記インダクタパターン電極と上記キャパシタパターン電極とを電気的に連結し、上記外部接地電極によりインダクタンスを発生させる閉ループを形成させる外部端子電極と、上記キャパシタパターン電極と上記インダクタパターン電極との間に備えられ、上記インダクタパターン電極によるインダクタンスの大きさを調節する可変誘電体層40と、を含むことができる。

(もっと読む)

多重通信用ジョイントコネクタ

【課題】必要とされるインピーダンス特性を汎用品のフェライトコアを用いて実現することができる多重通信用ジョイントコネクタを提供する。

【解決手段】本発明の多重通信用ジョイントコネクタは、コネクタハウジング21内には、インピーダンス特性が異なる複数のフェライトプレート22〜24が配置され、複数のフェライトプレート22〜24のインピーダンス特性を加算したものは、フィルタとして必要とされる所定のインピーダンス特性を満たす。

(もっと読む)

コモンモードフィルタ

【課題】 超高速差動信号を通過させ、コモンモードノイズを通過させ難くする差動遅延線型コモンモードフィルタを得る。

【解決手段】 差動線路1、3中に直列配置したインダクタLo1〜Lo3を含む受動直列素子と、インダクタLo1〜Lo3を橋絡する橋絡容量Ca1〜Ca3と、差動線路1、3間に並列配置された2個の直列キャパシタCoを含む受動並列素子とから全域通過型差動遅延線を形成する。キャパシタCoの接続点T1〜T3とグランド間にコモンモードノイズ減衰用インダクタLc1〜Lc3を挿入し、1区間の差動遅延線型コモンモードフィルタCMF1〜CMF3を形成する。複数の差動遅延線型コモンモードフィルタCMF1〜CMF3を従属接続し、各区間のコモンモードノイズ減衰用インダクタ値および橋絡容量値を異ならせる。

(もっと読む)

ノイズフィルタ部品,ノイズフィルタ構造及びノイズフィルタ部品の使用方法

【課題】高速な差動信号と低速なシングルエンド信号が同一ライン上に混在するような伝送規格において、差動信号及びシングルエンド信号を、その波形品質に影響を与えることなく通すことができるノイズフィルタ部品,ノイズフィルタ構造及びノイズフィルタ部品の使用方法を提供する。

【解決手段】ノイズフィルタ部品1−1はコモンモードチョークコイル部2とコイル3とコイル4と外部電極6−1〜6−4とを備える。コモンモードチョークコイル部2は、高周波帯の差動信号を通す部分であり、コイル21,22を有する。外部電極6−1,6−2はコイル21の両端部に接続され、外部電極6−3,6−4はコイル22の両端部に接続されている。コイル3,4は、差動信号よりも低い周波数帯のシングルエンド信号を通すためのコイルであり、コイル21,22に並列に接続されている。

(もっと読む)

ガラスアンテナ用フィルタ装置及び車両用窓ガラス

【課題】本発明は、2極タイプのガラスアンテナのアース側給電部が電気的に接続されたデフォッガに、他のメディアのガラスアンテナのアンテナ導体を電気的に接続しても、これらの両ガラスアンテナのアンテナ利得の低下を抑えられ、両ガラスアンテナを共存させることができる、車両用窓ガラス等の提供を目的とする。

【解決手段】双極型ガラスアンテナ22と、単極型ガラスアンテナ21と、ガラスアンテナ22のアンテナ導体14に電気的に接続されたデフォッガ30とを備える車両用窓ガラスであって、デフォッガ30とガラスアンテナ21のアース側給電部17との間に流れる漏洩信号を濾波するフィルタ装置10が、インピーダンスが極大となる共振点を第1の周波数帯に有し、該第1の周波数帯より高域の第2の周波数帯のインピーダンスが、該第1の周波数帯の前記インピーダンスに比べて低い、車両用窓ガラス。

(もっと読む)

インピーダンス回路および信号変換のための方法

インピーダンス回路(10)は、入力端子(11)、第1の容量性装置(12)、および第2の容量性装置(13)、さらには第1の容量性装置(12)および第2の容量性装置(13)を備える回路網(17、21)によって入力端子(11)に接続されている出力端子(14)を備える。第1の容量性装置(12)は、バラクタ(41)を有するバラクタ回路(40)および少なくとも1つの直列回路(47、48、49)を備える。少なくとも1つの直列回路(48、48、49)は、直列接続されたコンデンサ(50、52、54)およびスイッチ(51、53、55)を備え、バラクタ回路(40)と並列に接続される。第2の容量性装置(13)は、追加のコンデンサ(15)を備える。 (もっと読む)

フィルタ装置

フィルタ装置は基板(302)と基板の第1表面に設けられた複数の水平ギャップ閉鎖アクチュエータ(GCA)装置とを有する。複数のGCA装置は1つ以上のGCAバラクタ(700)を有する。複数の水平GCA装置の各々は、少なくとも1つのドライブくし形構造(602a、602b、702a、702b)と、少なくとも1つの入力/出力(I/O)くし形構造(616a、616b、716a、716b)と、ドライブくし形構造及びI/Oくし形構造に互いに入り込んだ少なくとも1つのトラスくし形構造(604、704)とを有する。トラスくし形構造は、トラスくし形構造及びドライブくし形構造の間に印加されるバイアス電圧に基づいて、少なくとも第1の嵌合位置及び第2の嵌合位置の間の移動軸方向に沿って動くように形成されている。  (もっと読む)

(もっと読む)

鉄ベース・コアを有するフィルタ回路

【課題】約1〜1000kHzの周波数範囲で実質的に一定の透磁率を有するコアを備えたチョークを含むフィルタ回路の提供。

【解決手段】フィルタ回路は、DSL通信システムにおいて通信チャンネル上のデジタル信号及びアナログ信号の周波数バンドを選択するために使用される。フィルタ回路は、実質的に鉄ベースのアモルファス金属合金を含むコアを有するインダクタを含む。有利には、フィルタ回路はコバルトベースのコアを使用するフィルタ回路と同じかもしくはそれ以上の性能を提供するが、非常に低価格である。従って、低コストで高効率な解決をDSL及びそれと同等のものなどの通信アプリケーションに提供する。

(もっと読む)

積層型誘電体フィルタ

【課題】 各インダクタ素子の経路長ずれを抑制し、減衰特性を等しくする。

【解決手段】 複数の誘電体層25(100b)が積層されて誘電体層間にインダクタ素子を構成する複数のインダクタパターンP5〜P8が形成されており、1つの側面にインダクタ素子の一方の端部が露出している積層体と、積層体の側面に積層方向に帯状に等間隔で形成された端子電極17〜20とを具備し、インダクタパターンP5〜P8は等間隔に並んで形成され、インダクタパターン中心線1〜4と端子電極中心線5〜8とのずれ量9〜12が誘電体層中心線28から遠いインダクタパターンP5〜P8におけるほど大きく、インダクタパターンP5〜P8は誘電体層中心線28を対称軸として線対称のパターンである積層型誘電体フィルタである。各インダクタ素子の経路長のずれを抑制することが可能となるので、各インダクタ素子の減衰特性のずれを抑制することが可能となる。

(もっと読む)

信号等化器

【課題】インピーダンス不整合によって発生する反射を抑制して伝送特性の劣化を防止することで、広い周波数帯域で使用可能な信号等化器を得る。

【解決手段】送信端1と受信端2との間を接続して信号を伝送する主伝送線路20と、主伝送線路20の受信端2側に、受信端2と並列に接続された受信側終端抵抗50と、受信側終端抵抗50と並列に接続され、伝送線路61および伝送線路61とインピーダンスが異なる終端抵抗62の直列回路からなり、所望の周波数帯域以外の帯域の信号を減衰させる周波数特性調整回路60と、主伝送線路20と受信端2との間に直列に接続され、自身の入力インピーダンスと主伝送線路20の特性インピーダンスとを整合させる整合抵抗30とを備える。

(もっと読む)

積層型誘電体フィルタ

【課題】 デジタル機器内部の信号ラインのノイズを低減するための、安定した特性の積層型誘電体フィルタを提供する。

【解決手段】 誘電体層1a〜1iが積層された、第1側面2および第2側面3を有する積層体1と、第1側面2に形成された接地端子30と、第1側面2の接地端子30の両側に接地端子30との間にそれぞれ静電容量を有するように近接して形成された2つの第1端子21a,22aと、第2側面2に形成された2つの第2端子21b,22bと、積層体1の内部に形成された、接地端子30と第1端子21a,22aとの間に容量素子C1,C2が配置されている2つのフィルタ回路F1,F2とを具備している積層型誘電体フィルタ10である。接地端子30および2つの第1端子21a,22aのそれぞれの間隔を正確に設定して容量を安定して付加できるので、ノイズに対する減衰特性が高い、安定した減衰特性を有する積層型誘電体フィルタ10を供給することができる。

(もっと読む)

ハイブリッド・カプラとのインピーダンス整合が改善されたフィルタ

本発明は、テレビジョン信号分配システムにおいて装置間通信に使用される周波数の信号が信号源と干渉するのを防止する帯域除去フィルタに関する。このフィルタは、信号スプリッタと協働し、従来の帯域除去フィルタによって生じるスプリッタを介した装置間通信への悪影響を低減するように設計されている。このフィルタは、主に並列共振回路の動作によってスプリッタに給電するポートに抵抗負荷および高い出力インピーダンスを与えるセクションを帯域除去フィルタに追加したものである。

(もっと読む)

(もっと読む)

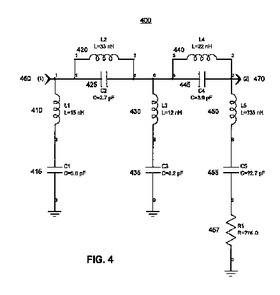

ローパスフィルタ

【課題】 工程の簡素化を図ると共に、通過域を広げ、かつ減衰傾度の大きい高性能なローパスフィルタの提供を目的とする。

【解決手段】 ローパスフィルタは、表面を拡面化処理しない弁作用金属からなる陽極体1を用い、カットオフ周波数から算出される電気長がそれぞれ異なる複数の二端子型固体電解コンデンサ30a、30bを並列接続し、外装樹脂でモールド成形した構造であり、各々の二端子型固体電解コンデンサ30a、30bの陰極部7の長さLa、Lbはそれぞれの電気長の1/4とする。

(もっと読む)

ノイズ抑制回路

【課題】負荷装置に伝播するノイズを特に低減するノイズ抑制回路を提供する。

【解決手段】信号を出力する第一の装置D1およびその信号が入力する第二の装置D2との間に設けられた第一および第二の導電線E1,E2を伝播するノイズを抑制するための回路であって、第一の導電線E1には、第一の分岐点P1と第二の分岐点P2との間に第一の巻線L1、およびこの第一の巻線L1と第二の分岐点P2との間に第二の巻線L2が設けられ、第一の連絡導電線B1には、第一の巻線L1に電磁結合された第三の巻線L3、およびこの第三の巻線L3と第一の分岐点P1との間に第一の逆相信号伝送手段C1が設けられ、第二の連絡導電線B2には、第二の巻線L2に電磁結合された第四の巻線L4、およびこの第四の巻線L4と第二の分岐点P2との間に第二の逆相信号伝送手段C2が設けられる。

(もっと読む)

電気素子およびその製造方法

【課題】従来の伝送線路型ノイズフィルタよりもインダクタンスを低減可能な電気素子を提供する。

【解決手段】電気素子100は、陽極電極10,20と、陰極電極30と、導体板41,42,51,52とを備える。陽極電極10は、電気素子100の長さ方向DR1において導体板41,42の一方端に接続され、陽極電極20は、電気素子100の長さ方向DR1において導体板41,42の他方端に接続される。陰極電極30は、電気素子100の幅方向DR2における導体板51,52の両端に接続される。そして、電気素子100の全長から陽極電極10,20および陰極電極30の長さを減算した減算結果を電気素子100の全長で除算した値は、従来の電気素子の全長から陽極電極および陰極電極の長さを減算した減算結果を従来の電気素子の全長で除算した値よりも小さい値に設定される。

(もっと読む)

コモンモードフィルタ及びその実装構造

【課題】GHz帯のコモンモードノイズを抑制する効果が高いコモンモードフィルタを提供する。

【解決手段】コモンモードフィルタ100は、第1及び第2のセラミック基体11a、11bと、第1のセラミック基体11aと第2のセラミック基体11bに挟まれた機能層12とを備えている。機能層12は、互いに磁気結合した積層方向に重なる2つのコイル導体17,18を含み、第2のセラミック基体11bからコイル導体17,18までの最短距離は、第1のセラミック基体11aからコイル導体17,18までの最短距離よりも短い。第1のセラミック基体11aは焼結フェライト、複合フェライト等の磁性材料からなる。一方、第2のセラミック基体11bはアルミナ等の低誘電率材料からなり、第1のセラミック基体11aと共に機能層12を物理的に保護すると共に、機能層12内のコイル導体間の浮遊容量を低減する役割を果たす。

(もっと読む)

アイソレーション回路

【課題】高周波域の信号を伝送する際に、一方の電子回路部品が接続されたグランドと他方の電子回路部品が接続されたグランドとを完全に分離することができ、しかも、高周波域の信号だけでなく、低周波域の信号をも伝送することができるアイソレーション回路を提供する。

【解決手段】アナログ・デジタルコンバータ110とFPGA120が基板10に実装されている。アイソレーション回路1は、このようなアナログ・デジタルコンバータ110とFPGA120との間に構成されている。アイソレーション回路1は、別々のグランド層11,12を電気的に分離する回路であり、トランス2とフェライトビーズ3−1,3−2とを備えている。トランス2は、高周波のデジタル信号のみを透過させるためのトランスであり、フェライトビーズ3−1,3−2は、低周波のデジタル信号のみを透過させるためのフェライトビーズである。

(もっと読む)

積層型電子部品

【課題】互いに磁気的に負に結合するコイル間の磁気的な結合係数を適切な大きさにすると共に、形状を小型化する。

【解決手段】絶縁体層11A〜11Nとコイル用導体パターン12A〜12D、13A〜13Dを積層し、コイル用導体パターンによって内部にコイルが形成された第1のコイル部、絶縁体層とコイル用導体パターンを積層し、コイル用導体パターンによって内部にコイルが形成された第2のコイル部及び、第1のコイル部と第2のコイル部間に配置された磁気結合用窓Hを有する電極を積み重ねて積層体が形成され、第1のコイル部と第2のコイル部間に配置された電極は磁気的結合用窓Hに連なるスリットSが形成される。第1のコイル部のコイルと第2のコイル部のコイルは、磁気的に負に結合させる。

(もっと読む)

21 - 40 / 139

[ Back to top ]