Fターム[5J039KK13]の内容

Fターム[5J039KK13]に分類される特許

301 - 320 / 417

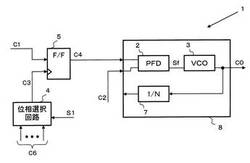

位相調整回路装置及びタイミング調整回路システム

【課題】 所定の入力信号または出力信号について製造バラツキや電源電圧や温度変化の影響を少なくし、適切なタイミングでの動作を実現する位相調整回路装置を提供する。

【解決手段】 2つの入力クロック信号の位相差に応じた電圧の位相差検出信号を出力する位相比較回路2と位相差検出信号Sfの電圧値に応じた周波数で発振する基準クロック信号C0を出力する電圧制御発振回路3を有する位相同期回路8、位相の異なる複数のクロック信号C6の1つを選択して位相調整用の参照クロック信号C3として出力する位相選択回路4、及び、第1入力クロック信号C1の信号レベルの変化タイミングを参照クロック信号C3の立ち上がりまたは立ち下がりタイミングに合わせる位相調整を行うフリップフロップ回路5を備え、位相調整後の第1入力クロック信号C4と基準クロック信号C0が外部回路を経由して得られる遅延クロック信号C2を位相比較回路2に入力する。

(もっと読む)

半導体集積回路および半導体集積回路設計方法

【課題】設計期間を短縮化でき、半導体集積回路内の電源ノイズおよび製品のEMI問題を軽減できること。

【解決手段】階層化されたブロック間のインターフェースを、クロックとデータを同時に送るソースシンクロナスタイプにする。受信側ブロック22の受信器24にメソクロナスタイプの同期化回路を構成するクロック位相検出器27と、VDL28を備え、ブロック間インターフェースのデータをセットアップ/ホールド違反なしに受信し、受信側ブロック22の内部回路に転送する。

(もっと読む)

信号伝達回路

【課題】この発明は、信号伝達回路に関し、ディジタル信号を、ジッタを生じさせることなく遅延経路の後段まで伝達させることを目的とする。

【解決手段】入力端子12の後段に、セットパルス伝達回路14とリセットパルス伝達回路16を配置する。セットパルス伝達回路14は、狭パルス生成回路18、遅延調整回路20、インバータ22、及び狭パルス生成回路24を備える。リセットパルス伝達回路16は、インバータ26、狭パルス生成回路28、遅延調整回路30、インバータ32、及び狭パルス生成回路34を備える。狭パルス生成回路18,24,28,34は、アップエッジを受けて所定幅の狭パルスを発生する。狭パルス生成回路24,34の出力は、それぞれ、SRラッチ36のセット端子及びリセット端子に供給される。

(もっと読む)

クロック遅延補正回路

【課題】クロック分配回路のクロック遅延を補正するクロック遅延補正回路で固定遅延手段を除き、設計時における設計検証を容易にする。

【解決手段】クロック遅延補正回路10は、分配クロックCLKの周期を示す周期データを生成する周期データ生成手段11と、可変遅延時間を持ち分配クロックCLKを遅延して出力クロックCOUT1を生成する可変遅延回路121と、出力クロックCOUT1の位相と基準クロックCREF1の位相とを比較する位相比較回路122と、位相比較回路122の比較結果に従ってカウントUPするカウンタ123とを有し、カウンタ123のカウント値で可変遅延回路121の遅延時間を制御する。

(もっと読む)

位相比較器

【課題】フルレートとハーフレートの両方に対応した位相比較器を得る。

【解決手段】データ信号の立ち下がりタイミングでクロック信号の振幅値を検出する第一の検出手段1と、データ信号の立ち上がりタイミングでクロック信号の振幅値を検出する第二の検出手段2と、第一の検出手段1がクロック信号の立ち上がり状態又は立ち下がり状態の振幅値を検出しているのかを識別して第一の識別結果を出力し、第二の検出手段2がクロック信号の立ち上がり状態又は立ち下がり状態の振幅値を検出しているのかを識別して第二の識別結果を出力するエッジ比較手段3と、第一の識別結果に応じて第一の検出手段1の出力の極性を反転する第一の極性反転手段4と、第二の識別結果に応じて第二の検出手段2の出力の極性を反転する第二の極性反転手段5と、データ信号の極性に応じて第一又は第二の極性反転手段4、5の出力値を選択して出力する信号選択手段6とを設けた。

(もっと読む)

レシーバ回路及びレシーバ回路試験方法

【課題】 レシーバ回路の速度試験をドライバ回路の接続無しに行えるようにすること。

【解決手段】 遅延部3は遅延制御信号に応答してクロック入力信号の位相を遅延制御して出力する。セレクタ2は、実速度試験時、遅延部3からのクロック入力信号と外部端子からの入力信号の中から前記クロック入力信号を選択して出力する。シリアルパラレル変換器4は、サンプリングクロック信号に基づいてセレクタ2から出力された信号をサンプリングし、シリアル信号をパラレル信号形式に変換して出力する。クロックデータリカバリ回路5は、変換器4の出力信号7に応じた最適な位相のサンプリングクロック信号を生成して変換器4に供給する。前記サンプリングクロックの位相を制御するための制御コード60をモニタすることで、遅延変化量とコード変化量の相関をとり、実測度試験を行う。

(もっと読む)

スプレッドスペクトラムクロッキングに使われる遅延された高周波クロック信号を発生させる方法、回路、及びシステム

【課題】スプレッドスペクトラムクロッキングに使われる遅延された高周波クロック信号を発生させるための方法、回路、及びシステムを提供する。

【解決手段】スプレッドスペクトラムクロック信号を発生させる方法は、同期システムのためのスプレッドスペクトラムクロック信号を提供するために選択される複数の遅延された高周波クロック信号を提供するために高周波クロック信号を遅延させる段階を含む。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】設計が容易で、プロファイルの変更も簡単に行うことができ、かつ占有面積が小さく発生するジッタの小さいスペクトラム拡散クロックジェネレータを提供する。

【解決手段】所定の単一周波数のクロックを発生するクロック源と、所定周波数の三角波を発生する三角波発生源と、三角波の電圧に応じて、所定の2次関数に従う2次電流を発生し、切替信号に応じて、2次電流の方向を決定する2次電流発生源と、2次電流発生源から出力される2次電流を第1および第2のコントロール電圧に変換する第1および第2の電流電圧変換回路と、第1および第2のコントロール電圧に応じて、クロック源から入力されるクロックの遅延を変え、クロック周波数がクロック毎に変動する第1および第2のクロックを出力する第1および第2の電圧制御ディレイラインと、第1および第2のクロックを切替えてスペクトラム拡散クロックとして出力するセレクタとを備えている。

(もっと読む)

半導体集積回路

【課題】クロック信号のスペクトラムを拡散することによって電磁放射ノイズを低減する方式を採用した半導体集積回路において、電磁放射ノイズのピーク成分をさらに効果的に低減する。

【解決手段】この半導体集積回路は、クロック信号を周波数変調することによって電磁放射ノイズを低減する半導体集積回路であって、所定の周波数を有するクロック信号を周波数変調することにより、第1の変調幅を有する第1の変調クロック信号を生成する第1の変調回路10と、第1の変調クロック信号をさらに周波数変調することにより、第1の変調幅よりも大きい第2の変調幅を有する第2の変調クロック信号を生成する第2の変調回路20とを具備する。

(もっと読む)

半導体記憶装置の同期モード検出回路及び方法

【課題】半導体記憶装置の同期モード検出回路及び方法に関するものであり、クロックが入力されれば同期モード信号をイネーブルにし、クロックが入力されなければ同期モードをディセーブルにすることによって、同期モードと非同期モードとを区分することができる半導体記憶装置の同期モード検出回路及び方法を提供する。

【解決手段】半導体記憶装置の同期モード検出回路は、有効アドレス信号とクロックを組み合わせて基準信号を生成する第1信号組合部と、前記基準信号をラッチする第1ラッチ部と、前記第1ラッチ部の出力信号と前記クロックを組み合わせて検出パルス信号を生成する第2信号組合部と、前記有効アドレス信号のイネーブル有無に応じて前記検出パルス信号の駆動を制御する制御部と、前記制御部の制御により前記検出パルス信号を駆動する駆動部と、前記駆動部で駆動された信号をラッチし、同期モード信号を出力するラッチ部とを含む。

(もっと読む)

スペクトル拡散クロッキング

状態マシン回路を使用して、多重入力クロック信号のそれぞれのクロック信号を選択し、そのような入力クロック信号に応答して、合成クロック信号を生成するクロック合成回路へ供給する、多重化回路を制御することができる。

状態マシン回路の構成は、例えば、合成クロック信号が、スペクトル拡散クロック信号、および/または入力クロック信号のそれぞれの名目周波数よりも大きい名目周波数を有するクロック信号、となるようにすることができる。  (もっと読む)

(もっと読む)

パルス発生回路およびこの回路を用いた電子装置、携帯電話機、パーソナルコンピュータ、ならびに、この回路を用いる情報伝送方法

【課題】簡単な回路で低消費電力にて高周波数帯域のパルスを容易に発生することがで

き、しかも高価な半導体プロセスを使うことなく実現することができるパルス発生回路を

提供すること。

【解決手段】パルス発生回路を、所定段数縦続接続されたインバータ回路101〜109と、これらインバータ回路101〜109にあって1つのインバータ回路の入出力側に

1段置きに接続され、この接続された各段のインバータ回路102,104,106,108の遅延量に相当する時間幅のパルスを発生する複数のNAND回路110〜113と、

これらNAND回路110〜113の出力の論理和を取るNOR回路114とを備えて構

成する。

(もっと読む)

周波数逓倍回路および送信装置

【課題】 本発明は、電子機器において所望のクロック信号を2逓倍する周波数逓倍回路と、その周波数逓倍回路によって生成された2逓倍クロック信号に同期して伝送情報のCMI符号化を行う送信装置とに関し、物理的なサイズが小さく、かつ安価に精度よく2逓倍クロック信号が生成されることを目的とする。

【解決手段】 クロック信号の周期Tの半分に相当する遅延d(=T/2)を前記クロック信号に与え、遅延クロック信号を生成する遅延手段と、前記クロック信号と前記遅延クロック信号との双方の前縁または後縁に同期し、パルス幅が前記周期Tの四分の一であるパルス信号の列を生成するパルス幅調整手段とを備えて構成される。

(もっと読む)

半導体集積回路

【課題】回路規模を大きくすることなく、複数の回路を動作させるための夫々のクロックの位相を容易に制御することが可能な半導体集積回路を提供する。

【解決手段】本発明の半導体集積回路40は、クロックを入力され、クロックの1周期分に相当する同相遅延素子段数CTを求める遅延制御手段41と、遅延制御手段41により求められた同相遅延素子段数CTから、所定量の遅延を発生させる遅延素子の段数DEGOUT1〜DEGOUTnを決定する遅延素子段数決定手段42と、クロックを遅延素子段数決定手段42により決定された遅延素子の段数分遅延させる遅延クロック生成手段431〜43nとを有する

(もっと読む)

パルス位相差符号化回路

【課題】入力される電圧信号のレベルが回路の動作電源電圧より上昇した場合でも、正確な符号化動作を行うことができるパルス位相差符号化回路を提供する。

【解決手段】A/D変換回路11を構成するパルス位相差符号化回路13において、カウンタ2のカウント値をデータラッチ回路4にラッチさせるタイミング信号を生成するため、符号化周期信号PBに所定の遅延時間T12を付与する遅延回路12を、電圧入力端子に与えられる電圧信号Vinのレベルが上昇するのに応じて遅延時間が短縮されるように構成する。具体的には、遅延回路12を、リングディレイライン1を構成するNOTゲートと同じNOTゲートを、リングディレイライン1を構成する直列段数の1/2となる段数で直列接続して構成し、それらのNOTゲートを、A/D変換対象となる入力電圧Vinを電源として動作させる。

(もっと読む)

デジタル逓倍回路、スイッチング制御回路及び昇降圧DC−DCコンバータ

【課題】逓倍クロックを適切に生成する。

【解決手段】入力された基準クロックを所定の逓倍数逓倍した逓倍クロックを生成出力するデジタル逓倍回路において、発振クロックを前記所定の逓倍数の逆数倍に分周した分周クロックを生成する分周回路と、前記基準クロックの一周期に含まれる前記分周クロックの一周期の数のアップカウントを行うアップカウンタと、前記基準クロックの一周期に相当する前記アップカウントを行った結果であるアップカウント値を基準としてダウンカウントを行っていき、前記ダウンカウントを行っていった際のダウンカウント値がゼロとなるときにパルスを生成することによって、前記パルスを、前記基準クロックを前記所定の逓倍数逓倍した前記逓倍クロックとして出力するダウンカウンタと、を有する。

(もっと読む)

位相制御回路

【課題】経時変化や温度変化に拘らず、常に最適なタイミングの調整をすることが可能な位相制御回路を実現する。

【解決手段】位相を制御する位相制御回路において、クロック信号を遅延する可変遅延回路と、遅延されたクロック信号がクロック入力端子に入力され、データ信号がデータ入力端子に入力される第1のフリップフロップ回路と、データ信号がクロック入力端子に入力され、遅延されたクロック信号がデータ入力端子に入力される第2のフリップフロップ回路と、第2のフリップフロップ回路の出力信号に基づいて可変遅延回路の遅延量を制御する積分回路とを備える。

(もっと読む)

コンパレータ回路およびその制御方法

【課題】比較入力信号の変化の傾きが小さな場合であっても、発振などせず安定した波形を出力し、比較入力信号の増減の方向に係わらず一定の閾値で比較入力信号の大小判定を行なうコンパレータ回路を提供する。

【解決手段】コンパレータ回路100は、比較入力信号INおよび参照入力信号REFの電位差に応じて充放電される容量素子4と、その電圧が閾値電圧Vth以上の場合にはハイレベルを出力し、閾値電圧Vth未満の場合にはローレベルを出力するアナログバッファ部5と、アナログバッファ部5の立ち上がりおよび立ち下がりエッジを検出してアップ信号UPおよびダウン信号DOWNを出力するエッジ検出部7と、アップ信号UPに応じて容量部を充電し、ダウン信号DOWNに応じて容量部を放電するチャージポンプ部8とを備えている。

(もっと読む)

クロック生成回路

【課題】逓倍回路から正確な逓倍クロックが出力されず、温度等の変動に対する補正能力が低下し、ロックが困難になるという課題があった。

【解決手段】互いに直列に接続された複数個の遅延素子から構成されるデジタルディレイライン56,69,71を有し、デジタルディレイライン56,69,71に対応したカウンタ52,65から出力されるカウント値に応じて複数の遅延素子のいずれかの遅延を選択し、選択した遅延素子およびこれに隣接する1つの遅延素子によって遅延時間を設定制御する。

(もっと読む)

クロック信号を生成する電気回路および方法

サンプリング装置(31)のためのクロックサンプリング信号(CLK)を生成するための電気回路(30)は、複数のクロック信号(21〜24、51〜54、61〜64)を生成するためのクロックジェネレータ(1、40、50、60)と、デジタル信号(DS)の特徴的な信号部分(LE)と複数のクロック信号(21、22、23、24、51〜56、61〜64)を相関させる相関装置(L)と、および相関装置(L)による相関に基づいて、クロック信号(21、22、23、24、51〜55、61〜64)のうちの1つを、クロックサンプリング装置のためのクロックサンプリング信号(CLK)として、選択する選択装置(MX)を備える。クロック信号(21〜24、51〜54、61〜64)は、同じサイクル周期(T)を有し、互いに位相シフトする。サンプリング装置(31)は、その後、クロックサンプリング信号(CLK)によってデジタル信号(DS)をサンプリングする。  (もっと読む)

(もっと読む)

301 - 320 / 417

[ Back to top ]