Fターム[5J039KK13]の内容

Fターム[5J039KK13]に分類される特許

341 - 360 / 417

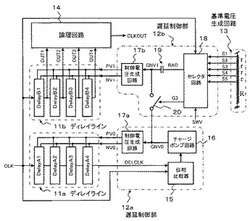

周波数逓倍回路

【課題】 ディレイラインによるPLL技術を用いた周波数逓倍回路におけるEMIノイズを抑制する。

【解決手段】 本発明の周波数逓倍回路は、電圧制御遅延回路(Delay)と、N個のDelayにCLKが入力され、CLKを位相遅延させてDELCLKを生成するディレイライン11aと、位相ロック状態において所定の電圧をGNV0に出力する遅延制御回路12aと、N個のDelayにCLKが入力され、当該Delayの各出力から異なる位相遅延量を持つN個の出力クロック信号(OUTn)を生成するディレイライン11bと、GNV0および複数の異なる基準電圧Snに基づいて、ディレイライン11bの位相遅延量を電圧制御する遅延制御回路12bと、OUTnを論理演算し、周波数がCLKの略N/2倍であるCLKOUTを生成する論理回路14を有する。

(もっと読む)

位相同期ループ回路及び位相同期方法

【課題】 電源電圧のレベルが低くなっても高周波数の多様なクロック信号を発生することが可能な位相同期ループ及び方法を提供すること。

【解決手段】 位相同期ループ回路は外部クロック信号と帰還クロック信号を受信し、外部クロック信号の位相が帰還クロック信号の位相より先行するとアップ信号を発生し、外部クロック信号の位相が帰還クロック信号の位相より遅れるとダウン信号を発生する位相検出器と、アップ信号に応答して制御電圧が増加し、ダウン信号に応答して制御電圧を減少するループフィルタ回路と、制御電圧を受信してn(nは4以上の整数)個の内部クロック信号を直接発生する電圧制御発振器回路とを含むこともできる。また、位相同期ループ回路は少なくとも4個のループを含み制御電圧を受信して複数の内部クロック信号を発生する電圧制御発振器回路も含むことができる。

(もっと読む)

位相同期ループ回路での周波数検出器及び周波数エラーの検出方法

【課題】 位相同期ループ回路において周波数エラーを高速で検出できる周波数検出器及び周波数エラーの検出方法を提供する。

【解決手段】 予測されたランレングス信号の予測分布度に基づいて、周波数検出周期の間にサンプルされたRF信号からランレングス信号を検出するランレングス信号検出ユニットと、周波数検出周期の間に、検出されたランレングス信号をカウントする少なくとも一つのカウンタを備えたカウンタユニットと、サンプルされたRF信号のパッシングエッジをカウントして、周波数検出周期を制御するエッジカウンタと、カウンタユニットに含まれたカウンタによりカウントされた値及び所定の基準値を利用して、周波数検出周期の間の周波数エラーを生成する周波数エラー生成ユニットとを備える。

(もっと読む)

タイミング感知用回路のための方法及びシステム

【課題】異なる駆動強度を提供しながら、実質的に等しい伝播遅延を有する回路に対するシステム及び方法を開示する。

【解決手段】これらシステム及び方法によって、回路は、随意選択的な強度のフル駆動強度回路において、ある比率の駆動強度を有する。さらに、これら回路は、ベースライン駆動回路に対して、実質的に同一の入力キャパシタンス及びフィードバック電流を有する。このような回路の入力は3つのノードに結合される。その1つは、駆動される論理装置に結合された論理回路であり、2つ目はダミー論理装置であり、3つ目は出力が浮遊状態に置かれている論理回路である。

(もっと読む)

構造化されたASICデバイスのためのクロック信号ネットワーク

【課題】クロック信号の好適な分配を行うことができる構造化されたASICデバイスを提供する。

【解決手段】構造化されたASIC(10)デバイスのクロック分配回路構成(200)は、決定性(deterministic)の部分および複数の設定可能な部分を含む。その決定性の部分は、コンダクタ(40)セグメントの所定の配置を用い、デバイス上の複数の所定のロケーションへ、クロック信号を分配するために、回路をバッファする。それぞれの所定のロケーションから、クロック分配回路構成の関連される設定可能な部分は、そのクロック信号を、その所定のロケーションから提供された、構造化されたASIC(10)の所定の領域においてそのクロック信号を必要とする任意のクロック利用回路構成に分配する。

(もっと読む)

差動−シングル変換回路

【課題】差動入力信号を論理ゲートによりパルス信号へ変換し出力する差動−シングル変換回路において、論理ゲートの閾値電圧の変動に影響されること無く、差動信号を安定したパルス信号に変換することを目的とする。

【解決手段】エッジ検出器3により、差動信号INを2値レベル信号に変換した信号N3と、反転させた差動信号/INを2値レベル信号に変換した信号N4との立ち上がりエッジを検出し、RSフリップフロップ4により、信号N3、N4の変化を記憶するようにしたことで、DUTY比が一定な出力信号OUTを生成することができる。

(もっと読む)

複数の回路にタイミング信号を提供するための方法及び装置、集積回路並びにノード

各回路がノードによって給電される複数の電気回路又は光回路間でタイミング信号を提供又は移送する方法。複数のノードはタイミング信号を互いに転送し合い、少なくとも1つのノードは、少なくとも2つのノードからタイミング信号を受信するまでタイミング信号を送信しないように適合化される。このようにして、ノードと回路間のタイミングのスキューの方向が知られ、回路間のデータ移送はより容易になる。  (もっと読む)

(もっと読む)

信号発生装置および方法

【課題】基準クロック信号に従ってデジタル値のシーケンスを生成することのできる信号発生器を提供する。

【解決手段】本発明の一実施形態によれば、基準クロック信号に従ってデジタル値のシーケンスを生成する信号発生器3が提供される。この信号発生器3は、インクリメント信号INC及びオフセット信号Φ1、Φ2を受け取る少なくとも1つの入力端子32、33、34と、オフセット信号Φとインクリメント信号INCに基づいてカウンタ開始値を決定するようになっている開始値回路302と、開始値に設定されるようになっており、基準クロック信号の各サイクルにおいて、規定の値が達成されるまで、カウンタの位置をインクリメント信号INCに従って新しい値に変更するようになっているカウンタと、カウンタ値を出力する出力端子とを備える。

(もっと読む)

アナログデジタルコンバータ

【課題】V−F変換を利用したADコンバータであって、変換周波数を高めることなく、高精度にAD変換を行うことが可能なものを実現する。

【解決手段】二本のVCOを設け、両VCOの周期差を利用して主VCOの周期未満のV−F変換値を求める。BASE−VCO1から出力されるパルス信号のパルス数をカウンタ4にて計数することにより、デジタル信号の上位ビットを生成する。一方、下位ビットについては、第3レジスタ10並びに第2および第3減算器11,12により、サンプリング周期ごとに、現在のサンプリング信号Psの活性化時点からBASE−VCO1およびJAW−VCO2の出力の位相一致時点までの間に含まれる、BASE−VCO1の出力のパルス数に基づいて、サンプリング周期内初頭からBASE−VCO1の出力のサンプリング周期内最初のパルス発生までの位相差を算出することにより生成する。

(もっと読む)

半導体集積回路

【課題】 複数の回路ブロックにそれぞれ位相をずらしたクロックを供給する半導体集積回路において、各回路ブロックへ供給する各クロックの位相ずれ量を電源ノイズ波形の周期に基づいて設定することで、位相の異なる電源ノイズ波形を干渉させて電源ノイズを低減させる。

【解決手段】 半導体集積回路(IC)は、4つの回路ブロックBL1〜BL4と、各回路ブロックBL1〜BL4へそれぞれ供給する各クロックA〜クロックDの位相を設定する位相設定回路10を有する。位相設定回路10は、ベースクロックをクロックAとして第1の回路ブロックBL1へ供給し、各外部入力端子A,B,Cに供給される各電圧に基づいて各クロックB,C,Dの位相ずれ量(遅延時間)をそれぞれ設定する。

(もっと読む)

半導体集積回路装置

【課題】 簡単な構成で高逓倍能力を持ち、高速応答を実現したクロック生成回路を備えた半導体集積回路装置を提供する。

【解決手段】 遅延回路の各段遅延信号をゲート手段で選択し初段側に帰還してリングオシレータを構成する。デコーダにより1つのゲート手段の選択信号を形成して上記ゲート手段を制御する。基準周波数信号の1周期間での上記リングオシレータの発振出力のカウンタ出力とX倍指定値との比較結果により第1レジスタで上記デコーダの入力信号を形成する。第1動作モードで上記制御回路の代表比較結果に対応してバイナリスキャンにより上記入力信号を形成する。第2動作モードでは、上記比較結果により上記入力信号に対して+1又は−1とする。

(もっと読む)

パルス幅変調回路及び多相クロック生成回路

【課題】

周波数の微調整を行うことが可能なパルス幅変調回路及び多相クロック生成回路を提供すること。

【解決手段】

本発明にかかるパルス幅変調回路は、基準クロックに基づいて多相クロック信号を生成する多相クロック生成手段と、入力データと、多相クロック信号とに基づいてパルス幅変調信号を生成するパルス幅変調信号生成手段とを備えたパルス幅変調回路であって、多相クロック生成手段は、位相ロックループ回路を有し、多相クロック信号のうち任意のクロック信号を選択し、帰還クロックとして前記位相ロックループ回路に出力するパルス幅変調回路である。このような構成によれば、多相クロック生成回路の生成する多相クロックのクロック周波数が変更可能となり、クロック周波数及びパルス周波数の微調整を行うことが可能となる。

(もっと読む)

波形グリッチ防止方法

本発明におけるシステム開発目的は、発止させるパルス列の位相をグリッチやスプリアスパルスやデューティサイクルのスプリアス的変化なしで任意に変化させられるようにすることにある。この目的を達成すべく、本ゲート済周期波形発生システムにおいては、可調位相周期波形を発生させる発生器と、この周期波形の位相に基づき遅延イネーブル信号を提供するデバイスと、遅延イネーブル信号及び可調位相周期波形に基づきゲート済周期波形を発生させる論理素子と、を設け、遅延イネーブル信号によりゲート済周期波形をその不要変化なしで発止可能としている。  (もっと読む)

(もっと読む)

デジタル制御型位相合成回路システム

【課題】 ジッタ耐性を強化し、かつロックレンジを拡大するデジタル制御型位相合成回路システムを得る。

【解決手段】 位相の異なる2つのクロックと制御信号が入力され、制御信号による重み付けに基づいて、これらのクロックの中間の位相をもつ出力クロックを合成する位相合成回路と、出力クロックの位相と基準クロックの位相とを比較するバイナリ型位相比較回路と、バイナリ型位相比較回路による比較結果に基づいて第1のカウント値をカウントアップ又はカウントダウンし、第1のカウント値の最上位ビットの値を出力し、第1のカウント値にキャリー又はボローが発生した場合にクロックパルスを出力する第1のアップダウンカウンタと、クロックパルスを動作クロックとし、第1のカウント値の最上位ビットに基づいて第2のカウント値をカウントアップ又はカウントダウンし、第2のカウント値を制御信号として出力する第2のアップダウンカウンタとを有する。

(もっと読む)

振幅検出回路、振幅検出方法及び光通信装置

【課題】 ピーク検出に必要なキャパシタを用いることなく時定数を大幅に小さくできる振幅検出回路を実現する。

【解決手段】 aに示す入力信号(入力in)を折り返してbに示す折り返し信号を得る。この折り返し信号波形は、入力inのハイからロウ、ロウからハイへの遷移点で入力の立ち上がり・立下り時間のためへこみqが生じており、検出した振幅値に誤差が生じる。一方、入力inを微分してcに示す微分波形を得、さらにこれを折り返してdに示す折り返し信号を得る。次に、bとdとを加算することにより、へこみqがdにより補正され、ピーク値Pに示すような入力inのピーク値に対応する平坦な出力を得ることができる。即ち、キャパシタを用いないで入力inの振幅を検出することができる。

(もっと読む)

半導体集積回路

【課題】 待機モードから通常モードに速やかに復帰することができる半導体集積回路における上記待機モードでの消費電力の低減を図る。

【解決手段】 自走モードと逓倍モードとを備えたクロック生成回路(10)と、上記クロック生成回路によって生成されたクロック信号に同期動作可能な内部回路(40)と、基準クロック信号を生成する発振回路(30)と、通常モードと待機モードとの切り換えを制御可能な動作モード制御回路(20)とを設ける。上記発振回路の発振動作が安定する前に上記自走モードによるクロック信号が生成されることにより、これに同期して内部回路が通常モードで動作することができ、待機モードから通常モードへの復帰時間が短縮される。そして上記待機モードにおいては、上記発振回路の上記発振動作が停止されることで消費電力が低減される。

(もっと読む)

半導体集積回路

【課題】 クロックスキューを低減し、動作マージンを十分に確保することが可能な半導体集積回路を提供する。

【解決手段】 遅延回路8による遅延時間DL1とクロックツリー11による遅延時間DL11との和が、遅延回路9による遅延時間DL2とクロックツリー12による遅延時間DL12との和と等しくなるように、遅延回路8,9の遅延時間DL1,DL2が調整される。このように、予め任意に遅延時間をプログラムすることができるプログラマブル遅延回路8,9を設けたことによって、機能ブロック3,4に供給される内部電源電圧V1,V2の差が大きい場合でも、機能ブロック3,4間のクロックスキューを低減することができる。したがって、低消費電力の半導体集積回路において、クロックスキューを低減することができ、動作マージンを十分に確保することが可能になる。

(もっと読む)

バスレシーバ回路及び該バスレシーバ回路に用いられるノイズ除去方法

【課題】

多数の負荷が接続されているバス線からバス信号を受け取るバスレシーバ回路の対ノイズ特性を確保する。

【解決手段】信号変化検出部20により、バス信号bの1/2周期毎に、当該1/2周期の前端以降の最初の変化が検出されると同時に、ホールド回路40により、同バス信号bの電圧レベルに対応した論理レベルがホールドされ、同1/2周期の後端に達する直前に同ホールドの解除が行われる。このため、バス信号bの1/2周期毎に当該1/2周期の前端よりも後かつ後端よりも前の期間に同バス信号bに含まれているノイズ(すなわち、正規の変化タイミング以外で発生するノイズ)が除去され、フリップフロップ60に正しいバス信号jが取り込まれる。

(もっと読む)

遅延回路、およびそれを含む電子回路

【課題】 オペアンプや遅延回路を含むシステムの動作速度を変更するには、オペアンプや遅延回路を個別に再設計する必要があった。

【解決手段】 オペアンプ42は、所定の固定電圧および所定のバイアス電圧を受けて動作する。遅延回路10は、所定の固定電圧および所定のバイアス電圧を受けて、内部を流れる電流の変動を抑制しながら動作する。クロック生成回路20は、遅延回路10にて遅延される前の信号と、遅延回路10にて遅延された信号を基に、オペアンプ42に供給するクロック信号を生成する。定電圧発生回路30は、オペアンプ42および遅延回路10に供給するバイアス電圧を生成する。

(もっと読む)

集積回路

【課題】 より効果的に不要輻射を抑制できる集積回路を提供することを課題とする。

【解決手段】 各グループの電流使用規模がほぼ均一になるようにそれぞれ1以上の回路ブロックが属する複数の回路グループと、前記回路グループの数と同数の、同一周波数でタイミングの異なるクロックを生成するクロック生成部12とを集積回路に備え、クロック生成部12は、クロック生成部12が生成する各クロックの基となる基本クロックを生成するソースクロック生成部121と、ソースクロック生成部121により生成された基本クロックを1以上の段階に遅延させて、基本クロックと同一周波数でタイミングの異なるクロックを1つ以上生成する遅延回路122とを備え、各回路グループにそれぞれ異なるクロックを供給する。

(もっと読む)

341 - 360 / 417

[ Back to top ]