Fターム[5J039KK13]の内容

Fターム[5J039KK13]に分類される特許

281 - 300 / 417

集積回路電源ノイズ低減方法および集積回路電源ノイズ低減システム

【課題】 集積回路の電源から放出されるノイズを効率良く低減することができる集積回路電源ノイズ低減方法および集積回路電源ノイズ低減システムを提供すること。

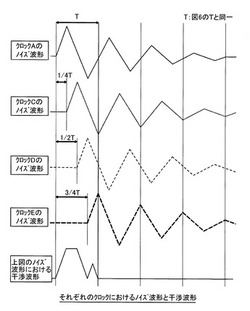

【解決手段】 トランジスタが作動するときの貫通電流によって発生するIC1の電源ノイズを低減する集積回路電源ノイズ低減方法において、前記IC1のベースクロックに対して一定周期単位で位相を遅らせたディレイクロックを複数生成するクロック分散手順と、前記複数のディレイクロックにより動作する回路ブロックを複数の回路ブロック11,12,13,14に分割する回路ブロック分割手順と、各回路ブロック11,12,13,14により生成された位相のずれたノイズ波形と電源ノイズ波形を干渉させて電源ノイズを低減する電源ノイズ低減手順と、を有する。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】入力されるシステムクロック信号と反転されたシステムクロック信号との交差点と、基準信号とが一致するように調整可能な回路を備えた半導体メモリ装置を提供すること。

【解決手段】このため本発明は、システムクロック信号と反転されたシステムクロック信号との交差点を基準とする第1クロック信号を生成する第1クロック入力部と、システムクロック信号と基準信号との交差点を基準とする第2クロック信号を生成する第2クロック入力部と、反転されたシステムクロック信号と基準信号との交差点を基準とする第3クロック信号を生成する第3クロック入力部と、遅延制御信号に対応して第1クロック信号を遅延させ遅延クロック信号として出力する遅延部と、遅延クロック信号と第2クロック信号との位相差又は遅延クロック信号と第3クロック信号との位相差に対応して遅延制御信号を出力するクロック遅延調整部とを備える半導体メモリ装置を提供する。

(もっと読む)

ASIC及び画像形成装置

【課題】 スイッチング電流(過渡的な貫通電流)等による瞬間の過渡電流が、内部配線を流れる事による配線からの電磁波の直接輻射、及びその結果生じる内部電源の電圧降下や、急激な電圧変化によって、その信号がIO出力端子に重畳され出力される事で生じる間接輻射による不要輻射が、無視できないレベルとなってきている。

【解決手段】 エーシック内部のクロックのスキュー調整を分散化させそのエーシックを用いたシステムでエーシックで不要輻射が生じないようにする。特に同一のクロック端子に接続されてその端子からのクロックスキューが互いに異なるブロックを少なくとも2つ以上形成させ互いにクロックオンするタイミングがことならせ少なくとも同じ電源ライン間に複数のブロックにまたがって配置してコンタクトで電源接続されていることを特徴とする。

(もっと読む)

スケルチ検出回路

【課題】温度、プロセス、電源電圧の変動に強く、安定したスケルチ検出信号を出力することができるスケルチ検出回路を提供する。

【解決手段】スケルチ検出回路は、差動信号の電位振幅が、スケルチレベルを超えているかどうかを検出し、その検出信号を出力するピーク検出回路と、検出信号のパルス幅を、そのパルス幅の時間を含めて、差動信号のデータの1周期分の時間以上の時間だけ延長するパルス幅延長回路とを備える。ここで、ピーク検出回路は、差動信号の電位振幅に応じた電位を持つ第1および第2の信号を出力する入力アンプ回路と、入力アンプ回路と同一構成であり、スケルチレベルに相当するリファレンス電圧に応じた電位を持つ第3および第4の信号を出力するレプリカアンプ回路と、第1および第2の信号に応じて流れる合成電流と第3および第4の信号に応じて流れる固定電流とを比較し、その電流差に応じて、差動信号の電位振幅がリファレンス電圧を超えているかどうかを表す検出信号を出力する電流比較回路とを備える。

(もっと読む)

位相比較信号処理回路

【課題】位相比較回路の出力矩形波信号の処理する際に、簡単な回路構成を有し、PLLで引込み可能な周波数幅を拡げ、同期時間を短縮できる位相比較信号処理回路を提供する。

【解決手段】入力矩形波信号を双極性信号に変換する電圧シフタ2、入力矩形波信号のレベル変化時に制御パルス信号を発生する制御パルス信号発生器7、制御パルス信号の到来時に積分値をリセットし、その後双極性信号を積分して積分値を出力する積分回路3、積分値のリセット時のレベル変化分を微分パルスとして出力する微分回路4、制御パルス信号の到来時に微分パルスを出力するゲート回路6、前記保持回路は最新の入力微分パルスレベルを保持し、微分パルスレベルの更新時にその微分パルスレベルが保持されるように保持電圧値が順次変化する保持信号を形成するホールド回路8を備え、この保持信号を次段のループフィルタに供給する。

(もっと読む)

半導体メモリ装置

【課題】半導体メモリ装置の遅延固定クロックの出力において、デューティ比を容易に補正して出力可能な遅延固定回路を備える半導体メモリ装置を提供すること。

【解決手段】このため、本発明は、システムクロックを所定の時間遅延させ、遅延固定クロックを出力する遅延固定回路と、該遅延固定クロックのデューティ比を補正して第1クロックを出力するにあたり、前記第1クロックの第2エッジと、前記第1クロックによって生成された第2クロックの第2エッジとのタイミング差に対応して、前記遅延固定クロックのハイレベル区間とローレベル区間との比を調整するデューティ補正回路と、前記第1クロックの第1エッジと前記第2クロックの第1エッジとの位相を合わせるクロック同期回路とを備える半導体メモリ装置を提供する。

(もっと読む)

半導体装置

【課題】 半導体装置における通常モードと特殊モードとの混載をコストの増大および特殊モードへの誤移行の危険性を回避して実現する。

【解決手段】 短パルス除去回路(11)は、外部制御信号(/CE)について第1所定時間より短いパルス幅の活性パルスおよび非活性パルスを除去して内部制御信号(/CEI)として出力する。短パルス検出回路(12)は、外部制御信号について第1所定時間より短いパルス幅の活性パルスおよび非活性パルスを検出する。内部回路(13)は、通常モードおよび特殊モードを有し、外部制御信号に代えて内部制御信号に応じて動作する。内部回路は、短パルス検出回路による活性パルスの検出に応答して通常モードから特殊モードに移行し、短パルス検出回路による非活性パルスの検出に応答して特殊モードから通常モードに移行する。

(もっと読む)

IC

【課題】外部ピンまでのL成分と、ICを実装した基板上のL成分を介して、IC外部のバイパス・コンデンサによって流れる過渡電流による電圧変動により引き起こされる放射ノイズの低減を目的とする。

【解決手段】同期式のロジック回路において、基準クロックを分周して周波数が同じで位相の異なる動作クロックを生成して、同期式のロジックを複数のブロックに分割して、それぞれのブロックを前記 位相の異なる動作クロックで駆動するシステムであって、各動作クロックは、立ち上がり、立下り、共に重ならない位相とする。

(もっと読む)

半導体装置

【課題】本発明は、システム全体のスループットを低下させることなく、実動作中の回路誤動作(セットアップ違反)を認識することができる半導体装置を提供することを目的とする。

【解決手段】本発明は、第1レジスタR1と、遅延手段B2と、第2レジスタR2と、比較器1とを備える。第1レジスタR1は、論理回路(L1)からのデータをクロック信号の所定のタイミングで取り込む。遅延手段B2は、クロック信号を遅延させる。第2レジスタR2は、第1レジスタR1と論理等価であり、遅延手段B2を経たクロック信号の所定のタイミングで論理回路(L1)からのデータを取り込む。比較器1は、第1レジスタR1の出力Q1と第2レジスタR2の出力Q2との比較を行い、第1エラー信号を出力する。

(もっと読む)

電子回路装置

【課題】パルス幅を意図的に変化させるNRZ等の信号の伝送において、パルス幅のバラツキの低減を図り、さらにジッタの低減も図った電子回路装置を提供する。

【解決手段】2個のエッジ検出回路11,12と、2個の可変遅延回路13,14と、SRラッチ回路15とを備え、可変遅延回路13,14のそれぞれの入力にエッジ検出回路11,12の出力を接続し、SRラッチ回路のS入力およびR入力それぞれに可変遅延回路13,14の出力を接続する。

(もっと読む)

パルス発生回路

【課題】dv/dt過渡信号による誤動作を防止したパワーデバイスの駆動回路を実現する半導体装置において、試験用にオン信号とオフ信号とを同時に発生させることのできるパルス発生回路を実現する。

【解決手段】第1の論理値および上記第1の論理値と排他的関係にある第2の論理値の間でレベル遷移する第1の入力信号が入力され、さらに第2の入力信号または上記第2の入力信号に加えて第3の入力信号も入力され、上記第1の入力信号が上記第1の論理値から上記第2の論理値へとレベル遷移する際に第1のパルス(オン信号)を出力し、上記第1の入力信号が上記第2の論理値から上記第1の論理値へとレベル遷移する際に第2のパルス(オフ信号)を出力し、上記第2または第3の入力信号が入力された場合には、上記第1および第2のパルスを同時に出力する。

(もっと読む)

クロックエッジ復元を有するパルスカウンタ

特定の時間間隔の間に入力パルスをカウントするための装置および方法が提供される。クロックエッジ復元出力信号は、入力ゲート信号および入力パルスを含むクロック信号に応答して生成される。クロックエッジ復元出力信号は、入力ゲート信号がイネーブル状態にある間および入力ゲート信号がイネーブル状態からディスエーブル状態に遷移するときに生じる、クロック信号の入力パルスの、立ち上がりまたは立ち下がりのいずれかのそれぞれに対して、それぞれ完全なクロックパルスを有する。カウンタ回路は、クロックエッジ復元出力信号に含まれるパルスをカウントする。  (もっと読む)

(もっと読む)

複数のメモリのための信号バッファリングおよびリタイミング回路

【課題】複数のメモリ素子のための信号バッファリングおよびリタイミング回路を提供する。

【解決手段】複数のメモリ素子のための信号バッファリングおよびリタイミング(SBR)回路である。PLLをベースとするクロック発生器によって、受け取ったホスト・クロック信号から1組の位相シフト・クロック信号セットが生成される。複数の位相選択器の各々によって、前記1組の位相シフト・クロック信号セットからサブセットの連続クロック信号が個々に選択される。個々のサブセットの連続クロック信号が、異なる組の1つまたは複数のバーニヤに印加され、個々のバーニヤによって、複数の連続クロック信号の中から1つのクロック信号が個々に選択される。SBR回路は、スキューおよび遅延に関連する比較的厳格な信号タイミング要求事項を満足するように設計することができる。

(もっと読む)

クロック発生回路

【課題】クロック逓倍してクロック信号を発生するクロック発生回路のロックインタイムを短縮する。

【解決手段】ロックイン状態において、2つの数値データCi,C(i+1)を積和演算器が出力し、各数値データに従って発振器11の発振周期を設定して、その出力クロック信号のパルス数をカウントして第1および第2のカウント値を生成する。これらの2つの数値データと2つのカウント値と周期目標データとに従って、発振器の発振周期を設定する第3の数値データを生成して、発振器の発振周期を設定する。

(もっと読む)

可変周波数多相発振器

【課題】簡単なデューティサイクル制御と、広い周波数レンジと、簡単な周波数調整構成と、低消費電力を備え、集積回路に組み込まれ、且つ、その集積回路を複雑にすることのない多相出力を有する可変周波数多相発振器を提供する装置および方法を提供すること。

【解決手段】多相信号を供給するための可変周波数多相発振器が開示される。この可変周波数多相発振器は、相関器、複数の遅延セル、およびNOR回路を備える。上記相関器のそれぞれは、電流供給部、キャパシタ、コンパレータ、スイッチ、及び論理ユニットを備える。上記複数の遅延セルは、大きな周波数レンジの範囲内で相が相関性を有する多相信号を発生させる。上記多相信号の周波数とデューティサイクルは調整可能である。

(もっと読む)

EMIノイズを低減した同期回路の設計方法

【課題】 どの場所にどれだけスキューを付けられるかを検証して、消費電流が流れるタイミングを時間軸上で分散させることで、EMIのいずのピークを低減することができる同期回路の設計方法を提供すること。

【解決手段】 本発明に係る同期回路の設計方法は、ネットリストを含む所与の条件を入力して、自動配置配線ツールを用いて同期回路の一次配置配線を実施する第1工程と、配置配線された同期回路のクロックツリーに従って、クロックソースから各末端経路までのクロックの到達時間差であるスキューを解析する第2工程と、解析されたスキューがセットアップ/ホールドタイムに対してマージンを有する複数のモジュールI,II,III,IVに分割する第3工程と、分割された複数のモジュールI,II,III,IVの少なくとも一つにクロックスキュー設定回路10を追加挿入する第4工程と、クロックスキュー設定回路10を追加して、二次配置配線を実施する第5工程と、を有する。

(もっと読む)

電磁干渉を減少させる方法及びクロック管理回路、(コヒーレントな周波数クロックの生成及びノンコヒーレントな位相を用いるスペクトル管理)

【課題】クロック動作回路において電磁干渉を減少させる方法を提供する。

【解決手段】この方法では、クロック回路は、少なくとも第1クロック信号及び第2クロック信号を含む。この方法は、第1クロック信号の第1遷移部が、第2クロック信号の対応する第2遷移部と実質的に合っているときを検出する。この方法は更に、第1遷移部が第2遷移部と実質的に合っている場合、第2クロック信号を所定の時間量だけ遅延する。

(もっと読む)

時間計測回路

【課題】短い時間幅の高分解能な計測と長い時間幅の低分解能な計測とを、回路規模を大幅に増大させることなく、いずれも実現させることが可能な時間計測回路を提供する。

【解決手段】駆動電圧VDDLに応じた遅延時間で信号を遅延させる遅延ユニットDUをM(Mは正整数)段直列接続してなり、起動用パルスPAの入力により起動され、各遅延ユニットDUにてパルス信号を順次遅延させながら伝送するパルス遅延回路10と、計測用パルスPBが入力されると、パルス遅延回路10内でのパルス信号の位置を検出(ラッチ)し、その検出結果を、起動用パルスPAの入力から計測用パルスPBの入力までの時間Tm内にパルス信号が通過した遅延ユニットDUの段数を表す所定ビットのデジタルデータDTに変換して出力するラッチ&エンコーダ12と、電圧設定データDVに従った大きさの駆動電圧VDDLを発生させる駆動電圧設定回路14とを備える。

(もっと読む)

クロック切替回路

【課題】位相が異なるクロックを非同期の切替信号に基づき切り替えても出力クロックに、切り替え時の短パルスが発生しないクロック切替回路を提供すること。

【解決手段】クロック切替回路1は、外部クロックCLKT、CLKBが入力されそれぞれPLL回路2、3と、PLL回路3の出力PLBかPLL回路2の出力PLTの反転信号を選択出力するマルチプレクサ14と、CLKB、PLBとは非同期のLock判定信号12aに基づきマルチプレクサ14を切り替え制御するクロック制御回路13とを有する。クロック制御回路13は、Lock判定信号12aが入力されるとPLBの位相を所定値オフセットさせたオフセットクロックPLQBに同期してマルチプレクサ14の出力を切り替えさせる。

(もっと読む)

クロック供給回路

【課題】 ジッタの低減化が図られたクロック供給回路を提供。

【解決手段】 第1の周波数の第1のクロックで動作する第1の回路ブロック10と、第1のクロックを2逓倍して第2の周波数の第2のクロックを生成する逓倍回路30と、第2の周波数と同一の第3のクロックで動作する第2の回路ブロック20と、第2のクロックと第2の回路ブロック20を経由した第4のクロックの2つのクロックの周波数と位相が一致するようその周波数が制御された第5のクロックを生成するPLL回路40と、第5のクロックを遅延させる遅延回路60からの遅延クロックで動作するモニタ回路23と、第2のクロックとモニタ回路23を経由した第6のクロックとの位相の早遅に応じて第2の回路ブロック20の第1の周波数に同期したジッタを打ち消すようあらかじめジッタが印加された第3のクロックを生成して第2の回路ブロック20に供給するジッタキャンセル回路50とを備えた。

(もっと読む)

281 - 300 / 417

[ Back to top ]