Fターム[5J039KK13]の内容

Fターム[5J039KK13]に分類される特許

81 - 100 / 417

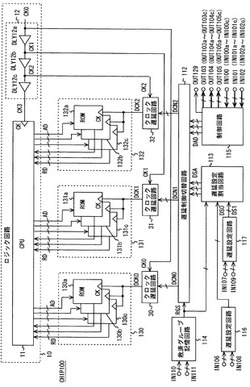

半導体集積回路のクロック遅延調整回路およびその制御方法

【課題】回路規模が増大する問題があった。

【解決手段】複数の回路ブロックと、入力するクロック信号を遅延制御信号に基づいて遅延したクロック信号を対応する前記複数の回路ブロックに供給する複数のクロック遅延回路と、前記複数の回路ブロックの遅延試験を行う制御回路と、前記遅延試験の結果に応じて、前記複数の回路ブロックのうち遅延処理が必要な回路ブロックの情報を記憶する救済グループ記憶回路と、前記遅延試験の結果に応じて、前記複数の回路ブロックのうち遅延処理が必要な回路ブロックの遅延値情報を記憶する、所定数の遅延設定回路と、前記救済グループ記憶回路が記憶した回路ブロックの情報に対応したクロック遅延回路に対し、前記遅延設定回路が記憶した遅延値情報に応じた前記遅延制御信号を割り当てる遅延設定割当制御回路と、を有する半導体集積回路のクロック信号調整回路。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

発振異常検出回路

【課題】発振回路の発振周波数の異常を検出することができる発振異常検出回路を提供することである。

【解決手段】クロック信号CLKを、直列接続された複数の遅延素子20〜25を用いて遅延させる遅延部2と、遅延素子20〜25の出力信号であるクロック信号CLK0〜CLK5から、全体遅延時間tda内における、クロック信号CLKの変化を示す発振信号パターンD0〜D5を取得する信号パターン取得部3と、期待信号パターンE0〜E5を予め記憶する期待値記憶部4と、発振信号パターンD0〜D5と期待信号パターンE0〜E5とを比較する比較部5と、比較部5による比較結果が一致しない場合、発振回路100に発振異常が生じていると判定する異常判定部6とを備えた。

(もっと読む)

多相クロック生成回路

【課題】

位相ノイズが少ない多相クロック生成回路を提供する。

【解決手段】

多相クロック生成回路は,基準クロックを生成する基準クロック生成器と,リング状に接続された複数の遅延回路を有し,前記複数の遅延回路がそれぞれ位相がずれた出力クロックを出力する多相クロック発振器と,前記複数の遅延回路のいずれかの出力端子に前記基準クロックを供給する基準クロック注入回路とを有する。多相クロック発振器のクロックの位相ノイズを低減し周波数変動が抑制できる。

(もっと読む)

クロック異常検出回路

【課題】クロック異常を検出する精度を向上させる技術を提供する。

【解決手段】被検査クロックを遅延させる第1の遅延回路の出力と第2の遅延回路の出力よりLow期間を決める。定められたLow期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。第1の遅延回路の出力と第2の遅延回路の出力よりHigh期間を決める。定められたHigh期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。Low期間の異常とHigh期間の異常を統合する。

(もっと読む)

半導体装置、及びそのテスト方法

【課題】シリアルインタフェース回路におけるCDR回路の位相追従機能を、ループバックテストによって検査する。

【解決手段】本発明による半導体装置において、PLL回路2は、周波数変調された参照クロック1に基づいて、受信用クロック21及び送信用クロック22を生成する。シリアライザ3は、送信用クロック22に応じたタイミングでパラレルデータ33をシリアル化して出力する。CDR回路8は、受信用クロック21に基づいて、受信データ20に対するクロックデータリカバリを実行し、再生データ24を生成する。デシリアライザ14は、再生データ24をパラレル化する。ループバック回線19は、シリアライザ7から出力されたシリアルデータ18を、受信データ20としてCDR回路8に入力する。

(もっと読む)

半導体装置

【課題】半導体装置の回路面積の増大を抑制し、かつクロックジッタを低減できるようにする。

【解決手段】基準クロック信号を動作クロックとして動作する回路ブロックと、基準クロック信号をn分周したクロック信号を動作クロックとして動作する回路ブロックとを有する半導体装置にて、遅延回路により基準クロック信号に所定の遅延を与えて、セレクタが制御信号に応じて基準クロック信号及び遅延が与えられたクロック信号の内から1つのクロック信号を選択して基準クロック信号を動作クロックとして動作する回路ブロックに出力するようにして、電源ノイズにより生じる位相変化を合わせた基準クロック信号の位相変化量を各周期で等しくしてクロックジッタを低減できるようにする。

(もっと読む)

電子回路、電子機器、デジタル信号処理方法

【課題】多相クロックを使用してデジタル信号処理を行なう場合に、クロック信号の各位相関係を正しく保ったまま高速動作が要求される各デジタル信号処理部まで多相クロックを分配できるようにする。

【解決手段】基準タイミング生成部110は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低い基準タイミング信号J0を生成して局所タイミング再生部120に供給する。局所タイミング再生部120は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低いクロック信号であって、高速信号処理部140におけるデジタル信号処理の基準となる複数のクロック信号でなる多相タイミング信号J2を生成して高速信号処理部140に供給する。高速信号処理部140と局所タイミング再生部120を1対1で設け、1つの局所タイミング再生部120から複数の高速信号処理部140へ多相タイミング信号J2を分配しないようにする。

(もっと読む)

遅延時間差測定回路

【課題】本発明の一実施例では、2つの信号間の遅延時間差を信号のエッジに応じて正確に測定する遅延時間差測定回路を提供することを目的とする。

【解決手段】上記課題を解決するため、2本の信号線の伝播遅延時間差を測定する遅延時間差測定回路は、該2本の信号線に接続され、選択信号に応じて一方の信号線を伝播する信号を出力する選択回路と、該選択回路に接続され、該選択回路の出力信号を一定時間遅延させて該選択信号として出力する切替回路と、該選択回路の出力側と該2本の信号線の入力側を接続する帰還経路と、該帰還経路に接続され、該帰還経路を伝播する信号の自己発振周期に基づいて該2本の信号線を伝播する信号の遅延時間の差を算出する制御回路とを有する。

(もっと読む)

遅延回路、及び電子機器

【課題】遅延回路のキャパシタの容量を増大させることなく、外来ノイズの影響による出力電圧の誤動作を防止する。

【解決手段】キャパシタと第1のノードを介して接続され、前記キャパシタを充電または放電する定電流源と、入力電圧が第1のレベルに変化したときに前記キャパシタを放電または充電し、入力電圧が第2のレベルに変化したときに前記キャパシタを充電または放電する充放電回路と、前記キャパシタの充放電の開始から、前記第1のノードの電圧が所定の検知電圧を超えるまでの時間遅延して、出力電圧のレベルを第1のレベルから第2のレベルに変化させる電圧検知回路とを有する遅延回路において、前記入力電圧が第2のレベルであって、かつ前記出力電圧が第2のレベルに変化したときに、前記第1のノードの電圧を前記検知電圧を超えるレベルに保持する電圧保持回路を備えることで出力電圧の誤動作を防止する。

(もっと読む)

位相検出回路および方法

【課題】 相当量の電力を消費し、かつジッタを生成する分周器回路を必要とせずに、高周波周期出力信号を生成する位相ロックループを提供すること。

【解決手段】 位相検出器回路は、第1および第2周期入力信号の位相を比較して、出力信号を生成する。位相検出器は、第1および第2周期入力信号の2つの異なる組み合わせを作り、第3および第4周期信号を生成する回路を備える。この回路は、第3周期信号を、第1相対位相シフトを付与する、第1周期信号および第2周期信号の第1の組み合わせに基づかせる。この回路は、第4周期信号を、第1周期信号および第2周期信号の第2の組み合わせに基づかせて、異なる相対位相シフトを提供する。位相検出器は、また、第3周期信号の電力の大きさを第4周期信号の電力の大きさと比較して、位相比較出力信号を生成する比較回路も備える。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】入力クロックの周波数変化に依存して変調プロファイルが変化しないスペクトラム拡散クロックジェネレータを提供する。

【解決手段】スペクトラム拡散クロックジェネレータは、切替信号に応じて入力クロックを遅延し、出力クロックとして出力する遅延ラインと、入力クロックの周期を計測する入力クロック周期計測部と、入力クロック周期計測部の計測結果に応じて、1変調周期当たりの出力クロックのサイクル数、および、あらかじめ設定された変調度に対応する入力クロックの所定サイクル当たりの出力クロックの周期の変調ステップ幅を算出し、算出されたクロックサイクル数および変調ステップ幅に基づいて切替信号を生成する遅延ライン制御部とを備えている。

(もっと読む)

位相周波数比較器およびシリアル伝送装置

【課題】ループ帯域幅を安定させる位相周波数比較器を簡易な回路で提供する。

【解決手段】基準クロック102とフィードバッククロック103とを入力とし、周波数シンセサイザへのアップ信号と周波数シンセサイザへのダウン信号とを出力する位相周波数比較器において、第1位相周波数比較回路106と、第2位相比較回路107と、前記基準クロック102と前記フィードバッククロック103とを入力とし、前記第1位相周波数比較回路106の入力と前記第2位相比較回路107の入力とに、所定の相対的な遅延を与える遅延回路部108とを備え、周波数比較を前記第1位相周波数比較回路106で行い、位相比較を前記第1位相周波数比較回路106とラッチを制御した前記第2位相比較回路107とで行う位相周波数比較器。

(もっと読む)

送信装置および通信システム

【課題】 従来の送信装置では、クロックとデータとの間のスキューが変動した場合にも高精度の通信を実現することが困難であった。

【解決手段】 N(Nは自然数)ビットの第1のパラレルデータ信号を、基準クロックをN逓倍した第1変換クロックでパラレル/シリアル変換を行い、N×K(Kは自然数)ビットの第2のパラレルデータ信号を、基準クロックをN×K逓倍した第2変換クロックでパラレル/シリアル変換を行う。

(もっと読む)

半導体装置

【課題】半導体装置の外部に出力される信号にハザードが含まれないようにする。

【解決手段】半導体装置において、IOセル23_1は、タイミング調整回路50および出力バッファ70を含む。出力バッファ70は、タイミング調整回路50によってタイミング調整されたデータ信号DOcおよび出力許可信号OEcを受ける。タイミング調整回路50は、出力バッファ70にデータ信号DOcおよび出力許可信号OEcが入力された時点で、出力すべき論理レベルにデータ信号DOcが変化した後に出力許可信号OEcが非活性状態から活性状態に切替わり、かつ、出力すべき論理レベルをデータ信号DOcが保持している間に出力許可信号OEcが活性状態から非活性状態に切替わるように、IOポート論理回路18から受けたデータ信号DOおよび出力許可信号OEの少なくとも一方のタイミングを調整する。

(もっと読む)

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

遅延発生装置および半導体試験装置

【課題】差動ペアトランジスタを用いない比較器を備えた遅延発生装置およびこの遅延発生装置を備えた半導体試験装置を提供することを目的とする。

【解決手段】入力信号に対して設定された時間だけ遅延を持たせるための静電容量を有する遅延部111と比較基準電圧を生成するためのDAコンバータ110と遅延部から出力される出力電圧と比較基準電圧とを比較する比較器1とを備える遅延発生装置であって、比較器1は、比較基準電圧Vthに基づく閾値と出力電圧とを比較して反転するインバータ回路2Aと、インバータ回路2Aの正側電位Vd1を設定する第1の電圧源5と、インバータ回路2Aの負側電位Vs1を設定する第2の電圧源6と、を備えている。

(もっと読む)

半導体集積回路装置、及び電源電圧制御方法

【課題】短時間に電源電圧を最適値に制御することが可能な半導体集積回路装置を提供することである。

【解決手段】本発明にかかる半導体集積回路装置100は、ターゲット回路2と、ターゲット回路2に電源電圧を供給する電圧供給回路4と、電圧供給回路4の出力電圧を制御する制御回路3と、ターゲット回路2に供給される電源電圧の電圧値を予測する目標電圧予測回路1とを備える。制御回路は、ターゲット回路2の要求動作周波数が第1の動作周波数から第2の動作周波数に変化した際に、電圧供給回路4の出力電圧を所定の電圧値だけ変化させる。目標電圧予測回路1は、所定の電圧値の変化にともなうターゲット回路2の動作周波数の変化量を検出すると共に、動作周波数の変化量と所定の電圧値との関係に基づいて目標電圧値を算出する。電圧供給回路4は、ターゲット回路2に目標電圧値の電源電圧を供給する。

(もっと読む)

ノイズ除去装置

【課題】使用環境状況の影響を受けずに、ノイズを確実に除去する。

【解決手段】n個のD型フリップフロップを直列に接続し、各D型フリップフロップの出力した信号の論理積を出力とするデジタル・フィルタ20と、m×2個のプリミティブ素子を有するインバータを直列に接続したディレイ・フィルタ30を並列に接続する。入力信号INPUTを両フィルタに入力し、AND回路40が各フィルタの出力する信号DELAYと信号ANDの論理積である信号FILTを出力する。発生期間がクロック信号の周期とDFF回路の段数に対応する期間より短いノイズをデジタル・フィルタ20が除去し、インバータ回路の遅延時間より周期の短いノイズをディレイ・フィルタ30が除去する。

(もっと読む)

81 - 100 / 417

[ Back to top ]