Fターム[5J039KK13]の内容

Fターム[5J039KK13]に分類される特許

41 - 60 / 417

クロック生成回路

【課題】従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供する。

【解決手段】基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えた。

(もっと読む)

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

半導体集積回路

【課題】 原振クロック信号を通過させる場合の遅延時間と分周クロックを生成する場合の遅延時間を等しくするために、遅延時間の算出や遅延回路の調整を行う必要がない半導体集積回路を提供する。

【解決手段】 外部制御信号SEの論理値に基づいて、クロック信号CLKと外部入力信号SDの何れか一方を選択して内部入力信号S0とし、クロック信号CLKの立ち下がりで内部入力信号S0をラッチして第1内部出力信号S1を生成し、クロック信号CLKの立ち上がりで内部入力信号S0をラッチして第2内部出力信号S2を生成し、クロック信号CLKまたはクロック信号CLKの遅延信号を内部制御信号S3とし、内部制御信号S3の論理値に基づいて、第1内部出力信号S1または第2内部出力信号S2の何れか一方を選択出力し、選択された一方の内部出力信号は、当該選択期間中は信号レベルが変化しない。

(もっと読む)

時間デジタル変換装置

【課題】時間デジタル変換装置のダイナミックレンジを広くする。

【解決手段】第1の信号に応答して、所定の周期で繰返される第1のパルスの生成を開始する第1のパルス列生成部と、前記第1の信号に応答して、前記第1のパルスのカウントを開始するカウンタ回路と、入力端子が互いに接続され更にクロック端子が互いに接続される複数の遅延フリップフロップを有するストキャスティック型時間デジタル変換装置とを含み、第2の信号が入力する時の前記カウンタ回路のカウント数に基づく第1の時間を、前記第1の信号と前記第2の信号の時間差として検出する。

(もっと読む)

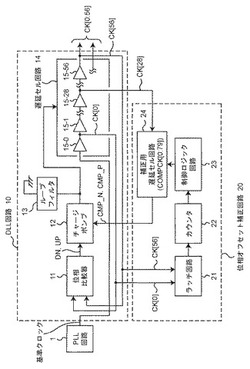

クロック生成装置及びDLL(DigitalLockedLoop)回路及びクロック生成方法

【課題】回路規模が小さく、また設計が容易な構成にて、高精度なクロックを生成するDLL回路を実現する。

【解決手段】DLL回路は、外部から入力される動作クロックclksと前記動作クロックと周波数が異なるもしくは等しい入力クロックと所望の周波数を表す設定値kから前記動作クロック周波数の前記設定値k分の一の周波数を有する生成クロックclkcを生成するクロック生成部100と、前記生成クロックclkcと外部から入力される参照クロックclkrの位相差を比較し、その位相差を出力する位相比較部200と、前記位相比較部200の出力である位相差から、前記位相差を“0”とするように前記設定値kへ補正をする補正値を生成し、前記設定値kへ補正値を加算する補正部300とを備える。

(もっと読む)

発振周波数補正信号発生回路

【課題】発振周波数とは別の周波数を生成するための回路を別途設けることなく、発振周波数を補正することができるようにする発振周波数補正信号発生回路を提供する。

【解決手段】発振信号を互いに異なる遅延時間にて遅延させて複数の遅延信号を生成し、当該遅延信号の各々に基づくタイミングにて当該発振信号を1周期単位でサンプリングして周期毎のサンプル値群を生成し、互いに異なる時点の2つの測定対象周期における当該サンプル値群の一連のサンプル値を比較してその比較結果に応じて前記補正信号を生成する。

(もっと読む)

周波数判定回路および半導体装置

【課題】長短のパルス幅が混在するデータ信号の周波数を判定することができる技術を提供する。

【解決手段】複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路201において、複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路を有する。例えば、所定のパルス幅よりも短いパルス幅の信号を検出し、その検出した信号のパルス数をカウントする。予めパルスのカウント数と周波数の対応付けをしておくことで、カウント数に基づいて周波数を判定することができる。

(もっと読む)

信号整形装置

【課題】高いクロック周波数に対応した高速動作が可能であると共に、高い精度でデューティ比を調節できる信号整形装置を提供すること。

【解決手段】所定パルス幅のパルス信号を生成するパルス信号生成部11と、パルス信号のデューティ比を制御するデューティ比調節部12と、を有する信号整形装置であり、パルス信号生成部11は、クロック信号が入力されるフリップフロップ回路101と、フリップフロップ回路101の出力信号を遅延させて当該遅延量に応じたパルス幅を有する単相のパルス信号を出力する遅延回路102と、を備え、デューティ比調節部12は、遅延回路102から出力される単相のパルス信号を互いに極性が反転した第1パルス信号と第2パルス信号からなる差動パルス信号に変換し、第1パルス信号の平均電圧と第2パルス信号の平均電圧との差に基づいて、パルス信号が目標のデューティ比になるように遅延回路102の遅延量を制御する。

(もっと読む)

制御回路及びこれを用いたデータ保持装置

【課題】セットの部品点数削減や低消費電力化を実現することが可能な制御回路及びこれを用いたデータ保持装置を提供する。

【解決手段】制御回路10は、トリガ信号TRIGGERに特定の信号パターンが現れたときに制御部11の動作に必要な内部クロック信号LCLKの生成を開始し、少なくとも制御部11において所定の処理が完了するまで内部クロック信号LCLKの生成を継続した後、内部クロック信号LCLKの生成を停止する内部クロック生成部12と、内部クロック信号LCLKを用いて前記所定の処理を実行する制御部11と、を有する。

(もっと読む)

PLL回路

【課題】平均値計算器に演算能力が比較的低い計算器を用いることが可能な技術を提供することを目的とする。

【解決手段】PLL回路は、基準クロック信号frと比較クロック信号fpとの位相比較を基準クロック信号frの周期毎に実行し、高電圧レベルの第1パルス及び低電圧レベルの第2パルスを含む信号を、前記第1及び第2パルスの当該周期単位でのパルス幅の差が当該位相比較での位相差に対応するように生成する位相比較器2と、位相比較器2が生成した信号の電圧を基準クロック信号frの周期毎に平均化する平均値計算器3とを備える。そして、平均値計算器3からの出力を基準クロック信号frの1周期分よりも長く遅延させるm周期遅延器5を備える。

(もっと読む)

半導体装置

【課題】クロック伝送回路3の電流消費量の増大を抑えつつ、リードデータのジッタを軽減する。

【解決手段】半導体装置10は、アクティブ期間内に内部クロック信号LCLKよりも周期の長い長周期クロック信号を供給し、アクティブ期間に続くリード期間内に内部クロック信号LCLKを供給するクロック出力制御回路73と、クロック出力制御回路73から出力された内部クロック信号LCLK及び長周期クロック信号を伝送するクロック伝送回路3と、データ入出力端子14と、クロック伝送回路3によって伝送された内部クロック信号LCLKに同期して、データ入出力端子14にリードデータを出力する入出力回路64とを備える。

(もっと読む)

半導体装置

【課題】立ち上がり時間と立ち下がり時間の差を解消しつつ、動作に伴う貫通電流の発生が防止されたレベルシフト回路を提供する。

【解決手段】互いに同じ回路構成を有するレベルシフト回路LV1,LV2と、レベルシフト回路LV1,LV2に相補の入力信号をそれぞれ供給する入力回路と、レベルシフト回路LV1,LV2から出力される相補の出力信号を同相に変換した後に短絡する出力回路とを備える。本発明によれば、同じ回路構成を有する2つのレベルシフト回路LV1,LV2を用いるとともに、これらレベルシフト回路LV1,LV2から出力される相補の出力信号を同相に変換した後に短絡していることから、レベルシフト回路LV1,LV2の動作速度差による貫通電流の発生がほとんど生じない。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

動作クロック生成装置、動作回路、及び、画像形成装置

【課題】少なくとも動作クロックの立ち上がりまたは立ち下がりのタイミングが所望のスペクトラム拡散クロックの周波数である動作クロックを生成する動作クロック生成装置、並びに、その動作クロック生成装置を用いた動作回路及び画像形成装置の提供。

【解決手段】基準クロックを計数したカウンタ値の増加に応じて、その基準クロックの立ち上がりタイミングを(A)に示す遅延量tr0〜tr23で遅延補正し、立ち下がりタイミングを(B)に示す遅延量tf0〜tf23で遅延補正した動作クロックを出力する。カウンタ値が1つ増加する間の遅延量trの各増減幅が、EMIを十分に抑制可能な所望の第1スペクトラム拡散クロックにおいて各クロックの立ち上がりタイミングが取る各周波数にそれぞれ相当する値となるように、遅延量tr0〜tr23を設定している。遅延量tf0〜tf23も、所望の第2スペクトラム拡散クロックに応じて設定している。

(もっと読む)

位相比較器

【課題】位相比較器において、2つのフリップ・フロップの出力信号がリセットされるまでの遅延時間によって両出力信号に現れる余分な成分を取り除き、それによって生じる種々の問題を解決すること。

【解決手段】本発明の位相比較器は、比較対象の2つの入力信号が入力されて第1と第2の出力信号を出力する第1と第2のフリップ・フロップと、第1と第2の出力信号を論理積処理してリセット信号を出力する論理積処理回路と、論理積処理回路と同じ遅延時間を持ち第1遅延信号と第2遅延信号を出力する第1と第2の遅延手段と、第1遅延信号と第2遅延信号がそれぞれ入力されるとともにリセット信号によってリセットされて第3と第4の出力信号を出力する第3と第4のフリップ・フロップとを備え、位相が進んだ方の入力信号を遅延させた第1もしくは第2遅延信号が入力される第3もしくは第4のフリップ・フロップの出力信号に位相比較出力信号が出力さるように構成されている。

(もっと読む)

電子機器

【課題】複数の接続部に動作クロックを出力すると、それぞれのクロックの立ち上がり及び立ち下がりにより生じる電磁波の周りへの影響が大きい。

【解決手段】電子機器は、信号の授受する動作クロックの周波数が同じ複数の外部機器が接続される複数の接続部と、複数の接続部に対して互いに位相をずらした動作クロックを出力するクロック出力部とを備える。クロック出力部は、複数の接続部のうちの2つに対して互いに逆位相の動作クロックを出力する。

(もっと読む)

高速量子化器

【課題】高速量子化器および最適化された時間遅延を提供する。

【解決手段】高速量子化器コンパレータの装置と方法は、3部を含む:プリアンプ部、再生ラッチ部、およびデータラッチ部。時間遅延は、再生ラッチ出力の最初の電圧を変えることによって減少される。電流源はコンパレータの底部に提供され、時間遅延最適化を可能にする。PMOS同等化スイッチが停止されたとき、クロック信号をフィードスルーにし、出力に電荷の注入を提供する。これらの電荷によって、コンパレータの時間遅延が可変となる。リセット時間が比較時間より長いために、非常に低い電流が出力電圧を決定する。

(もっと読む)

デジタル位相比較器およびこれを備えたデジタルPLL回路

【課題】デジタル位相比較器におけるスタートアップ時のキャリブレーションを不要とする。

【解決手段】基準信号を遅延させて遅延基準信号として出力し、遅延量に相当する時間差を有する遅延量信号を出力する手段と、遅延基準信号と発振器出力信号との時間差をデジタル値に変換し第1のデジタル値として出力する手段と、第1の時間量子化器で発生した時間残差を検出し、時間残差に応じた時間差を有する時間残差信号を出力する手段と、基準信号の状態に応じて時間残差信号を出力するか遅延量信号を出力するかを切り替える手段と、時間残差信号の時間差をデジタル値に変換して第2のデジタル値として出力し、遅延量信号の時間差をデジタル値に変換して第3のデジタル値として出力する手段と、第2のデジタル値および前記第3のデジタル値を用いて第1のデジタル値を補正することで小数位相を算出する手段と、を有する。

(もっと読む)

周波数シンセサイザおよび時間デジタル変換器

【課題】周波数シンセサイザにおいて、ループ帯域内位相ノイズの低減を小面積かつ低電流の構成で実現する。

【解決手段】周波数シンセサイザは、発振器1と、発振器1出力の分周信号CKVと参照信号Frefとの正規化された位相差を検出するTDC回路7とを備え、TDC回路7によって検出された正規化された位相差に基づいて発振器1の周波数を制御する。TDC回路7は、第2の発振器711と、第2の発振器711の出力信号OSC2の周期数をカウントするカウンタ712とを備え、カウンタ712の出力から、分周信号CKVの周期に相当するカウンタ値と、分周信号CKVと参照信号Frefとの位相差に相当するカウンタ値とを得て、これらのカウンタ値に基づいて、正規化された位相差を算出する。

(もっと読む)

注入同期発振器

【課題】逓倍数が任意の大きな数であっても、位相雑音が低減された注入同期発振器を得る。

【解決手段】注入同期発振器は、注入される注入信号に同期して自励発振周波数の信号を発振する発振器を備える注入同期発振器において、上記自励発振周波数と略同じ周波数の逓倍数分の1の周波数の基準信号が入力されるともに該基準信号にトリガーされてパルスを生成するパルス発生回路と、上記パルス発生回路で生成したパルスとタイミングが異なる少なくとも1つのパルスを生成するとともに該生成されたパルスと上記パルス発生回路で生成したパルスとを合わせて注入信号として出力するパルス数増倍回路と、を備える。

(もっと読む)

41 - 60 / 417

[ Back to top ]