Fターム[5J039KK13]の内容

Fターム[5J039KK13]に分類される特許

241 - 260 / 417

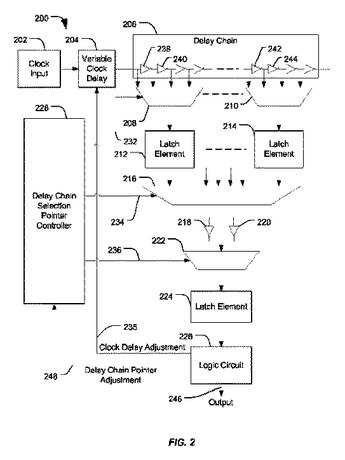

クロック・ジッタを測定する回路装置および方法

一実施形態では、回路装置の遅延チェーンにおいてクロック信号を受信すること、及び、該遅延チェーン内の選択される点において該クロック信号の値を決定すること、を含む方法が開示される。該方法は又、該値が該クロック信号のエッジの検出を示さない場合には、該選択される点を調整することを含む。  (もっと読む)

(もっと読む)

フィルタ回路および方法

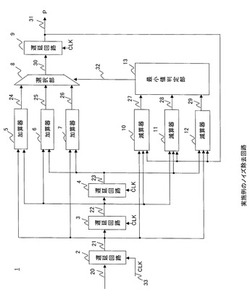

【課題】サンプリングクロックに同期して順次入力されるデジタルデータに連続したサンプリング周期にわたって混入したノイズをも除去するノイズ除去回路および方法を提供。

【解決手段】ノイズ除去回路1は、3つの遅延された入力データ(21、22、23)のうちのそれぞれ2つの平均(24、25、26)を算出し、これらの平均値のいずれが前回選択された出力データ(31)の値に対して最小の差(27、28、29)を有するかを判定し、最小の差を有する減算器データ(32)に対応する加算器(5、6、7)が出力する平均値(24、25、26)をフィルタ済出力信号値31として出力することにより、入力信号20に連続したサンプリング周期にわたり混入したノイズを除去する。

(もっと読む)

複数の発振回路を備える電子回路

【課題】メイン回路とサブ回路に独立して別々にクロック発振回路を設ける回路構成としながら、サブ回路に設けているサブクロック発振回路の周波数のずれを極めて簡単な回路構成で検出する。

【解決手段】複数の発振回路を備える電子回路は、主クロック発振回路10を備えるメイン回路1と、このメイン回路1に信号伝送回路3を介して接続してなるサブクロック発振回路20を備えるサブ回路2とを備える。メイン回路1は、サブクロック発振回路20の発振周波数のずれを検出する周波数検出回路11を備える。サブ回路2は、サブクロック発振回路20の出力パルスをカウントするカウンター24を備える。メイン回路1の周波数検出回路11は、サブ回路2のカウンター24のカウント値を検出してサブクロック発振回路20の周波数のずれを検出する。

(もっと読む)

位相検出回路及びデータ処理装置

【課題】回路構成が簡素化され、低消費電力化され集積回路化する上で有利な構成の回路を得る。

【解決手段】第1クロックが各クロック入力端に与えられる複数段のフリップフロップ回路(Q1−Q7)と、第2クロックが入力される直列接続された複数段の遅延素子(D1−D6)と、前記複数段の遅延素子の出力をそれぞれ、前記複数段のフリップフロップ回路の各データ入力端に与える接続部(L1−L7)と、前記複数段のフリップフロップ回路の出力データが入力され、この出力データ内容に応じて変化する制御信号を得る信号生成回路(163)と、前記信号生成回路からの制御信号に応じて、前記第1若しくは第2クロックを相調整する位相調整信号を出力する位相調整信号出力部(164)を有する。

(もっと読む)

電子回路装置

【課題】パルス幅を意図的に変化させるNRZ等の信号の伝送において、パルス幅のバラツキの低減を図り、さらにジッタの低減も図る。

【解決手段】2個のエッジ検出回路11,12と、2個の可変遅延回路13,14と、SRラッチ回路15とを備え、可変遅延回路13,14のそれぞれの入力にエッジ検出回路11,12の出力を接続し、SRラッチ回路のS入力およびR入力それぞれに可変遅延回路13,14の出力を接続する。前記SRラッチ回路15が、可変遅延回路13,14の出力のパルス終端側エッジを検出してセット/リセット動作を行う。

(もっと読む)

クロック信号出力回路

【課題】逓倍クロック信号の基準クロック信号に対する同期ずれを補正することができるクロック信号出力回路を提供する。

【解決手段】位相誤差補正回路12は、基準クロック信号PREFと逓倍クロック信号POUTとの位相差を検出し、その位相差に応じて、逓倍クロック信号POURの出力位相を基準クロック信号PREFに同期させる補正を、1制御周期の間に複数回実行する。

(もっと読む)

パルス幅測定方法および回路

【課題】入力パルスのデューティが測定可能となり、回路構成が簡素化できるようにする。

【解決手段】HレベルとLレベルとを繰り返す入力パルスを同一遅延時間でn+1段に亘って遅延させてn+1相の遅延パルスを生成し、該n+1相の各遅延パルスのそれぞれがHレベルであるかLレベルであるかに応じて変化し、且つ所定のタイミングにおいて、前記入力パルスのHレベル側又はLレベル側のパルス幅を示すエンコード信号を生成し、前記所定のタイミングにおける前記エンコード信号を、前記Hレベル側又はLレベル側のパルス幅信号として保持する。

(もっと読む)

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックに応答して1ビットずつレベル遷移する複数のビットの周波数制御信号を生成する周波数制御信号生成部と、及び前記複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。また、他の発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

適応型ホールドを用いる、デジタル・シングル・イベント過渡に対して強化されたレジスタ

【課題】デジタル・シングル・イベント過渡に対してレジスタを強化する。

【解決手段】レジスタの捕捉クロック・エッジのタイミングを調整して、データが正しい状態に戻ったときにレジスタがデータを捕捉するようにすることにより、レジスタをDSETの混乱状態から保護することができる。データ・グリッチがクロック・エッジ付近で発生した場合、レジスタ出力における有効時間が増加される(CLKからQ)。この有効時間の増加は、DSET過渡の存在がクロック・エッジ付近で検出されたときに、行われる。

(もっと読む)

周期信号訂正回路

【課題】突発的に発生する周期信号の信号幅の変化を自己の周期信号だけで補償する。

【解決手段】信号遅延部110は、周期信号Cを繰り返し周期の半分の時間だけ遅延させることによって遅延周期信号Cdを生成する。異常検出部120は、周期信号Cと遅延周期信号Cdが両方ともハイレベルであるとき異常信号ErrAを生成し、周期信号Cと遅延周期信号Cdが両方ともローレベルであるとき異常信号ErrBを生成する。制御部130は、異常信号ErrAを奇数回目に検出したとき制御信号ContAを生成し、異常信号ErrBを奇数回目に検出したとき制御信号ContBを生成する。訂正部140は、制御信号ContAが生成されると、周期信号Cをハイレベルからローレベルに変更し、制御信号ContBが生成されると周期信号Cをローレベルからハイレベルに変更する。

(もっと読む)

入力インタフェース回路、集積回路装置および電子機器

【課題】信号入力端子に静電気ノイズが印加された場合に、そのノイズの内部回路への伝達を未然に、かつ確実に防止することができる入力インタフェース回路を提供すること。

【解決手段】ノイズを検出するノイズ検出回路(200)と、ノイズが検出されたときに第1のスイッチ回路(SW1)をオフしてノイズ伝達を遮断する機能をもつノイズキャンセラ(300)と、を設ける。第1のスイッチ回路(SW1)がオフしているときは、第2のスイッチ回路(SW2)がオンして、直前の電圧をラッチする。ノイズ検出回路200に含まれるノイズ検出用トランジスタは、Nウエルの電位を適応的に最適化することができるフローティングNウエルトランジスタによって構成される。

(もっと読む)

ホールドフリーレジスタセル

【課題】汎用的に使用することのできるホールドフリーレジスタセルを提供する。

【解決手段】ホールドフリーレジスタセル1は、クロック信号CKを切り替え信号として2つの入力信号の切り換えを行うマルチプレクサ11と、マルチプレクサ11の出力遅延時間に応じてクロック信号CKを遅延させ、クロック信号CKdとして出力する遅延回路12と、遅延回路12から出力されたクロック信号CKdの立ち下りでマルチプレクサ11から出力されるデータをラッチするラッチ回路13と、を備える。マルチプレクサ11は、クロック信号CKがデータ取り込みエッジ前のレベルである‘1’のときはデータ入力信号Dを出力し、クロック信号CKがデータ取り込みエッジ後のレベルである‘0’のときはラッチ回路の出力信号Q1を出力する。

(もっと読む)

クロック周波数拡散装置

【課題】クロック高調波を低減して従来よりもEMIを低減する。

【解決手段】クロック周波数拡散装置は、入力クロック信号Clk_inを遅延させて位相の異なる複数のクロックClkd[15:0]を生成して出力する複数位相クロック生成器40と、複数のクロックClkd[15:0]に基づき任意の乱数Cnt1[3:0]を発生して出力する乱数発生器50と、乱数Cnt1[3:0]に基づき、複数のクロックClkd[15:0]を選択してクロックClkn,Clkpを出力するクロックセレクタ60と、クロックClkn,Clkpに応答した論理値を有する拡散された周波数の出力クロックClkoを生成して出力するクロック生成器70とを有している。

(もっと読む)

クロック異常検知回路

【課題】クロック信号の異常を精度良く検出することができるクロック異常検知回路を提供する。

【解決手段】クロック信号CKを検出してパルスを生成するパルス生成回路11と、電流源18から出力される電流を充電する充電回路13と、パルス生成回路11からのパルスによって、充電回路13に充電された電圧を放電する放電回路12と、充電回路13に充電された電圧を検知し、その電圧に応じた信号を出力する第1の電圧レベル検知回路15と、第1の電圧レベル検知回路15の出力に応じて制御された制御電圧を出力するピークホールド回路17と、充電回路13に充電された電圧を降圧し、降圧電圧を生成する電圧シフト回路14と、電圧シフト回路14により降圧された降圧電圧を検知する第2の電圧レベル検知回路16とを備える。ピークホールド回路17から出力された制御電圧に応じて電流源18は充電回路13に電流を出力する。

(もっと読む)

並列接続トランジスタ

【課題】配線のための面積増加なしに各トランジスタの入力信号の強度及び位相を均一にできる並列接続トランジスタを提供する。

【解決手段】並列接続トランジスタ50は、信号入力端子60に接続される伝送線路70、72と、伝送線路70及び72に沿って一列に配列されたトランジスタ84−1〜84−8及び88−1〜88−8と、伝送線路70、72に沿って一列に配列され、伝送線路70、72に一端が接続され、トランジスタ84−1〜84−8及び88−1〜88−8の対応する1つのベース端子に他端が接続された複数の容量素子82−1〜82−8及び86−1〜86−8とを含み、容量素子82−1〜82−8及び86−1〜86−8の容量値は、信号入力端子60からの伝送線路の線路長が大きいほど、小さくなっている。

(もっと読む)

半導体集積回路およびイコライザの制御方法

【課題】回路規模の増大を抑制しつつ、受信したデータ信号の等化量を調整することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路100は、イコライザと、イコライザにより等化されたデータ信号の位相を検出しこのデータ信号の位相と復元クロック信号の位相とを比較し、等化されたデータ信号のビット幅が復元クロック信号の周期よりも小さいときは第1の比較信号を出力し、一方、大きいときは第2の比較信号を出力し、復元クロック信号の位相がデータ信号の位相よりも進んでいる場合には第3の比較信号を出力し、遅れている場合には第4の比較信号を出力する位相比較回路と、第3、第4の比較信号および基準クロック信号に基づいて、復元クロック信号を生成する復元クロック生成回路と、少なくとも第1、第2の比較信号に基づいて、イコライザのピーキング量を制御する制御回路と、を備える。

(もっと読む)

高データレートのオフチップ・データ通信を実行するためのシステム及び方法

ある電子機器が説明される。その電子機器は、第1の集積回路(IC)と第2の集積回路(IC)とを含む。また、その電子機器は、パラレルデータ信号をシリアルデータ信号に多重化するように構成されたマルチプレクサと、該シリアルデータ信号を該第1のICから該第2のICへ送信するように構成された送信機とを含む。さらに、その電子機器は、該シリアルデータ信号を受信するように構成された受信機を含む。該受信機は、アナログノードの電圧振幅を決められた範囲内にクランプするように構成されたクランプ回路を含む。該クランプはまた、該受信機のバンド幅を拡張するのに役立つ。  (もっと読む)

(もっと読む)

周波数/位相比較器

【課題】フルレートとハーフレートの両方に対応して、周波数比較モードおよび位相比較モードで正常動作を行うことのできる周波数/位相比較器を得る

【解決手段】フルレートおよびハーフレートのどちらに対してもクロック信号の振幅値をアナログホールド出力するアナログホールド位相比較部10と、フルレートの場合に1/4周期遅れのクロック信号の振幅をデジタルホールド出力し、ハーフレートの場合に1/8周期遅れのクロック信号の振幅をデジタルホールド出力するデジタルホールド位相比較部20、30と、アナログホールド値とデジタルホールド値に基づいて、入力データ信号とクロック信号の周波数比較を行う周波数比較手段50と、デジタルホールド値の極性に応じて、アナログホールド位相比較部10からの出力値と周波数比較手段50からの出力値を選択出力する最終出力信号選択手段60とを備える。

(もっと読む)

信号処理システム、記録情報再生システムおよび信号受信システム

【課題】製造コスト上昇を抑える。

【解決手段】信号処理システムであって、制御端子に与えられた制御信号に応じた遅延を、入力端子に入力された信号に与えて出力端子から出力する第1の遅延回路と、前記第1の遅延回路と同様に構成され、入力端子と出力端子とが接続された第2の遅延回路を有し、発振信号を出力する発振器と、前記発振器の発振信号に応じた信号と基準となる信号との間の位相を比較し、比較結果を示す信号を出力する位相比較回路と、前記位相比較回路の出力信号の低周波成分を、前記第1及び第2の遅延回路の制御信号として用いられるように出力するフィルタ回路とを有する。前記第1の遅延回路の入力端子に与えられ、その出力端子から出力された遅延した信号が、前記基準となる信号として前記位相比較回路に与えられている。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 PVT変動に起因して周波数変調プロファイルが変化することを防止することができるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 入力クロックCLKINと出力クロックCLKOUTの位相を位相比較記30で比較し、その比較結果信号POに基づいて制御回路20で新たな遅延パターンを算出し、その新たな遅延パターンに従って1クロックパルス毎に遅延セル11_0,11_1,11_2,11_3,…,11_N−2,11_N−1,11_Nの段数を切替信号S[0],S[1],S[2],S[3],…,S[N−2],S[N−1],S[N]により切り替えながら入力クロックCLKINを入力させて周波数変調を行なう。

(もっと読む)

241 - 260 / 417

[ Back to top ]