Fターム[5J039KK13]の内容

Fターム[5J039KK13]に分類される特許

181 - 200 / 417

カウンタ回路、レイテンシカウンタ及びこれを備える半導体記憶装置、並びに、データ処理システム

【課題】ハザードなどが発生しやすい高周波信号を正しくカウントすることが可能なカウンタ回路を提供する。

【解決手段】クロック信号LCLKに基づいて、互いに位相の異なる分周クロックLCLKE,LCLKOを生成する分周回路100と、分周クロックLCLKEをカウントする第1のカウンタ210と、分周クロックLCLKOに同期して第1のカウンタ210のカウント値を取り込む第2のカウンタ220と、第1及び第2のカウンタ210,220のカウント値を排他的に選択する選択回路230とを備える。本発明によれば、第1及び第2のカウンタ210,220のカウント値の関係が常に一定に保たれることから、ハザードが生じた場合であってもカウント値がジャンプするのみであり、カウント値が不定となることがない。

(もっと読む)

信号逓倍器、信号生成器、光送信器および光通信装置

【課題】回路の製造ばらつきや経時変動があっても、クロック信号のデューティ比を精度よく制御すること。

【解決手段】入力部11には、連続して電圧が変化するクロック信号が入力される。供給部12は、一定の参照電圧を供給する。セレクタ13は、入力部11から入力されたクロック信号の電圧が、供給部12によって供給される参照電圧を跨ぐごとに電圧を交互に切り替えたクロック信号を出力する。演算回路14は、入力部11から入力されたクロック信号と、セレクタ13から出力されたクロック信号と、の排他的論理和を出力する。

(もっと読む)

半導体素子の内部電圧生成回路及び内部電圧生成方法

【課題】外部クロックの周波数の変動にかかわらず、常に安定した電圧レベルを維持できるようにする半導体素子の内部電圧生成回路を提供すること。

【解決手段】本発明は、内部電圧端の電圧レベルが所定の目標レベルより低くなる期間において、前記内部電圧端をプルアップ駆動する第1電圧駆動手段20と、外部クロックの周波数に対応する周期の1周期毎に、所定時間の間、前記内部電圧端をプルアップ駆動する第2電圧駆動手段22とを備える半導体素子の内部電圧生成回路を提供する。

(もっと読む)

半導体集積回路装置

【課題】遅延を有する論理回路から検出した信号を直接利用して、その論理回路の電源電圧の制御を行うような機構が求められている。

【解決手段】本発明は、本発明は、論理回路と、前記論理回路の遅延の変化に応じた周波数の検出信号を出力する遅延特性検出回路と、前記検出信号に応じて抵抗値が変化する抵抗素子と、前記抵抗素子の抵抗値の変化に応じて参照電圧を出力する参照電圧生成回路と、前記参照電圧を前記論理回路及び遅延特性検出回路に出力する電圧供給回路とを有する半導体集積回路装置である。

(もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号が入力される端子とVCXO109の入力端子との接続を制御し、異常信号によって接続をオンにするスイッチとを有するタイミングリカバリー回路である。

(もっと読む)

半導体集積回路

【課題】出力バッファを必要とせずに多相クロックの位相状態の検出を可能にする半導体集積装置を提供する。

【解決手段】半導体集積回路1Aは、集積化された論理演算回路12、クロック生成器10、中継回路11および信号生成部13を有する。クロック生成器10は、多相クロックMP0を生成する。中継回路11は、当該生成された多相クロックMP0を論理演算回路12に分配する。信号生成部13は、当該分配された多相クロックMP1の位相状態を検出し、当該検出された位相状態に基づいて多相クロックMP1の位相誤差を表す電圧値を持つアナログ電圧信号LV0,LV1を生成する。

(もっと読む)

パルス幅補正装置およびパルス幅補正方法

【課題】二値化のコンパレートレベルを調整することなく、データが誤って取り込まれるのを防止すること。

【解決手段】デューティー比検出回路3は、二値化信号DIのデューティー比の基準値からのずれを検出し、遅延回路5は、二値化信号DIを所定の遅延量だけ順次遅延させた遅延信号DLを生成し、セレクタ6は、デューティー比検出回路3にて検出された二値化信号DIのデューティー比のずれに対応した遅延信号DLnを遅延信号DLから選択し、パルス幅補正回路7は、セレクタ6にて選択された遅延信号DLnを用いることにより、二値化信号DIのパルス幅を補正する。

(もっと読む)

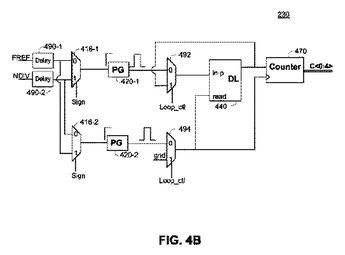

完全デジタル位相ロックループにおける位相デジタル変換器

位相デジタル変換器と、完全デジタル位相ロックループと、完全デジタル位相ロックループを有する装置とについて、本明細書で説明する。位相デジタル変換器は、時間デジタル変換器を駆動する位相周波数変換器を含む。時間デジタル変換器は、位相周波数変換器によって出力された位相差の絶対値と符号とを判断する。時間デジタル変換器は、タップ付き遅延線とループフィードバックカウンタとを利用して、ループ追跡プロセスによくある小さいタイミング差およびループ収集プロセスによくある大きいタイミング差の測定を可能にする。タップ付き遅延線は、基準期間の部分の測定を可能にし、基準クロックの速度に関する要件を低減することによって位相デジタル変換器のより低電力の動作を可能にする。  (もっと読む)

(もっと読む)

パルス発生回路及び通信装置

【課題】簡単な回路でかつ低消費電力で帯域制限された正確な短パルスの発生回路を具現し、フィルタを使用せずに目的のパルスを得る。

【解決手段】起動信号に基づき所定形状のパルスを出力端子から出力するパルス発生回路において、起動信号の位相が変化した時点から所定量の時間差で位相が順次変化するn+1個の信号(nは2以上の整数)を発生するタイミング発生回路と、所定の電位を供給する第1の電源及び第2の電源と、n個のインピーダンス素子と、n+1個の信号に基づく論理関数値によって所定順序で出力端子と第1の電源または第2の電源とをインピーダンス素子を介して交互に切り替えて接続するスイッチ回路と、を含むパルス発生回路。

(もっと読む)

半導体回路および試験装置

【課題】電源電圧のリップルが信号処理回路に及ぼす影響を低減する。

【解決手段】第1信号処理回路10は、第1信号S1に所定の信号処理を施し、その特性値に変化を与えて第2信号S2を出力する。第2信号処理回路12は、第2信号S2に所定の信号処理を施し、その特性値に変化を与えて第3信号S3を出力する。第1、第2スイッチング電源20、22はそれぞれ、第1、第2信号処理回路10、12に対し電源電圧Vdd1、Vdd2を供給する。第1信号処理回路10が第1信号S1の特性値に与える変化量と、第2信号処理回路12が第2信号S2の特性値に与える変化量はそれぞれ、電源電圧Vdd1、Vdd2に対する依存性を有する。第1、第2スイッチング電源20、22の位相はそれぞれ、第1信号S1の特性値の変化量とその目標値との誤差と、第2信号S2の特性値の変化量とその目標値との誤差がキャンセルするように設定される。

(もっと読む)

半導体集積回路

【課題】ダイナミックコンパレータのモード切替時に影響されることなく、後段回路用に正確に入力信号電位をサンプリングできる回路を提供する。

【解決手段】入力信号源(60)と後段回路(90)との間にサンプリング回路(20)が接続され、入力信号源(60)とダイナミックコンパレータ(70)の入力端子(8)との間に入力信号用スイッチ(30)が接続され、さらに、コンパレータ用キャパシタ(40)の一端は入力信号用スイッチ(30)と入力端子(8)と間に接続され、他端は固定電位に接続されたコンパレータ回路で構成される。タイミング制御回路(50)は、ダイナミックコンパレータが待機モードから比較モードへの切替の前に、入力信号用スイッチ(30)を遮断状態にする制御信号を出力し、切替の後に、サンプリング回路(20)のサンプリングを終了させる制御信号を出力する。

(もっと読む)

データ出力回路

【課題】データ出力回路を提供する。

【解決手段】クロック信号を受信して所定のパルス幅を持つクロックパルスを生成するデータ出力制御部と、前記クロックパルスに同期して第1データを出力する第1データ出力部と、前記クロックパルスに同期して第2データを出力する第2データ出力部と、を含むデータ出力回路を提供する。

(もっと読む)

高速時間ディジタル・コンバータ

【解決手段】 時間ディジタル・コンバータ(TDC)がサブ・インバータ遅延分解能でサンプリングすることを可能にするための手法が開示されている。一実施形態では、TDC中の差動型D−Qフリップフロップへの入力は、シングルエンド型信号、およびこの信号の遅延された形態および反転された形態に接続されてこの信号の時間補間を可能にする。さらに、TDC中の第1遅延ラインおよび相補な遅延ラインの負荷の平衡を保つための手法が開示されている。 (もっと読む)

位相検出装置、位相比較装置およびクロック同期装置

【課題】クロック同期システムに用いる位相比較器として、次段のカウンタに影響を与えることなく、クロックの同期がとれた際に確実にロックをかけること。

【解決手段】本発明は、基準クロックの位相に対する比較クロックの位相のずれを検出する第1の位相比較部K1aと、基準クロックおよび比較クロックのいずれか一方について所定時間遅延または進んだ状態での両クロックの位相のずれを検出する第2の位相比較部K1bと、第1の位相比較部K1aの出力と第2の位相比較部K1bの出力との論理積を位相ずれの検出結果として出力する論理積部AND1とを備える

(もっと読む)

フリップフロップ回路

【課題】不感帯が少なく高速安定動作が可能なフリップフロップ回路を提供すること。

【解決手段】本発明は、データ信号Dと、立ち上がり遅延クロック信号CKdとを入力し、データ信号Dの立ち下がりと立ち上がり遅延クロック信号CKdの立ち下がりとによって内部ノードNCの信号を立ち上げる第1のラッチ回路L1と、内部ノードNCの信号とクロック信号CKとを入力し、内部ノードNCの信号が立ち上がっている状態でクロック信号CKが立ち下がるタイミングにより内部ノードXの信号を立ち下げる第2のラッチ回路L2と、内部ノードXの信号とクロック信号CKとを入力し、クロック信号CKが立ち上がっている状態でのデータ信号Dを保持する出力信号を生成するための第3のラッチ回路L3と、内部ノードNCの信号を立ち上がり遅延クロック信号CKdによってプルダウンさせるプルダウン回路PDとを備えるフリップフロップ回路である。

(もっと読む)

半導体集積回路装置および逓倍クロック生成方法

【課題】 エージング時に使用可能な同期逓倍クロック発生回路を提供することである。

【解決手段】 可変ディレイヤを用いた発振回路と、カウンタを用いた発振周波数制御回路とを有し、入力クロック周波数の逓倍の周波数のクロックを発生するクロック発生回路において、上記発振回路を入力クロックに同期させて動作させることで、入力クロックと同期した逓倍クロックを発生させる。

(もっと読む)

半導体集積回路

【課題】低消費電力化に適したAVS技術又はDVS技術を実現した半導体集積回路を提供すること。

【解決手段】半導体集積回路は、クリティカル・パスを形成する第1のフリップ・フロップ、組み合わせ回路及び第2のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第1の遅延回路及び第3のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第2の遅延回路及び第4のフリップ・フロップと、第2のフリップ・フロップの出力と第3のフリップ・フロップの出力とを比較する第1の比較回路と、第2のフリップ・フロップの出力と第4のフリップ・フロップの出力とを比較する第2の比較回路と、これら比較回路の出力に応じて、前記組み合わせ回路に供給される電源電圧を制御する制御回路とを備える。なお、第1の遅延回路による遅延時間と第2の遅延回路による遅延時間は異なる。

(もっと読む)

位相同期装置

【課題】本発明は、短いロッキングタイムを有しながらも、安定的に動作できる位相同期装置を提供する。

【解決手段】本発明の位相同期装置は、入力クロックを所定の分周比で分周した後、順次遅延させる動作により周波数を判別し、前記判別された周波数情報を用いて発振器ゲイン設定信号を生成する発振器ゲイン設定手段と、前記入力クロックに応じて、前記発振器ゲイン設定信号に対応する周波数を有する出力クロックを発振させるPLL回路を含むことを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置において、ユーザボードの違いや製造ばらつきがあっても、電源共振ノイズによる問題を回避することができる技術を提供する。

【解決手段】半導体装置内の電源ノイズを観測する電源ノイズ観測回路1と、電源ノイズ観測回路1の出力に基づいて、生成クロック301の周波数が変化するクロック生成回路2と、生成クロック301が入力される演算回路ブロック3と、を備える。そして、前記電源ノイズ観測回路1によって観測される電源ノイズが低減するように、生成クロック301の周波数が調整される。

(もっと読む)

クロック分配回路の設計方法

【課題】消費電力を抑制しつつ、スキューの抑制およびスラックの増大を可能にするクロック分配回路の設計方法を提供する。

【解決手段】クロック分配回路の設計方法は、バッファの位置および配線の位置を設定し、クロック分配回路の共通ノードから第1の回路素子までのクロック伝達時間およびクロック分配回路の共通ノードから第2の回路素子までのクロック伝達時間を計算し、共通ノードから第1の回路素子までの第1の経路と共通ノードから第2の回路素子までの第2の経路との間のいずれかの箇所を短絡する短絡配線を設定することによって、共通ノードから第1の回路素子までのクロック伝達時間のばらつきおよび共通ノードから第2の回路素子までのクロック伝達時間のばらつきだけ、第2の回路素子が受け取るデータと第2の回路素子が受け取るクロックとの間のスラックを改善することを具備する。

(もっと読む)

181 - 200 / 417

[ Back to top ]