Fターム[5J039KK13]の内容

Fターム[5J039KK13]に分類される特許

161 - 180 / 417

半導体装置及びその制御方法

【課題】半導体装置の製造ばらつきや経年劣化に起因するクロックスキューを補正することができる半導体装置を提供する。

【解決手段】スキュー検出部6は、スキューを検出するための少なくとも1個のクリティカルパス7又はレーシングパス7を含む。クロック調整部5は、スキュー検出部6により検出されたスキューに基づいて、ディレイの設定値を設定する。クロックセル4は、ディレイの設定値に応じて、第1のクロックのディレイを調整して、第2のクロックとして出力する。

(もっと読む)

同期検出回路、これを用いたパルス幅変調回路、及び同期検出方法

【課題】部品点数の削減、高い検出精度の確保、処理速度低下の防止等を図る。

【解決手段】位相ロックループ回路15により、基準クロック信号に基づいて互いに位相が異なる複数相の多相クロック信号を生成する多相クロック生成回路11と、前記多相クロック信号の中から、同期信号に同期するクロック信号を特定する同期クロック特定回路12とを有する同期検出回路2であって、前記多相クロック生成回路11は、前記基準クロック信号を逓倍した周波数を有する高速多相クロック信号と、前記高速多相クロック信号を分周した周波数を有する低速多相クロック信号とを生成し、前記同期クロック特定回路は、同期信号と前記高速多相クロック信号との比較結果と、前記同期信号と前記低速多相クロック信号から選択された代表クロック信号との比較結果とに基づいて、前記同期信号の同期位置を示す同期位置信号を生成する。

(もっと読む)

信号再生回路向け位相比較回路及び信号再生回路向け位相比較回路を備える光通信装置

【課題】 1/Nレート構成に対応可能な高精度な位相比較回路を得る。

【解決手段】それぞれ、N相クロック信号CLKの各クロック信号を、受信データ信号DINの立ち上がりに同期してトラックホールドするN個のトラックホールド回路を備える。これらのN個のトラックホールド回路の出力から、受信データ信号DINの立ち上がりエッジが、クロック信号CLKの立ち上がりエッジに位置しているクロック信号をトラックホールドしているもののみをセレクタで選択して、位相差信号として出力する。

(もっと読む)

位相比較回路

【課題】D−FFの内部遅延が無視できない高速動作時において位相比較回路の低消費電力化を実現する。

【解決手段】マスタースレーブマスター型D−FF11は、第1のM−FF11−1,S−FF11−2および第2のM−FF11−3が縦続接続され、入力NRZデータ信号をクロック信号に応答して識別し、S−FFおよび第2のM−FFから出力する。遅延回路4は、入力NRZデータ信号をS−FFと同じ時間だけ遅延させる。第1のEXOR回路7は遅延回路の出力とS−FFの出力の排他的論理和演算を行ない、第2のEXOR8はS−FFの出力と第2のM−FFの出力の排他的論理和演算を行なう。加算器9は第1のEXOR回路の出力と第2のEXORの反転出力を加算する。

(もっと読む)

スケルチ検出回路

【課題】温度、プロセス、電源電圧の変動に強く、安定したスケルチ検出信号を出力することができるスケルチ検出回路を提供する。

【解決手段】受信した差動信号RX+,RX−の電位振幅が所定値を超えているときその検出信号Vpをパルスとして出力するピーク検出回路11と、ピーク検出回路11から出力する検出信号Vpのパルス幅を差動信号RX+,RX−の少なくとも1周期分延長するパルス幅延長回路12とを備える。ピーク検出回路11は、差動信号RX+,RX−に同一のDCバイアスを与えた後にその差分に対応する電圧信号Vdataを出力する入力差動増幅回路11Aと、入力差動増幅回路11Aのほぼレプリカ回路として構成され、参照電圧Vref’をレベルシフトしたシフト参照電圧Vrefを出力するレプリカ参照電圧生成回路11Bと、電圧信号Vdataとシフト参照電圧Vrefとを比較して検出信号Vpを出力する電圧比較回路11Cと、を備える。

(もっと読む)

ヒステリシスコンパレータ回路及びそれを用いた遅延回路

【課題】回路規模を大型化することなく、大きな遅延時間を得る。

【解決手段】遅延対象の矩形波の入力信号Vinを台形波発生回路10により台形波信号Vcに変換し、その台形波信号の中間電圧よりも高く設定された第1のスレッショルド電圧Th1を有するインバータ21と、中間電圧よりも低く設定された第2のスレッショルド電圧Th2を有するインバータ22とで、台形波信号Vcと第1及び第2のスレッショルド電圧を比較し、インバータ21とインバータ22の出力でバッファ回路23を駆動し、台形波信号Vcに同期して反転し、かつ遅延した矩形波の出力信号Voutを生成する。

(もっと読む)

デジタル位相検出器及びデジタル位相同期回路

【課題】デジタル位相検出器の時間分解能をデジタル制御し、回路規模・消費電力を低減する。

【解決手段】信号S1が入力される直列に接続された第1の遅延素子1011〜101Nと、信号S2が入力される直列に接続された第2の遅延素子1021〜102Nと、各々の第1の遅延素子の出力が与えられ、各々の第2の遅延素子の出力をクロックとするラッチ回路1031〜103Nと、前記ラッチ回路の出力値に基づいて信号S1のパルス幅を示すデジタルコードPWmを算出して出力するデコーダ回路104と、デジタルコードPWmと所定のデジタルコードPWrとを比較し、比較結果を出力する比較器105と、前記比較結果に基づいて前記第1及び第2の遅延素子の少なくともいずれか一方の遅延時間を制御する遅延制御回路106と、を備える。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】遅延固定ループで反映される遅延の程度を測定して読み出し命令に反映することにより、CASレイテンシに対応する最終出力イネーブル信号を生成することができる半導体メモリ装置を提供すること。

【解決手段】本発明の半導体メモリ装置は、遅延固定ループ310と、外部クロック信号に同期化したロック完了情報に応答して基準クロック信号とフィードバッククロック信号との間の遅延の程度を測定し、これを遅延測定値として出力する遅延及び遅延時間測定手段330と、外部クロック信号に同期化した読み出し命令情報を、基準クロック信号とDLLクロック信号との間の遅延の程度に対応する分だけ遅延させ、遅延測定値及びCASレイテンシ情報に対応してDLLクロック信号に同期化させ、最終出力イネーブル信号として生成する出力イネーブル信号生成手段350と、を備える。

(もっと読む)

多相クロック生成回路、オーバーサンプリング回路及び位相シフト回路

【課題】より位相差の微小な多相クロックを生成しつつ、消費電流の増大を抑制した多相クロック生成回路及びオーバーサンプリング回路を提供する。

【解決手段】1対の入出力端子と、遅延量制御端子にバイアスした電圧に応じた遅延量を発生させる2つの遅延ラインの出力の位相差を検出する位相比較器13と、位相比較器13の出力を平均化する平均化フィルタ14とを備え、一方の遅延量制御端子に基準電圧を接続し、他方の遅延量制御端子に平均化フィルタ14の出力を接続し各遅延ラインの出力が所定の位相差を持つように制御する遅延量制御部11と、複数かつ同数個の遅延素子を直列に接続した複数の遅延ライン21を備え、各遅延ライン21は基準電圧を接続した遅延素子22の数及び平均化フィルタ14の出力電圧を接続した遅延素子の数の組み合わせを異ならせたクロック遅延部20とを備え、所定の位相差を持つ多相クロックを生成する。

(もっと読む)

セットアップ/ホールドタイム測定装置

【課題】テスト信号に応じて外部クロック信号からデータ信号と内部クロック信号を生成し、読取り/書込み動作無しでバッファリングされたデータの状態によってセットアップ/ホールドタイムを測定できるようにしたセットアップ/ホールドタイム測定装置を提供する。

【解決手段】外部クロック信号をカウント信号によって遅延させ、テスト信号に応答して、前記遅れた外部クロック信号から内部クロック信号及びデータ信号を生成するデータ生成部と、前記内部クロック信号に同期して、前記データ信号をバッファリングした信号をラッチするデータラッチと、前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号からフラグ信号を生成するフラグ信号生成部と、前記フラグ信号に応答して前記カウント信号をカウンティングするカウンターと、を含む構成とした。

(もっと読む)

クロック信号生成装置および離散時間型回路

【課題】電源電圧、環境温度などの外部変動要因により、離散時間型回路において必要となるクロック信号に変動が生じた場合などにおいて、離散時間型回路が必要とするノンオーバーラップ時間、およびクロック信号のデューティ比を最適に設定することができるクロック信号生成装置を提供すること。

【解決手段】本発明のクロック信号生成装置において、クロック信号遅延算出部は、クロック信号生成回路の可変遅延回路における外部変動要因による遅延特性をモニターする遅延検出回路を有して、N相のクロック信号の遅延量を算出し、クロック信号遅延制御部は、遅延変動データ部に記憶されている外部変動要因をパラメータとした遅延変動データと、算出されたN相のクロック信号の遅延量とに基づいて、可変遅延回路における遅延量を可変するよう構成されている。

(もっと読む)

ピークレベル検出装置

【課題】1ビットオーディオ信号のピーク値を求めることを、低演算量かつ高精度で実現可能な装置を提供すること。

【解決手段】1ビットストリームが供給されるとディレイバッファ30に順次データが書き込み記憶される。そして、ピーク位置検出部10が、ディレイバッファ30に記憶されたピーク値のアドレスである最大ピークアドレスを検出しこれをデータ読み出し部20に送る。データ読み出し部20は、送られてきた検出された最大ピークアドレスに応じてディレイバッファ30の対応するデータを読み出す。そして、LPF40は、この読み出されたデータの低域を通過させ、最後にABS部50が信号を絶対値化してマルチビットピーク値を出力する。

(もっと読む)

時間差に関するデータを評価する装置及び方法、並びにディレイラインを較正する装置及び方法

2つの事象の時間差に関するデータを評価する装置は、複数の段(101、102、103、104)を有するディレイライン100を含む。各段は第1部分の第1遅延と第2部分の第2遅延との遅延差を有する。この遅延差を各段の位相アービタ(105)が測定して、2つの事象のうちの第1部分の第1事象が第2部分の第2事象より先か後かを示す指示信号を出力する。合計値(201)を得るために、複数の段の指示信号を合計する合計デバイス(200)を備える。合計値は時間差の評価を示す。 (もっと読む)

フェーズロックループにおけるデジタル制御された発振器の出力のディザリング

PLLのデジタル制御された発振器(DCO)は、DCO_OUT信号がディザされた間隔で変化する周波数を持つように、ディザされる。一例では、DCOは、入って来るデジタルチューニングワードのディザされていないストリームを受け取り、ディザされた基準クロック信号REFDを受け取り、DCO_OUT信号を出力し、その周波数変化がディザされた間隔で起こるようになっている。PLLがセルラー電話の送信機の局部発振器で用いられる場合、DCOの新規なディザリングは、デジタルイメージノイズが、メイン局部発振器周波数からの特定の周波数オフセットで、より少なくなるように、デジタルイメージノイズを周波数拡散する。デジタルイメージノイズの周波数拡散によって、PLL基準クロックの周波数を増大する必要なく、ノイズの仕様を満たすことが可能になる。基準クロックの周波数の増大を回避して、ノイズの仕様を満たすことにより、パワーの消費の増大が回避される。  (もっと読む)

(もっと読む)

半導体装置

【課題】Loopbackテストの際に電圧振幅マージン不足の半導体装置が次工程へと流出するのを防止する。

【解決手段】シリアライザ17は、テストモード期間にクロック信号CLK1に応じてパタン発生器20が出力するパラレルのテストパタン信号をシリアル信号に変換して出力バッファ16よりテスト治具側の外部ループバックパスへ出力する。CPU21は、遅延制御信号DLC1,DLC2によって一方の可変遅延素子VDL1,VDL2の遅延時間を制御する。入力バッファ10の出力であるテストパタン信号VRxとLSIテスタ等より印加される外部基準電圧Vrefとの差動信号VRx1がCDR12に印加され、クロック信号CLK2が生成される。両信号VRx,CLK2の一方の位相が変更されて、外部基準電圧Vrefの値毎にタイミングマージンがチェックされる。

(もっと読む)

クロック信号生成装置

【課題】本発明は、温度特性、電源電圧特性、個体バラツキを吸収し、最適なノンオーバーラップ時間を有する2相クロック信号を確実に生成できる信頼性の高いクロック信号生成装置を提供することを目的とする。

【解決手段】本発明のクロック信号生成装置は、ノンオーバーラップクロック信号を使用する負荷回路において使用される2相クロック信号の遅延時間を可変する可変遅延器と、2相クロック信号におけるHレベル区間のノンオーバーラップ時間を検出し、ノンオーバーラップ時間に応じた検出信号を出力するノンオーバーラップ検出器と、ノンオーバーラップ検出器からの検出信号に基づいて可変遅延器を制御する制御信号を生成する制御信号生成部と、を備えている。

(もっと読む)

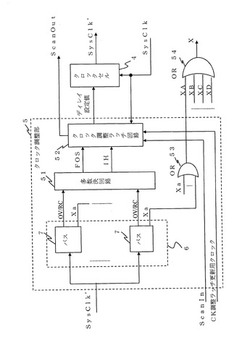

半導体装置

【課題】高速なクロックを必要とせずに、時間分解能を向上させたデジタルPWM制御を実現できる半導体装置を提供する。

【解決手段】複数段の第1遅延素子を有し、これら第1遅延素子に印加される制御電圧に応じて発振周波数が制御される電圧制御型クロック発生回路と、直列に接続された複数段の第2遅延素子を有する遅延回路と、複数段の第2遅延素子がそれぞれ出力するパルス信号の中から1つを選択する選択回路と、を備え、第1遅延素子と第2遅延素子とは同じ半導体基板に形成された同じ構成の遅延素子であり、第2遅延素子の遅延量は制御電圧に応じて調整される。

(もっと読む)

DLL回路、および半導体装置

【課題】DLLクロックが消失した場合に、位相検知における誤判定の結果を基に、遅延量が更新されることを回避し、ロック制御におけるDLLクロックサイクルの短縮化と、DLL回路の動作安定性の向上を図る。

【解決手段】本発明のDLL回路は、入力されるクロック信号の遅延量を制御する遅延信号を出力する遅延制御回路13と、この遅延信号に基づいた遅延量をクロック信号に付加し、DLLクロックとして出力する遅延回路12と、DLLクロック信号のクロッキング動作の有無を検知するDLLクロック検知回路31とを備える。そして、DLLクロック検知回路31は、DLLクロックのクロッキング動作が検知されない場合に、遅延制御回路13による遅延量の更新制御を停止させる。

(もっと読む)

半導体集積回路

【課題】複数のノイズパルスが連続して印加される場合においてもノイズを除去する能力を高めたノイズ除去回路を含む半導体集積回路を提供する。

【解決手段】この半導体集積回路は、入力信号を遅延する直列接続された複数の遅延回路と、複数の遅延回路によって互いに時間差が与えられた少なくとも3つの信号の論理積を求めることによってセット信号を生成する第1の論理回路と、複数の遅延回路によって互いに時間差が与えられた少なくとも3つの信号の論理和を求めることによってリセット信号を生成する第2の論理回路と、第1の論理回路によって生成されるセット信号によってセットされ、第2の論理回路によって生成されるリセット信号によってリセットされることにより、正論理の入力信号からパルス状のノイズが除去された出力信号を生成するRSラッチ回路とを具備する。

(もっと読む)

相補信号生成回路

【課題】 容量素子のみによるこれまでのスキュー調整方法よりもスキューの微調整を可能にした相補信号生成回路を提供する。

【解決手段】 本発明による相補信号生成回路は、複数のインバータ(901、904、905、906)を含む第1の信号伝達経路と、インバータ(901、907、908)と抵抗素子903を含む第2の伝達経路とを有する。

(もっと読む)

161 - 180 / 417

[ Back to top ]