Fターム[5J039KK13]の内容

Fターム[5J039KK13]に分類される特許

401 - 417 / 417

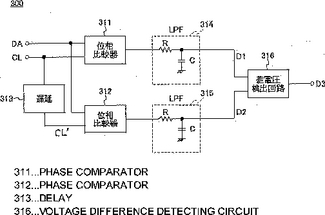

位相比較利得検出回路、誤同期検出回路及びPLL回路

PLLの位相比較利得検出回路において、データ信号DAとクロック信号CLとの間の位相を比較すると共に、データ信号DAとクロック信号CLを所定の遅延量だけ遅延したクロック信号CL’との間の位相を比較し、それぞれの位相比較結果どうしの差と上記所定の遅延量とに基づいて位相比較利得を検出する位相比較利得検出回路。  (もっと読む)

(もっと読む)

混成信号集積回路

本発明は、混成信号集積回路、すなわちアナログ回路とデジタル回路の両方を備える集積回路に関する。本発明は特に、このような装置内のノイズ低減に関する。デジタル回路がアナログ回路と同じ集積回路装置内に含まれる場合は、デジタル回路がかなりの量のノイズの追加の発生源となり得る。その結果、アナログ信号にクロストーク、電気的干渉、および信号歪みが加えられる。本発明は、アナログ回路(26)とデジタル回路(29、30)を備える集積回路であって、デジタル回路がASM(30)を含む集積回路を提供する。ASMは、クロック信号を必要としない。その動作は適切な入力条件によってトリガされるが、SSMとは異なり、その入力に変化がないときはアイドルとなり、デジタル回路によって発生されるノイズ・レベルを低減する。  (もっと読む)

(もっと読む)

ジッタ印加回路、及び試験装置

【課題】広帯域、高分解能、大振幅の位相ジッタ成分を、クロック信号に容易に印加することができるジッタ印加回路を提供する。

【解決部】与えられるジッタデータに応じた位相ジッタ成分を含むクロック信号を生成するジッタ印加回路であって、与えられる基準信号に応じて発振信号を生成するPLL回路と、発振信号を遅延させたクロック信号を出力する可変遅延回路と、ジッタデータの低周波成分に基づいてPLL回路の発振周波数を制御し、発振信号に位相ジッタ成分の低周波成分を印加する低周波印加部と、ジッタデータの高周波成分に基づいて可変遅延回路における遅延量を制御し、クロック信号に位相ジッタ成分の高周波成分を印加する高周波印加部とを備えるジッタ印加回路を提供する。

(もっと読む)

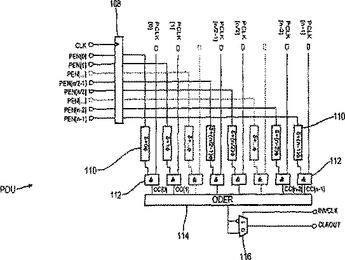

所定のクロック信号特性を有するクロック信号を生成するための方法および装置

所定のクロック信号特性を有するクロック信号(CLKOUT)を生成するための方法および装置であって、まずマスタクロック信号(CLK)に関して本質的に同一の周波数およびそれぞれ異なる位相関係を有する多数のクロック信号(PCLK[n−1:0])を準備し、次いで、準備された多数のクロック信号から(生成されるクロック信号に従って準備された制御信号(PEN[])に基づいて)所定のクロック信号を選択し、選択したクロック信号を組み合わせて所望のクロック信号(CLKOUT)を生成する。  (もっと読む)

(もっと読む)

デジタルオーディオ用の信号伝送装置

【課題】 音質改善のためユーザーが好みに応じてデジタルオーディオ信号のパルス幅を可変できるようにしたデジタルオーディオ用の信号伝送装置を提供する。

【解決手段】 送信機1から送信されるデジタルオーディオ信号をデジタル受信機が備えるDAコンバータ2に伝送するデジタルオーディオ用の信号伝送装置10において、入力バッファ回路110および出力バッファ回路120を含み所定の直流電源130で動作する伝送器本体100と、伝送器本体の出力側から引き出されDAコンバータに接続される出力ケーブル200とを備え、入力バッファ回路110の波形成形回路(インバータ回路)112にて入力パルス波形と所定の閾値電圧との交点を立ち上がり・立ち下がりポイントとして上記デジタルオーディオ信号を立ち上がり・立ち下がり時間が速いパルス波形に波形成形する際、バイアス電圧調整回路115により例えばパルス波形の中心電圧を可変としてパルス幅の異なるパルス波形が得られるようにする。

(もっと読む)

遅延同期ループ回路の良否検査方法及び遅延同期ループ回路の良否検査回路

【課題】

ディジタルデータをもとに良否判定可能な比較的安価な検査装置を用いて遅延同期ループ回路の良否検査を行うことができる遅延同期ループ回路の良否検査方法及び、遅延同期ループ回路の良否検査回路を提供する。

【解決手段】

基準信号を所定時間ずつ遅延させたN個のタップ信号を出力する遅延同期ループ回路の良否検査回路及びこの良否検査回路により行う良否検査方法において、各タップ信号をクロック信号とするN個のフリップフロップといずれかのタップ信号をクロック信号とするフリップフロップとを直列接続することによってシフトレジスタを形成し、このシフトレジスタを基準信号の1周期分動作させて、N個目のフリップフロップの出力信号とN+1個目のフリップフロップの出力信号とに基づいて遅延同期ループ回路の良否を判定することとした。

(もっと読む)

スプレッドスペクトラムクロック生成器及びその変調方法

【課題】製造バラツキ、電源電圧、使用温度、使用周波数が変化しても所望の変調度の周波数変調クロックを供給可能とするスプレッドスペクトラムクロック生成回路を提供する。

【解決手段】制御信号に応じて制御周期間隔で発振周期を可変に制御する第1の遅延制御型発振回路104と、第1の遅延制御型発振回路の出力を分周したクロック信号fo1と、位相比較結果に基づき周波数制御信号Cを出力する制御回路103と、変調最大値Aを決定する変調最大値決定回路106と、変調最大値A内で変調制御信号αを生成する変調信号発生回路107と、出力クロック信号の発振周期を制御信号に応じ制御周期間隔に可変に制御する第2の遅延制御型発振回路108を備えている。

(もっと読む)

クロックフィルタ回路及びクロックフィルタテスト回路

【課題】 入力信号に対する位相遅延の少ない、不要な高周波信号を除去したクロック信号を得ることができるクロックフィルタ回路を提供することを課題とする。

【解決手段】 ドレイン間が抵抗素子102を介して接続され、ゲートに入力クロック信号CLK1が入力される、ソースがVDDに接続されたトランジスタ100及び、ソースが接地されたトランジスタ102、トランジスタ102のドレインと接地とに接続されたコンデンサ103、トランジスタ100のドレインに接続されたCMOSインバータ104を備えた遅延回路2、遅延回路2と同様の構成で信号CLK1の代わりに、信号CLK1の反転が入力される遅延回路3、信号CLK1の反転と遅延回路2の出力とを入力とするAND回路4、入力クロック信号CLK1と遅延回路3の出力とを入力とするAND回路5、及びAND回路4の出力をRESETとし、AND回路5の出力をSETとするRS型フリップフロップを備えた。

(もっと読む)

SMD任意逓倍回路

【課題】

入力信号に同期し逓倍数が可変に設定される信号を出力する逓倍回路の提供。

【解決手段】

入力信号の周波数を可変に逓倍した出力信号を出力する逓倍回路であって、入力信号の周期を測定する周期測定用の遅延回路と、周期測定用の遅延回路で測定された周期に基づき、遅延時間が可変に設定され、遅延時間を再現する遅延再現用の遅延回路とを備えた同期遅延回路10と、同期遅延回路から出力される位相が異なる複数の信号を受けて多重化する多重回路20と、設定逓倍値にしたがって、周期測定用の遅延回路の遅延段数、遅延再現用の複数の遅延回路の段数の設定を可変に設定する制御回路30とを備え、多重回路20から入力信号に同期しその周波数を逓倍した出力信号が出力される。

(もっと読む)

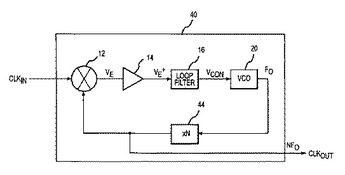

低電力と低いタイミング・ジッタのフェーズ・ロック・ループと方法

フェーズ・ロック・ループは、入力クロック信号から出力クロック信号を生成する。出力クロック信号は、クロック・ツリーを通して結合されて、出力クロック信号の位相を入力クロック信号の位相と比較する位相検出器にフィード・バックされる。出力クロック信号は、位相検出器から出力を受け取るように結合された制御入力を有する電圧制御発振器と、電圧制御発振器の出力に結合された周波数逓倍器とによって生成される。を持っている電圧制御発振器によって生成される。結果として、電圧制御発振器が相対的に低い周波数で動作することによって相対的に小さな電力を使用する一方、周波数逓倍器により生成されたCLKOUT信号は、相対的に高い周波数を持っている。  (もっと読む)

(もっと読む)

進歩した位相等化を用いたDLL位相検出

【解決手段】同期回路(例えば、遅延ロックドループ即ちDLL)の初期化中にクロックのシフトモードを開始及び終了するシステム及び方法が開示されている。初期化の際に、DLLは、ForceSL(Force Shift Left)モード及びOn1xモード(即ち、クロックサイクル毎にレフトシフト)に入る。フィードバッククロックは、(システムクロックから順次供給される)リファレンスクロックの位相をトラックし、コース位相検出ウインドウに与えられる前に、最初にコース位相検出器内で遅延される。フィードバッククロックの2つの遅延バージョンが、リファレンスクロックでサンプリングされて、一組の位相情報信号が生成される。それら信号は、その後、アドバンスド等位相(APHEQ)信号を確立するために使用される。APHEQ信号は、PHEQ(位相等化)位相のオンセットを進め、ForceSLモード及びOn1xモードの終了に使用される。これによって、クロックジッタによる不適切なForceSLの終了、又はOn1xが終了する間におけるフィードバックパスのオーバーシューティングが防止される。不適切なForceSLの終了及びOn1xのオーバーシューティングの問題が避けられることで、DLLのロッキングタイムはより速くなる。 (もっと読む)

差動位相検出器

【課題】本発明は、完全にデジタルで実装される差動位相検出器と、該差動位相検出器のための補間器に関する。

【解決手段】本発明によると、4つの光検出器のデジタル化された信号(A、B、C、D)からトラッキング誤差信号を生成する差動位相検出器は、デジタル化された信号(A、B、C、D)を時間多重するマルチプレクサと、時間多重されたデジタル化信号(A、B、C、D)からサンプルを同期化するためのデマルチプレクサ/補間器を含む。デマルチプレクサ/補間器は、好ましくは、4個の信号の時間多重信号を受信し、時間多重信号の半分の速度である4チャネルの信号を生成する。

(もっと読む)

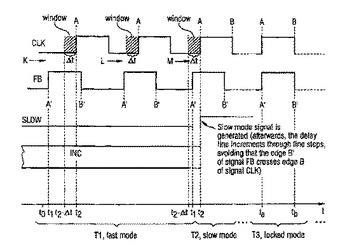

クロック信号を同期化する際に使用する装置、および、クロック信号同期化方法

本発明は、可変制御可能な遅延時間(tvar)を有する遅延手段(2)を備え、クロック信号(CLK)またはこのクロック信号(CLK)から得られる信号が、遅延手段(2)に入力され、可変制御可能な遅延時間(tvar)だけ遅延され、遅延されたクロック信号(DQS)の形状で出力される、クロック信号同期化方法、および、クロック信号(CLK)の同期化に使用する装置(1)に関するものである。本発明は、遅延手段(2)から出力される遅延されたクロック信号(DQS)またはこのクロック信号(DQS)から得られる信号(FB)の上記クロックエッジ(A’)が、上記クロック信号(CLK)またはこのクロック信号(CLK)から得られる信号の対応するクロックエッジ(A)の前の所定の時間窓の内側にあるかどうかを決定するためのデバイス(5)が設けられていることを特徴とする。  (もっと読む)

(もっと読む)

処理素子の連鎖を備える電子回路

論理回路(14)とストレージ素子(12)とを備える連鎖状の処理素子(10a,10,10b)が与えられる。連鎖における末端の処理素子(10b)を除くすべてのストレージ素子(12)は、連鎖における次の処理素子(10a,10,10b)の論理回路(14)に結合される1つ又は複数の出力を持つ。タイミング回路(16)は、処理素子(10a,10,10b)の個別の1つにおいてストレージ素子(12)が論理回路(14)からデータをロードする個別のローディングの時間点を制御する。データは、連鎖において連続的に互いに先行する処理素子(10a,10,10b)で連続的に遅れてロードされる。末端の処理素子(10b)における連続的なローディングの時間点間の時間間隔は、末端の処理素子(10)以外のすべての処理素子(10a,10)をロードするローディングの時間点を含む。  (もっと読む)

(もっと読む)

論理回路におけるクロック分配のための遅延マッチング

【課題】論理回路におけるクロック分配のための遅延マッチング。

【解決手段】論理回路内部に分配された複数の信号間の伝播遅延差を補正するための技術。遅延マッチング回路は、フロップによって生成された内部のクロックからQへの遅延を模倣する。遅延マッチング回路は、再分配されようとしている、クロック信号のような原初の信号の伝播経路内に置かれる。一般に、遅延マッチング回路は、特定の構成を有する伝播ゲート・マルチプレクサを含むことができる。遅延マッチング回路は、原初の信号の分割された版により経験されたクロックからQへの遅延に実質的に等しい遅延を課する。このようにして、遅延マッチング回路は、原初の信号と分割された信号の立ち上がり端と立ち下がり端とが、実質的に一致することを確実にし、同期した動作を可能にする。これゆえ、遅延マッチング回路は、再分配された信号と分割された信号を同期させることができる。

(もっと読む)

多電源半導体装置

複数のブロック31、32により構成され、各ブロック31、32が独立したクロック回路41、42を有し、可変電源101により動作する多電源半導体装置において、クロック生成回路10から複数のブロック32に供給されるクロック信号に、可変電源101の電圧値に基づいて遅延量が変化する可変遅延回路20を設ける。このことにより、可変電源101の電源電圧を変化させた場合でも、ブロック間のクロックスキューが低減される。 (もっと読む)

長いオンチップバスの動作

テクノロジの縮尺度のために、オンチップ相互接続は幅が狭くなってきており、このような相互接続の高さは、幅に線形に比例しない。これにより、隣接配線とのカップリング容量が増加し、クロストークが高くなる。それはまた、配線の受信側におけるRC応答の不十分さに起因する性能の不十分さに繋がり、非常にノイズの多い環境では、故障の原因になることさえある。受信機スイッチング閾値がバスラインにおいて検出されたノイズに応じて調整される適応閾値構成が提案される。これらのノイズレベルは、フロントエンド処理(トランジスタ性能)とバックエンド処理(金属抵抗、容量、幅及びスペーシング)の両方に依存する。従って、回路は、プロセス変動を自動的に補償する。  (もっと読む)

(もっと読む)

401 - 417 / 417

[ Back to top ]