Fターム[5J039KK13]の内容

Fターム[5J039KK13]に分類される特許

261 - 280 / 417

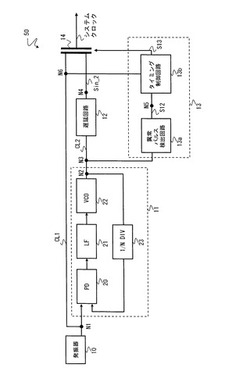

クロック生成回路、クロック選択回路、及び半導体集積回路

【課題】 PLL回路から出力される異常波形のクロックにより他の機能回路が誤動作すること。

【解決手段】 クロック生成回路50は、クロックCL1に同期したクロックCL2を出力するPLL回路11と、クロックCL1又はクロックCL2を出力するセレクタ14と、PLL回路11からのクロックCL2で異常波形のパルスが検出されたとき、クロックCL2に代えてクロックCL1を出力させる切替信号をセレクタ14に出力する切替信号生成回路13と、切替信号に基づいてセレクタ14がクロックCL2からクロックCL1に出力クロックを切り替えた後、異常波形のパルスがセレクタ14に入力されるように、PLL回路11からのクロックCL2を遅延させる遅延回路12と、を備える。

(もっと読む)

ディジタル信号の位相差検出方法

【課題】比較的低速かつ小規模のディジタル回路により精度の高い位相差検出を行う。

【解決手段】トラッキングサーボ回路10において、入力部のローパスフィルタ(LPF)12〜18および利得制御増幅器(GCA)20〜26はアナログ回路であり、A/D変換器28〜34より後段のオフセット・キャンセル回路36〜42、イコライザ(EQ)44〜50、位相差検出器52,54、加算器56、LPF58、利得制御増幅器(GCA)60およびサーボDSP154はすべてディジタル回路で構成される。両位相差検出器52,54は本発明の位相差検出方法にしたがって両入力信号の位相差を検出する。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】デューティ補正された遅延固定クロックを生成することができ、1つのDLLだけでもデューティ補正が可能で、かつ、入力されるクロック信号のデューティ比を効率的に補正して出力することができる半導体メモリ装置を提供すること。

【解決手段】遅延固定動作により遅延固定クロックを生成するDLL回路と、前記遅延固定クロックと、その遅延固定クロックの偶数倍に分周したクロックとを用いて、前記遅延固定クロックのデューティ比を補正するデューティ補正回路とを備える半導体メモリ装置を提供する。

(もっと読む)

ノイズ除去回路

【課題】少ない素子数のノイズ除去回路で、入力信号のノイズ除去を行う。

【解決手段】ノイズ除去回路30には、信号処理部1及びシュミットトリガ回路2が設けられる。信号処理部1には、2入力NOR回路NOR1、インバータINV1、Pch MOSトランジスタPT1、及びNch MOSトランジスタNT1が設けられ、クロック信号CLK及びイネーブル信号ENbを入力する。シュミットトリガ回路2には、インバータINV2、Pch MOSトランジスタPT2、Pch MOSトランジスタPT3、Nch MOSトランジスタNT2、及びNch MOSトランジスタNT3が設けられ、クロック信号CLK及び信号処理部1から出力される2つの信号を入力し、ノイズが除去されたクロック信号CLKを出力信号Soutとして出力する。

(もっと読む)

メータ駆動回路

【課題】 ゲインリダクションメータとゲインメータに同じ構成のメータ駆動回路を使用しても、ゲインリダクションメータにおいて圧縮率の極小値を明確に認識できること。

【解決手段】 メータ駆動回路40は、入力されたエンベロープ信号を反転してエンベロープフォロワ部40bに入力することのできる第1の選択部SWaと、エンベロープフォロワ部40bの出力を反転してゲインリダクションメータに供給することのできる第2の選択部SWbを備えている。

(もっと読む)

クロックスキューコントローラ及びそれを備える集積回路

【課題】クロックスキューを補償することができるコントローラを備える集積回路を提供する。

【解決手段】第1クロックマッシュに入力される第1クロックと第2クロックマッシュに入力される第2クロックとの間のスキューを調節するためのクロックスキューコントローラを備える。クロックスキューコントローラは、第1出力クロックと第2出力クロックとの間の遅延時間に対応するパルス信号を発生するパルス発生器と、パルス信号のパルス幅に対応するデジタル信号を出力するパルス幅検出器と、デジタル信号に対応する時間だけ、第1及び第2クロックのうちのいずれか一つを遅延させるクロック遅延調節器と、を備えて、クロックマッシュの間のクロックスキューを検出し、該検出されたスキューに対応する遅延時間だけクロックマッシュに供給されるクロック等の遅延時間を調節することができる。

(もっと読む)

高ヒステリシス幅入力回路

【課題】従来のヒステリシス入力回路は等価的にP型MOSFETとN型MOSFETのインバータ回路のβ比を変えて、ロジックレベルのヒステリシスを作っていたが、この方式では電源電圧が低下するとヒステリシス幅が極端に小さくなった。また、電源電圧の広範囲の変動に対してヒステリシス幅を確保することは難しかった。また、ロジックレベルを形成するのにP型とN型MOSFETを用いるので形状比の設定にやや無理があり、また製造工程でのバラツキの影響を受けやすかった。

【解決手段】入力インバータ回路と正極の電源にP型、N型MOSFET、負極の電源にN型、P型MOSFETと、及び前状態を過渡的にでも記憶・遅延する遅延回路を設け、前状態により、前記各MOSFETをオン・オフすることにより、ヒステリシス特性を得る。電圧特性が異なるMOSFETを使い分けることにより、前述の課題が解消できた。

(もっと読む)

電圧制御発振回路

【課題】動作が誤発振状態または準安定状態となったことを検出し、誤発振状態または準安定状態から抜け出して正常な発振状態にとすることができるVCOをを提供する。

【解決手段】本発明の電圧制御発振回路は、互いに逆相の差動のクロック信号が入力される差動遅延素子を縦続接続し、バイアス電圧によって差動遅延素子に流れる電流の量を制御することで、該差動のクロック信号の遅延量を制御する差動リングオシレータ型の電圧制御発振回路であり、いずれかの差動遅延素子の差動出力の出力電圧と、異常動作を検出する電圧に設定されたリファレンス電圧とを比較することにより異常発振を検出して検出信号を出力する位相検出部と、差動遅延素子毎に設けられ、検出信号が入力されると、差動出力対間の電位差を増幅するクロスカップル回路とを有している。

(もっと読む)

クロック制御回路、集積回路装置及び電子機器

【課題】ノイズフィルタでは完全には除去することができないようなノイズがクロック信号に発生した場合でも、このクロック信号で動作する回路の誤動作を防止することができるクロック制御回路を提供すること。

【解決手段】クロック制御回路10は、発振クロック22の電圧が所定の範囲にあるか否かを判断し、発振クロック22の電圧が所定の範囲にない時はノイズ検出信号128を生成するノイズ検出回路120と、ノイズ検出信号128に基づいて、少なくとも所定の期間、クロック出力停止信号138を生成するクロック出力停止信号生成回路130と、発振クロックを所定の時間遅延させた遅延クロック信号148を生成する遅延クロック生成回路140と、クロック出力停止信号138が存在する期間は、遅延クロック信号148の外部への出力を停止するように制御するクロック出力停止制御回路150と、を含む。

(もっと読む)

半導体装置

【課題】テスト中に所望の位相に対して追随できるテスト回路を備え、安価にDDRifのテストを行うことを目的としている。

【解決手段】本発明における半導体装置は、位相シフト量を決定するDLL200と、テストモード時に所定位相ずらす演算回路300と、位相シフト量を設定するレジスタ11〜16と、設定した位相にシフトして信号の送受信を行う伝送回路10とを備える。伝送回路10は、第1の信号を設定した位相にシフトする位相シフタ1と、テストモード時に第1の信号をループバックする双方向バッファ21と、双方向バッファ21から出力された信号の位相をシフトする位相シフタ2と、第3の信号の位相をシフトする位相シフタ3と、テストモード時に第3の信号をループバックする双方向バッファ22と、双方向バッファ22から出力された信号の位相をシフトする位相シフタ4と、位相シフタ2,4の出力信号を取り出すFIFO30とを備える。

(もっと読む)

フィルタ回路

【課題】連続する複数のサンプリングタイミングで混入する幅狭のノイズを除去する。

【解決手段】フィルタ回路1は入力信号処理回路2と信号レベル判定回路3とを備える。入力信号処理回路2は、クロック信号CLKでデジタル入力信号Dinをサンプリングして保持し、隣り合うサンプリングタイミングの間においてデジタル入力信号Dinにレベル変化が生じた場合、その保持した信号を反転する。信号レベル判定回路3は、サンプリング入力信号Dsをクロック信号CLKで複数段に順次遅延させ、遅延させた各段の信号が全て一致したときに、その一致したレベルを持つ信号Doutを出力する。

(もっと読む)

通信仲介デバイス

【課題】 アイドル時の消費電力の削減化が図られた通信仲介デバイスを提供する。

【解決手段】 内部クロック生成回路15が、HSアイドル検出回路10による、第1の間隔である125μsよりも短い時間間隔で第2のパケットが到着したことの検出を受けて、480MHzの周波数のクロックCLK1の生成を開始して、HSDLL16,エラスティシティバッファ17,Rxデータデシリアライザ18,Txデータシリアライザ21に供給し、第1のパケットの到着の時間間隔が125μsに戻ったことの検出を受けて、480MHzの周波数のクロックCLK1の生成を停止する。

(もっと読む)

半導体集積回路

【課題】本発明は、Ser/Des回路において、休眠ステートからパワーアップの状態へ遷移した際の受信エラーを減少できるようにする。

【解決手段】たとえば、受信機21が、休眠ステートP1からパワーアップの状態P0に遷移したとする。すると、リセット制御回路21mは、ディレイ回路21m-1によって、PLL31からのシステムクロックのカウントを開始する。そして、ディレイ回路21m-1がXサイクルをカウントした後に、リセット制御回路21mは、ディジタルフィルタ21eおよびPI制御回路21fのリセットを解除するように構成されている。

(もっと読む)

情報処理装置および情報処理方法

【課題】低実装コスト、低消費電力、マルチスタンダード対応のサンプリングレート変換を実現する。

【解決手段】バッファ142は、シリアル信号をLビットのパラレル信号に変換してデシメーションし、ある時刻の入力信号からFIRの次数分だけ遅延した信号までを1グループの入力系列とする。セレクタブロック143のセレクタ151は、Lビットの入力に対して、後段の加算平均または間引きの係数に対応するNビットの信号が出力されるように、入力信号を選択、補間する。加算処理部144の加算または出力選択部161は、コントローラ141の制御に基づいて、セレクタ151のNビットの出力を加算して出力するか、Nビットのうちの1ビットを出力する。デジタルフィルタ145は、加算または間引きによって得られた系列とFIRフィルタのタップ係数を用いて、フィルタの演算を実行する。本発明は、受信装置などのデジタルブロックに適用できる。

(もっと読む)

SET耐性レジスタ

【課題】シングル・イベント・トランジェント効果を緩和するように構成されたレジスタまたはラッチを提供する。

【解決手段】放射線耐性のラッチ、および動作の方法。SET効果を緩和するために、ラッチは、内部に配置されたパルス除去インバータを含む。パルス除去インバータは、入力論理信号を受け取り、それを遅延させ、その遅延された論理信号と入力論理信号とを比較する。入力論理信号と遅延された論理信号とが同等である場合、遅延された論理信号は、パルス除去インバータを通って伝搬することができる。パルス除去インバータが内部に配置されるので、ラッチの上流または内部、あるいはクロック信号で発生するSET事象が緩和される。

(もっと読む)

遅延信号生成装置、および遅延量制御方法

【課題】短い時間で精度良くデータを記録する。

【解決手段】図1の遅延信号生成装置は、光ディスク記録装置に設けられる。検出部105は、第2遅延信号と第1遅延信号の遅延量の差が検出用パルス信号のパルス幅となるときの第2遅延セレクト信号を求め、その第2遅延セレクト信号に対応する出力位置と第1遅延セレクト信号に対応する出力位置との間にあるバッファの数を、検出結果として出力する。遅延量制御部106は、上記検出結果に基づいて、制御入力信号を求める。記録用ディレイライン101は、上記制御入力信号に応じた遅延量だけ記録用クロックを遅延させる。制御入力信号を求める遅延キャリブレーション動作は、記録中に行われる。

(もっと読む)

半導体集積回路

【課題】半導体集積回路の外部入出力信号のタイミングを自動的に調整する。

【解決手段】半導体集積回路は、内部セルの動作クロック信号に同期して当該内部セルから出力されたデータ信号又は外部から入力されたデータ信号をラッチするフリップフロップ(10)を有する入出力セル(1)を備えている。

(もっと読む)

半導体集積回路

【課題】半導体集積回路内でクロックジッタを定量的に測定する。

【解決手段】n個(nは2以上の整数)の直列に接続された遅延素子をそれぞれ有し、1段目の遅延素子には同一の入力信号が入力され、k(kは1≦k≦n−1をみたす整数)段目の遅延素子の出力信号がk+1段目の遅延素子に入力される第1及び第2の遅延回路1,2と、n個のエッジ検出部E及び読み出し部20を有し、第j(jは1≦j≦nを満たす整数)のエッジ検出部は前記第1の遅延回路のj段目の遅延素子の出力信号及び前記第2の遅延回路のn−j+1段目の遅延素子の出力信号が入力され、この2つの信号の立ち上がり又は立ち下がり変化の期間が重なるか否かを検出してその検出回数をカウントし、前記読み出し部が前記カウントされた検出回数を読み出す検出回路3と、を含む。

(もっと読む)

半導体装置、半導体集積回路装置、及び許容位相差測定回路

【課題】低コストで電流ピークを効果的に抑制することができる半導体装置を得る。

【解決手段】ステップST1において、モジュールA21とモジュールB22とのクロック位相を一致させた後、ステップST2において、モジュールA21からモジュールB22にデータ転送を行う。その後、ステップST3において、モジュールA21のクロックCLKAとモジュールB22のクロックCLKBとのクロック位相差を所定の大きさに設定した後、ステップST4において、モジュールA21とモジュールB22とがそれぞれ独立に所定の演算処理を行う。そして、ステップST5において、モジュールA21のクロックCLKAとCPU25のクロックCLKPとの位相を一致させた後、ステップST6においてモジュールA21の演算結果をCPU25で読み取る。

(もっと読む)

DLL回路

【課題】 クロックの立ち上がり及び立ち下がりに同期した内部クロックを生成するDLL回路においては、高精度が要求されることから回路規模が大きくなるという問題がある。

【解決手段】 Rise用の遅延調整回路とFall用の遅延調整回路を備え、Fall用の遅延調整回路にはRise用の遅延調整回路でRise側を調整したクロックを入力する。入力されるクロックのRise側が調整されていることから、Fall側の遅延差は非常に小さくなる。そのため、Fall用の遅延調整回路、カウンタの回路規模が大幅に削減できる。その結果少ない回路規模で、高精度のDLL回路が得られる。

(もっと読む)

261 - 280 / 417

[ Back to top ]