Fターム[5J039MM09]の内容

Fターム[5J039MM09]に分類される特許

1 - 20 / 20

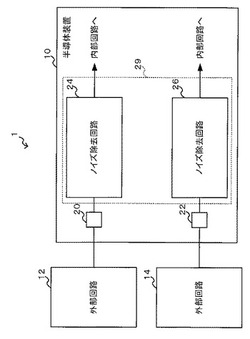

半導体装置及びノイズ除去装置

【課題】電源電圧の変動を伴うノイズに対して、入力される信号に応じた入力端子の種別によってそれぞれ異なる手法を用いることによりノイズ耐性が装置内で向上する。

【解決手段】外部回路12から入力端子20を介してノイズ除去回路24に発振信号が入力される。電源ノイズにより電源電圧が変動した場合は、ノードBにLレベルパルスのグリッチが発生し出力信号が反転する。OR回路48には、当該出力信号と、遅延回路46により遅延されてグリッチ(反転)のタイミングがずれた遅延信号と、が入力されるため出力信号は、反転せずHレベルを保つ。一方、外部回路14から入力端子22を介してノイズ除去回路26に遅延に関する制限が厳しい高周波の発振信号が入力される。シュミット回路52の入力と出力との間に接続された容量素子C7により、ノードAが電源電圧に追従して変動するため、ノードBにグリッチが発生せず、反転せずにHレベルを保つ。

(もっと読む)

集積回路

【課題】電源ノイズが存在する環境下において、位相同期回路の出力信号の特性劣化を軽減する。

【解決手段】基準信号源は、基本周波数を有する基準信号を生成する。位相同期回路102は、制御電圧に応じた周波数の信号を生成する電圧制御発振器106と、前記周波数の信号をN分周して第1分周信号を生成する第1分周器107と、第1分周信号と基準信号との位相差を検出する位相検出器103と、チャージポンプ104と、ループフィルタ105と、を含む。第2分周器は、電圧制御発振器により生成された信号をM分周して第2分周信号を生成する。信号処理回路は、第2分周信号に同期して動作する。基本周波数のK倍と、第2分周信号の周波数との差分の絶対値が、電圧制御発振器の入力から位相同期回路の出力までの伝達関数によって表される帯域通過フィルタの低域遮断周波数以下または高域遮断周波数以上となるように、NおよびMの値が決定されている。

(もっと読む)

半導体装置、電子機器、及び出力波形歪み改善方法

【課題】N本のクロック信号を出力した際に生ずる出力波形歪みを改善した装置構成を提供する。

【解決手段】半導体装置は、所定周波数の入力クロック信号CLK−Iを入力して同一周波数の複数のクロック信号CLK1からCLKNを出力する。前記入力クロック信号は遅延部1_1から遅延部1_N−1により所定の遅延時間差を与えられ、前記複数のクロック信号として出力される。前記複数のクロック信号の立ち上がり及び立ち下がりを分散することで、共通の電源レギュレータ11への負荷が低減する。

(もっと読む)

半導体装置及びデータ取込方法

【課題】電源ノイズによるデジタル信号の取込エラーを低減すること。

【解決手段】パルス制御信号に応じてスイッチング動作を行なうスイッチング回路120と、デジタル信号を取り込むデジタル信号保持回路111と、を備え、デジタル信号保持回路111は、スイッチング動作による電源ノイズの発生期間におけるデジタル信号の取り込みを回避するためのマスク信号をパルス制御信号から生成するマスク信号生成回路114を含み、電源ノイズの発生期間にはデジタル信号を取り込まず、電源ノイズの非発生期間に前記デジタル信号を取り込む半導体装置。

(もっと読む)

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

スペクトラム拡散クロック生成装置

【課題】生成されたスペクトラム拡散クロックを、各種タイミングを制御するカウンタのクロックとしても用いることのできるスペクトラム拡散クロック生成装置の提供。

【解決手段】SSC源クロック発生回路3,基準クロック発生回路5が発生するSSC源クロック,基準クロックは、16bitカウンタ7,9に入力されて、そのクロック数がカウンタ値cnt1,cnt2として計数される。カウンタ値cnt1,cnt2は、比較回路10に入力され、カウンタ値cnt1がカウンタ値cnt2よりも1以上大きくなると、比較回路10は比較結果cmpとしてLレベルの信号を出力する。すると、パルス生成回路21がLレベルの矩形パルス(間引き要求pls_cg)を出力し、AND回路31によりその間引き要求pls_cgとSSC源クロックとの論理積が計算されることによって、SSC源クロックが1クロック分間引かれる。

(もっと読む)

半導体発振回路および携帯電話

【課題】基準周波数生成回路は、ロジック回路の電源ノイズの影響を受けて、周波数偏差やピリオドジッターの悪化を引き起こしていた。

【解決手段】CPUや周辺回路などのロジック回路12の電源はレギュレータ13より供給し、基準周波数生成回路11の電源には電源の高周波ノイズを10dB以上の減衰量を持つローパスフィルター10を介してから供給する。これによりロジック回路12で発生する高周波ノイズ起因での周波数偏差やジッターの悪化を抑えることができ、この基準周波数をUARTシリアル回路に接続して通信ができる。

(もっと読む)

半導体回路および試験装置

【課題】電源電圧のリップルが信号処理回路に及ぼす影響を低減する。

【解決手段】第1信号処理回路10は、第1信号S1に所定の信号処理を施し、その特性値に変化を与えて第2信号S2を出力する。第2信号処理回路12は、第2信号S2に所定の信号処理を施し、その特性値に変化を与えて第3信号S3を出力する。第1、第2スイッチング電源20、22はそれぞれ、第1、第2信号処理回路10、12に対し電源電圧Vdd1、Vdd2を供給する。第1信号処理回路10が第1信号S1の特性値に与える変化量と、第2信号処理回路12が第2信号S2の特性値に与える変化量はそれぞれ、電源電圧Vdd1、Vdd2に対する依存性を有する。第1、第2スイッチング電源20、22の位相はそれぞれ、第1信号S1の特性値の変化量とその目標値との誤差と、第2信号S2の特性値の変化量とその目標値との誤差がキャンセルするように設定される。

(もっと読む)

電源装置及び電源装置におけるタイミング制御回路

【課題】電源投入時に流れる突入電流を削減すること。

【解決手段】商用電源2から電気機器3に電力を供給する電源装置1において、ON/OFFスイッチ22をONするとタイミング制御回路7で制御された無接点リレー6Aが交流波形の立ち下がりのゼロクロス点で交流電源電圧の供給を開始し、かつ、ON/OFFスイッチ22をOFFするとタイミング制御回路7Aで制御された無接点リレー6Aが交流波形の立ち下がりのゼロクロス点で交流電源電圧の供給を終了するようにした。

(もっと読む)

クロック信号生成回路、及びクロック信号生成回路の使用方法

【課題】リングオシレータを利用して基準クロック信号の周波数を逓倍した逓倍クロック信号を生成するクロック信号生成回路において、逓倍クロック信号のジッタを抑制する。

【解決手段】高速クロック発生回路2の主要部であるリングオシレータへの電源供給を時定数がτに設定されたローパスフィルタ23を介して行い、高速クロック信号CKrで基準クロック信号CKs(周波数fs)の周期をカウントする周期カウンタ4のカウント値(周期カウント値)DGを、基準クロック信号CKsに従って動作する逓倍クロック生成回路5が、nクロック周期で、逓倍クロック信号CKoに反映させる。そして、基準クロック発生回路3は、周波数fsがτ>n/fsを満たす基準クロック信号CKsを発生させる。

(もっと読む)

ノイズリダクション回路、および電子機器

【課題】簡単な回路構成で伝送路に入る信号の両電圧レベルに含まれるノイズの減少をする。

【解決手段】ノイズリダクション回路は、入力信号IS10と、この入力信号を遅延させる遅延ユニットDL10の出力信号DLS10との論理積を取る論理積ユニットまたは論理和を取る論理和ユニットのいずれか一方である少なくとも1つの第1の論理ユニット10と、第1の論理ユニットの後段側に設けられ、論理積ユニットまたは論理和ユニットのいずれかであって上記の一方とは異なる他方である少なくとも2つの第2の論理ユニット12、14と、を含み、少なくとも1つの第1の論理ユニット10および少なくとも2つの第2の論理ユニット12、14がカスケード接続されて構成される。

(もっと読む)

CML回路及びそれを用いたクロック分配回路

【課題】電源投入時やクロックゲーティング時などクロック停止状態から復帰する際にクロック配線や次段クロックドライバのRC成分の影響で最初の一定期間クロック波形が出なくなることを防ぎつつ通常動作時や低速動作するテスト時に消費電力や電源ノイズを低減すること、また過剰な駆動力によって発生するクロック波形のリンギングを低減する。

【解決手段】クロック停止状態から復帰する際にのみブースト回路12を動作させる。通常同作用バッファ13は、レファレンス信号REFがアクティブである間は、ずっと動作する。

(もっと読む)

インタフェース回路および2値データ伝送方法

【課題】受信側で2値データの受信前にノイズマージンを拡大したり、発生するノイズの低減を図ることのできるインタフェース回路および2値データ伝送方法を実現する。

【解決手段】送信データ104は送信バッファ103から受信側に送信され、入力バッファ112を経て第3のフリップフロップ回路113に取り込まれる。検出部105は送信データ104の経時的な論理変化を検出して、基準電圧制御部114から出力される基準電圧調整信号124を変化させて2値化の適正化を図ると共に、遅延調整部106から出力されるクロック信号の位相を変化させてデータの取り込みを調整する。

(もっと読む)

半導体集積回路

【課題】回路規模を大きくすることなく、複数の回路を動作させるための夫々のクロックの位相を容易に制御することが可能な半導体集積回路を提供する。

【解決手段】本発明の半導体集積回路40は、クロックを入力され、クロックの1周期分に相当する同相遅延素子段数CTを求める遅延制御手段41と、遅延制御手段41により求められた同相遅延素子段数CTから、所定量の遅延を発生させる遅延素子の段数DEGOUT1〜DEGOUTnを決定する遅延素子段数決定手段42と、クロックを遅延素子段数決定手段42により決定された遅延素子の段数分遅延させる遅延クロック生成手段431〜43nとを有する

(もっと読む)

クロックおよび電源グリッドスタンダードセルを用いたASICデザイン

【解決手段】 ASICソフトウエアデザインツールを用いて配列および配線することができる集積または統合された電源およびクロックグリッド。集積されたグリッドは、電源レールとクロックラインを含む、3つのタイプのグリッドユニットを含む。電源レールおよびクロックラインは、種々のグリッドユニットセルにおいて種々の配向を含む。 (もっと読む)

メモリ回路

【課題】電源投入時または回路動作中に電源ラインやグランドラインに伝播するノイズによって、記憶回路が誤動作してしまっていた。この記憶回路をメモリ装置の書き込みと消去との制御信号のラッチ回路として使用した場合、メモリ装置の内容が意図せずに書き換えられてしまうことがあった。

【解決手段】本発明のメモリ回路を構成する記憶回路は、第1のラッチ回路5とこれの反転データを入力する第2のラッチ回路6と、第1のラッチ回路5と第2のラッチ回路6の反転出力信号とを入力するアンド回路13とを有している。通常時は、第1,第2のラッチ回路同士は、保持するデータが互いに反転しているため、アンド回路13の出力に変化はないが、ノイズなどにより第1,第2のラッチ回路が保持するデータが互いに同じになると、アンド回路13からはデータが出力されない。したがって、メモリ回路の電源投入時、動作時を問わず誤動作を防止することができる。

(もっと読む)

デグリッチ回路

【課題】 低消費電力でノイズを除去することができるデグリッチ回路を提供する。

【解決手段】 第1電流源ICH1を介して電源ラインに接続され、第2電流源ICH2を介して接地されるインバータ21に電圧VINが入力される。インバータ21には、キャパシタC1を介して接地され、トランジスタ23,24に接続される。これらのゲート端子には、電源電圧VCCよりも低い第2制御電圧VP、接地レベルよりも高い第1制御電圧VNがそれぞれ入力される。トランジスタ24は、第4電流源ICH4を介して接地ラインに接続され、電圧VAはインバータ26を介してラッチ回路30の第1の入力端子INAに供給される。トランジスタ23は、第3電流源ICH3を介して電源ラインに接続され、電圧VBはインバータ25を介してラッチ回路30の第2の入力端子INBに供給される。

(もっと読む)

半導体集積回路

【課題】電源ノイズ発生の主要因のひとつである、内部ロジックでのゲートの出力変化による電源電流変動を低減すること。

【解決手段】ゲート回路105−1の出力変化を受けてゲート回路106−1、2の出力が変化するとき、ゲート回路106−1とゲート回路106−2ではスレッショルド電圧が異なるため、出力変化が発生するタイミングが異り、また、ゲート回路106−1、2の出力変化を受けてゲート回路107−1〜4の出力が変化するとき、ゲート回路107−1、3とゲート回路107−2、4ではスレッショルド電圧が異なるため、出力変化が発生するタイミングが異なることにより、電源電流の変化は分散し、各電源ラインに発生する電源電流のピークが低減され、電源ノイズを抑制することができる。

(もっと読む)

ノイズ低減回路

【課題】 クロストークノイズを安定して減少させることができ、クロストークノイズに起因する回路誤動作を確実に防止できるノイズ低減回路を提供する。

【解決手段】 電源側に並列に接続された第一及び第二のトランジスタと、前記第二のトランジスタの出力側に直列接続された抵抗手段とを設け、前記抵抗手段の出力側と前記第一のトランジスタの出力側とを出力ノードで接続し、前記出力ノードから出力される出力電圧の変化が段階的になるように前記第一及び第二のトランジスタのオン/オフ動作タイミングを制御する制御回路を備えた。

(もっと読む)

1 - 20 / 20

[ Back to top ]