Fターム[5J043AA00]の内容

パルス発生器 (3,485) | 目的、効果 (1,186)

Fターム[5J043AA00]の下位に属するFターム

温度変動補償 (60)

電源変動補償 (55)

低消費電力化 (154)

高速化、高周波化、スイッチングの高速化 (108)

集積化、小型化 (89)

ノイズ対策(チャタリング、α線を含む) (86)

クロックに伴う誤動作の防止 (17)

故障対策、故障検知、現用予備 (15)

回路試験、評価、検査 (36)

同期 (13)

起動、停止(単安定マルチのトリガを除く) (21)

素子、部品のばらつき補償 (47)

素子特性の限定、調整 (5)

差動増幅器、比較器のオフセット除去、補正 (1)

出力の調整、可変、切換 (183)

出力の安定化 (234)

Fターム[5J043AA00]に分類される特許

41 - 60 / 62

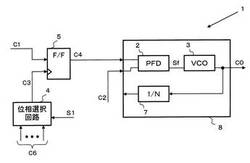

位相調整回路装置及びタイミング調整回路システム

【課題】 所定の入力信号または出力信号について製造バラツキや電源電圧や温度変化の影響を少なくし、適切なタイミングでの動作を実現する位相調整回路装置を提供する。

【解決手段】 2つの入力クロック信号の位相差に応じた電圧の位相差検出信号を出力する位相比較回路2と位相差検出信号Sfの電圧値に応じた周波数で発振する基準クロック信号C0を出力する電圧制御発振回路3を有する位相同期回路8、位相の異なる複数のクロック信号C6の1つを選択して位相調整用の参照クロック信号C3として出力する位相選択回路4、及び、第1入力クロック信号C1の信号レベルの変化タイミングを参照クロック信号C3の立ち上がりまたは立ち下がりタイミングに合わせる位相調整を行うフリップフロップ回路5を備え、位相調整後の第1入力クロック信号C4と基準クロック信号C0が外部回路を経由して得られる遅延クロック信号C2を位相比較回路2に入力する。

(もっと読む)

フリップフロップを用いたパワーオンリセット回路、及びこれを備えた半導体装置

【課題】 半導体装置において、パワーオン時にパワーオンリセット信号によるリセット状態への初期設定がうまくいかず、ラッチ信号が期待値と異なり別のモードに設定され誤動作するという問題がある。

【解決手段】 本発明のパワーオンリセット回路は、セット用フリップフロップの他にダミーフリップフロップを備えている。パワーオン時にパワーオンリセット信号によるリセットが行われない場合にも、ダミーフリップフロップからの出力によりリセットし、初期設定する。ダミーフリップフロップを設けることで、より確実なパワーオン時の初期設定が可能となるパワーオンリセット回路、及び半導体装置が得られる。

(もっと読む)

半導体集積回路装置の設計方法

【課題】ゲートセルサイズの増加を抑えながら遅延時間を変えることなく、信号の遅延時間のばらつきを大幅に低減する。

【解決手段】出力回路などに設けられるゲートセルの1つであるフリップフロップ2において、信号遅延時間のばらつきに最も起因する該フリップフロップ2の入出力部となるインバータ6,9,12を構成するMOSトランジスタのゲート長とゲート幅のサイズのみを、標準ゲートセルのトランジスタよりも大きくすることにより、ディレイ特性を変えることなく遅延時間のばらつきを大幅に低減する。

(もっと読む)

デュアルパスマルチモード順次記憶素子

本明細書では、デュアルパスマルチモード順次記憶素子(SSE)(10)が説明されている。一実施例では、デュアルパスマルチモードSSEは、第1(14)および第2(12)の順次記憶素子、データ入力、データ出力ならびに選択機構(16)を備えている。第1および第2の順次記憶素子(14、12)は、それぞれ、入力および出力を有する。データ入力は両方の順次記憶素子の入力に結合され、データを受け入れるように構成される。データ出力は両方の順次記憶素子の出力に結合され、データを出力するように構成される。選択機構(16)は、データ入力からのデータをデータ出力に渡すために、順次記憶素子のうちの1つを選択するように構成される。一実施例では、第1の順次記憶素子はパルストリガー式記憶素子(14)を備えており、第2の順次記憶素子はマスタースレーブ記憶素子(12)を備えている。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】SOI型のMOSトランジスタを用いたデータ保持型フリップフロップに対するボディーバイアス制御をその動作状態に応じて最適化する。

【解決手段】SOI型のMOSトランジスタから成る複数個の回路は、電源スイッチ(10)による選択的な電源遮断の対象にされるマスタラッチ部(MLAT)と選択的な電源遮断の非対象にされるスレーブラッチ部(SLATdr)とから成るフリップフロップを有する。スレーブラッチ部は電源非遮断状態においてMOSトランジスタの閾値電圧が小さくなるようにボディーバイアス制御され、電源遮断状態においてMOSトランジスタの閾値電圧が大きくなるようにボディーバイアス制御される。これにより、電源非遮断状態においてフリップフロップの高速化が保障され、マスタラッチ部の動作電源遮断状態においてスレーブラッチ部におけるサブスレッショルドリーク電流が低減される。

(もっと読む)

温度センサ及び温度検出方法

【課題】リングオシレータで具現された温度センサ及びそれを利用した温度検出方法を提供する。

【解決手段】温度変化によってその内部電流量が可変し、第1及び第2バイアス信号を発生する第1バイアス部と、温度変化に関係なくその内部電流量が一定であり、第3及び第4バイアス信号を発生する第2バイアス部と、第1及び第2バイアス信号に応答して第1クロック信号を発生する第1リングオシレータと、第3及び第4バイアス信号に応答して第2クロック信号を発生する第2リングオシレータと、第1クロック信号の一つのパルスをラッチしてワンショットパルスを発生するワンショットパルス発生部と、ワンショットパルス幅を第2クロック信号のパルスとしてカウントして温度コードを発生するカウンタと、を備える温度センサである。

(もっと読む)

フリップフロップ、集積回路、及びフリップフロップのリセット方法

【課題】 リセット配線を無くすことで、LSI内の配線の複雑化を防止でき、又は信号配線に利用できるチャネルを増やすことができるフリップフロップ、それを用いた集積回路、及びフリップフロップのリセット方法を提供する。

【解決手段】 電源電圧の変動を検出してリセットを行うフリップフロップにおいて、ハイ又はローレベルを記憶する状態保持ノード2と、所定値を越える電源電圧の変動を検出することで、状態保持ノード2の記憶状態をリセットするリセット信号を形成するリセット信号形成回路1とを備える。

(もっと読む)

フリップフロップ機能素子、半導体集積回路、半導体集積回路設計方法及び半導体集積回路設計装置

【課題】回路規模の増大を抑制しつつタイミング違反を防止することが可能なフリップフロップ機能素子、半導体集積回路、半導体集積回路設計方法及び半導体集積回路設計装置を提供する。

【解決手段】設計装置のセルライブラリに、3個のラッチ回路(L1、L2、L3)を備えるフリップフロップFF1をスタンダードセルとして記憶する。このラッチ回路L2の出力は、フリップフロップFF1の出力信号Qとなる。ラッチ回路L2にデータ信号は、クロック信号CKによりラッチされた信号をラッチ回路L3に供給する。このラッチ回路L3の出力は、フリップフロップFF1の出力信号Q2となる。ホールドタイム違反が生じる可能性があるエラーパスを発見した場合、設計処理部は、このエラーパスにおいて前段のフリップフロップFFの出力としてQ出力からQ2出力に変更する。

(もっと読む)

タイマ制御装置

【課題】タイマー時間のバラツキを予め把握し電圧値に比例した補正量が設定できる補正手段で補正することで、マイコンに発振子を備えることなく高精度なタイマーを提供する。

【解決手段】動作クロック発振用の発振素子を備えないマイコン1と、制御動作開始を指示する入力手段8と、制御対象の動作を入/切する出力手段11と、補正手段5とを備え、前記マイコン1は、所定の時間のみ前記制御対象を動作させるタイマ機能を備え、前記補正手段5はアナログ電圧を前記マイコン1へ出力することで、前記タイマ機能の動作時間を電圧に応じて補正することができるので、発振子を備えずに簡単な構成で高精度なタイマーを提供することが出来る。

(もっと読む)

半導体回路

【課題】 より低い電圧から広範囲の電源電圧範囲で安定に動作することができる、タイマー回路又は発振回路である半導体回路を提供する。

【解決手段】 電源電圧Vccで駆動され、電源電圧Vccに依存した電流を出力するとともに、電源電圧Vccから所定の低下電圧だけ低下してなる基準電圧Vrefを出力する電流源12を用いてコンデンサ11を充電する。コンパレータ14は、コンデンサ11の電圧を電流源12から出力される基準電圧Vrefと比較して、基準電圧Vref以上となったとき出力信号を出力する。タイマー回路40は、電源電圧Vccの供給開始から、コンデンサ11の電圧がその充電により経過時間に実質的に比例して上昇し基準電圧Vrefに到達するまでの遅延時間後に、出力信号を出力する。

(もっと読む)

遅延回路及び発振回路

【課題】 本発明の課題は、電流源の設定電流が小さい場合でも高精度な遅延時間を得ることができる遅延回路及び発振回路を提供することである。

【解決手段】 電流値が設定可能な電流源(I1)と、電流源によって充電されるコンデンサ(C1)と、コンデンサに蓄積されたの電荷を放電するスイッチング素子(M1〜M10)と、コンデンサの充電電圧と基準電圧とを比較するコンパレータ(CMP1)とを備え、スイッチング素子がオフしてコンデンサの充電を開始し、コンデンサの電圧が基準電圧に達するまでの時間を遅延時間として出力する遅延回路において、電流源の設定電流値が小さい場合は、スイッチング素子のリーク電流を少なくしている。

(もっと読む)

遅延同期ループ及びこれを具備した半導体メモリー装置

【課題】 互いに異なる位相を有した複数個のクロック信号を発生することができる遅延同期ループを提供する。

【解決手段】 クロック信号とフィードバッククロック信号との位相差を検出し、前記位相差によって変化する複数ビットの遅延制御信号を発生する位相検出器12と、前記複数ビットの遅延制御信号に応答して前記クロック信号を遅延させて複数個の出力クロック信号及び前記フィードバッククロック信号を発生する所定個数の縦続接続された第1の遅延セルを具備する第1の遅延器18と、前記複数個の遅延制御信号に応答して反転クロック信号を遅延させて複数個の反転出力クロック信号を発生する所定個数の縦続接続された第2の遅延セルを具備する第2の遅延器22と、前記複数個の出力クロック信号及び前記複数個の反転出力クロック信号の中で関連があるクロック信号を位相混合して補正された複数個の出力クロック信号を発生する位相混合器24とを含む。

(もっと読む)

乱数発生器および乱数を発生する方法

【課題】決定論的事後処理を必要としない乱数発生器および乱数発生方法を提供する。

【解決手段】不均等または均等周期の発振ディジタル出力信号A1、A2、...、ALが、少なくとも2つのリング発振器32、33、34によって発生され、論理状態「0」、「1」を表す外部パリティ信号PSが、奇数個の出力信号A1、A2、...、ALが特定の論理状態「1」を取るときに発生される乱数発生方法に関する。外部パリティ信号PSは、それぞれのリング発振器の外部パリティ入力36、37、38へフィードバックされる。本発明において、カオス理論(パリティ信号のフィードバック)とディジタル回路における真のランダム性(熱雑音に起因するジッタ)との協力が、乱数を発生する新規な理論的原理として、効率的な実際的解決法を導いた。

(もっと読む)

発振信号生成器及びその装置

【課題】

発振信号が歪んでしまうのを確実に回避することができるようにする。

【解決手段】

発振信号生成部P1の各遅延回路21においては、第1制御信号Sc1に応じた所定量の電流を供給する第1電流供給部P4を、電源電圧と差動対部P3との間に設けるようにしたことにより、この差動対部P3と第1及び第2伝送線L1、L2と可変抵抗部P6とを電源電圧からフローティングしたような状態にすることができる。この結果このフローティングしたような状態となっている部分に接続される電圧を調節することにより、発振信号Soの発振中心電圧を、遅延回路21の動作が線形領域から外れないように制御することができる。

(もっと読む)

半導体装置、発光表示装置およびそれらの駆動方法

シフトレジスタ回路の各段の出力端にラッチ回路を設け、出力を出したい段にパルスがシフトした段階でラッチパルスを入力し、次にラッチパルスが入力されるまでこの状態を保持し、次に出力を出したい段にパルスがシフトした段階で、ラッチパルスを入力すると、出力段を切り替えることができる。このようにすることで、クロック周波数を変えずラッチパルスを変化させるだけで選択する期間や選択する段を任意に選択することができる。  (もっと読む)

(もっと読む)

発振装置

【課題】細かな時間分解能で発振信号の位相制御を行うことが可能で、且つ回路規模が小さく低消費電力な発振装置を提供する。

【解決手段】発振装置10は、行方向および列方向に7個ずつマトリクス状に配列されたインバータから構成され、列方向に配列されたインバータR11〜R77はリング状に連結されて7個の7段リングオシレータOC1〜OC7が構成され、各リングオシレータOC1〜OC7の各段のインバータ間のノードは行方向に配列されたインバータによって接続され、行方向に配列されたインバータF11〜F77はリング状に連結されることにより、各リングオシレータOC1〜OC7は多重化されている。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に搭載されるラッチ回路のソフトエラーレートを低減でき、救済情報等をラッチした場合にハードエラーと認識されるエラーの救済を可能とする。

【解決手段】不良アドレス等の情報を記憶した複数のフューズ素子10と、この複数のフューズ素子から並列に転送される複数の情報をラッチする複数の第1のラッチ回路11と、この複数の第1のラッチ回路から並列またはシリアルに転送される複数の情報をラッチする複数の第2のラッチ回路12と、これらの各ラッチ回路に入力する情報の転送を制御する転送制御回路13とを具備し、ラッチ回路にリフレッシュ機能を持たせている。

(もっと読む)

半導体集積回路

【課題】データ選択機能付きのダイナミック型フリップフロップ回路において、動作の高速性を良好に確保しながら、複数のデータの何れもが選択されていない場合であっても、正常動作するようにする。

【解決手段】例えば選択信号S0によりHのデータD0が選択されていた場合、第1ノードN1がLとなり、第2ダイナミック回路1Bの第2ノードN2はHとなっており、出力信号QはHレベルである。この状態において、選択信号S0〜S2によって複数のデータD0〜D2の何れもが選択されなくなった際には、第1ノードN1がHとなり、前記第2ノードN2は、その電荷が放電されて、出力信号QはLレベルに誤動作する状況となる。しかし、この場合には、出力ノードN3がHとなり、第4ノードN4がLとなって、前記第2ダイナミック回路1Bのn型トランジスタTr6がオフして、第2ノードN2の放電を阻止する。

(もっと読む)

フリップフロップ回路及び半導体装置

【課題】組合せ回路の電源切断直前におけるデータをフリップフロップ回路に保持するための外部制御信号のタイミング設定を容易にする。

【解決手段】マスターラッチと該マスターラッチに直列に接続されたスレーブラッチに互いに逆位相のマスタークロック信号とスレーブクロック信号を供給し、これにより該マスターラッチに入力されたデータを該スレーブラッチへシフトさせるようにしたフリップフロップ回路において、外部制御信号の入力により該マスタークロック信号と該スレーブクロック信号の信号レベルを同一値に固定する手段を設ける。

(もっと読む)

位相単独の予想可能な再設定の方法と装置

脳のオリーブ小脳ネットワークで発見される下オリーブ(IO)神経の振動力学が再現され、様々な制御アプリケーションに適用される。特徴のある振幅と周波数で準正弦波振動を生成するIO神経モデルが提供される。活動電位は振動のピークで発生し、正確なタイミング特性を有する。IO神経モデルに印加される刺激は、振動振幅と周波数の変化を示さず、振動位相のシフトを生じる、それゆえ活動電位の時間シフトを生じる。その結果として生じる位相は刺激の強さにより定義され、刺激がいつ印加されるかに依存せず、このように、自己参照位相再設定(SPR)の効果を提供する。結合された複数のIO神経、またはそのモデルは、振動位相クラスタの形態で空間と時間に組織される傾向がある。IO発振器の位相は、位相進化の過程にかかわりなく、所望の位相パターンに素早くセットされうる。IO神経モデルを実装する回路と、その回路に基づく制御システムが記載される。 (もっと読む)

41 - 60 / 62

[ Back to top ]