Fターム[5J055AX08]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153) | スイッチの基本性能向上 (933) | 駆動能力の制御 (142)

Fターム[5J055AX08]の下位に属するFターム

出力部スイッチの数、構成を変えるもの (9)

スルーレートを制御できるもの (75)

Fターム[5J055AX08]に分類される特許

1 - 20 / 58

発振回路、およびDC−DCコンバータ

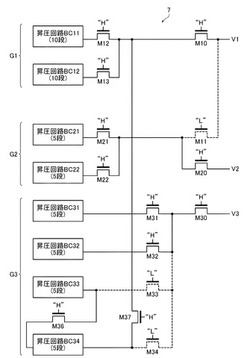

電圧生成回路

【課題】回路面積を低減させることのできる電圧生成回路を提供する。

【解決手段】一の実施の形態に係る電圧生成回路は、第1の電圧値の第1電圧を発生させる第1の昇圧回路と、第2の電圧値の第2電圧を発生させる複数の第2の昇圧回路を含む第2昇圧回路群とを有する。複数の第2の昇圧回路は、第1の状態から第2の状態に移行する際に互いに直列に接続され第1昇圧回路とともに第1電圧を発生可能に構成されている。

(もっと読む)

電磁機器駆動装置および電磁機器の駆動方法

【課題】電磁機器の累積使用量が多くなっても少ないと同じ一定時間で電磁機器を動作状態から停止状態に移行させる。

【解決手段】電磁機器駆動装置は、励磁用電源から電磁コイルへの通電が停止したときに逆起電力によって電磁コイルの両端間に生じる電圧をクランプするフリーホイール回路と、フリーホイール回路によってクランプされた電圧が、電磁機器の累積使用量が少ないときよりも多いときの方が高くなるように、フリーホイール回路の動作を制御するコントローラーと、を備える。

(もっと読む)

駆動回路

【課題】駆動電圧を調整可能な駆動回路を提供すること。

【解決手段】駆動回路10は、チャージポンプ回路部14を備えている。チャージポンプ回路部14は、メインスイッチング素子SW10がターンオンする遷移期間の初期段階において、キャパシタC1に充電された充電電圧に基づいて駆動電源18の電圧Vsを昇圧して駆動電圧Vgprを生成する。チャージポンプ回路部14では、指示信号S1に基づいてキャパシタC1に充電される充電電圧が調整可能に構成されている。

(もっと読む)

半導体装置

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

半導体装置

【課題】ハイサイド駆動回路が負バイアス駆動を行いつつ、ブートストラップコンデンサによりハイサイド駆動回路に駆動電圧を供給することができる半導体装置を得る。

【解決手段】基準電圧回路3は、ハイサイド駆動回路1の高圧端子VBの電圧と低圧端子VEの電圧との間の基準電圧を生成して、ハイサイドスイッチング素子Q1とローサイドスイッチング素子Q2の接続点に供給する。充電用スイッチング素子Q3のドレインがハイサイド駆動回路1の低圧端子VEに接続され、ソースが接地されている。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

半導体素子駆動装置及び方法

【課題】並列に駆動される複数の半導体素子の特性差によって生じる、ターンオンやターンオフ時のスイッチングにおける電流の偏りを緩和すること。

【解決手段】電圧変換器14は、IGBT13−1乃至13−3の各々のエミッタセンス電流を電圧信号に変換する。平均値演算器17や誤差演算器18等の演算器は、LPF15から出力される、IGBT13−1乃至13−3の各々に対応する電圧信号の平均値を求め、それぞれの電圧信号についての平均値に対する誤差を演算する。PWM波形生成部11は、IGBT13−1乃至13−3の各々を駆動するための駆動信号(パルス信号)を出力する。差動増幅器12の各々の駆動信号を、当該IGBT13−1乃至13−3の各々に対応する誤差に基づいて調整して、当該IGBT13−1乃至13−3の各々に供給する。

(もっと読む)

スイッチング回路およびスイッチング回路を用いた撮像装置

【課題】EM−CCDのCMG駆動回路からEM−CCDの出力信号への飛び込みを低減しながら、負荷容量CMG電圧の振幅の減衰を防ぎ、矩形波特性を改善する。

【解決手段】論理バッファとPchMOSとNchMOSのゲート間にフェライトビーズとダイオードの並列接続を挿入し、MOSがターンオフする方向にダイオードが接続されているスイッチング回路において、PchMOSのドレインソース間導通抵抗が2オーム以上あり、PchMOSのドレインとNchMOSのドレインとが1オーム以上の抵抗で接続され、PchMOSのドレインと容量負荷間に、スイッチング基本波周波数におけるインピーダンスがスイッチング基本波周波数における前記容量性負荷のインピーダンスの1/2より低いインピーダンスのフェライトビーズを直列接続する。

(もっと読む)

出力回路、システム、及び出力回路の制御方法

【課題】信号波形の変異を抑制すること。

【解決手段】第1のトランジスタT1は、信号S3に応答してオンオフし、オンしたトランジスタT1は外部端子P2に接続された伝送路27をプルダウンする。伝送路27のレベルは、トランジスタT1のゲートと外部端子P2とをACカップリングするキャパシタC1により、キャパシタC1の容量値に応じた傾きで立ち下がる。プルダウン回路44は、外部端子P2の電位に応じて、トランジスタT1のゲート電圧をプルダウンする。

(もっと読む)

電子リレー

【課題】制御部及びゲート駆動部によって消費される電力を抑制しつつ、負荷の起動時に突入電流を流しきることが可能な電子リレーを提供する。

【解決手段】商用電源6と負荷7に直列接続され、トランジスタ構造を有するスイッチ素子を用いた開閉部11と、負荷の起動及び停止を制御する制御部12と、制御部12とは絶縁され、スイッチ素子のゲート電極にゲート駆動信号を出力するゲート駆動部13と、制御部12及びゲート駆動部13を動作させるための電力を確保する電源部14を備え、制御部12は、負荷7の起動時に、ゲート駆動部13に、所定時間だけスイッチ素子のゲート電極に対して、定常安定動作時よりも多くの駆動電力を供給させる。

(もっと読む)

集積回路装置、電子機器及び集積回路装置の製造方法

【課題】 出力端子から出力される電圧値に応じて複数種の中から選択される耐圧に設定される集積回路装置等の提供すること。

【解決手段】 第1の耐圧を有する第1の出力トランジスター構造Tr_M1,Tr_M2と、第1の耐圧よりも高い第2の耐圧を有する第2の出力トランジスター構造Tr_H1,Tr_H2とが形成された半導体基板に、マスクを変えて配線して所定の耐圧に設定される集積回路装置である。配線により第1の耐圧が選択されると、第1,第2の出力トランジスター構造の双方が出力端子OUTと接続され、第2の出力トランジスター構造は、ダイオード接続されて静電気保護素子D1,D2を形成する。配線により第2の耐圧が選択されると、第1の出力トランジスター構造は出力端子OUTに非接続とされ、第2の出力トランジスター構造が出力端子OUTと接続される第2耐圧出力段トランジスターを形成する。

(もっと読む)

負荷駆動装置

【課題】負荷を駆動するための定電流のばらつきを低減することができる負荷駆動装置を提供する。

【解決手段】シャント抵抗20の一端側をオペアンプ34の反転入力端子に接続し、シャント抵抗20の他端側を基準電源32を介してオペアンプ34の非反転入力端子に接続する。シャント抵抗20に流れる電流は、駆動回路30内の第1スイッチング素子35を介して負荷10であるIGBTのゲートに流れるようになっている。これにより、基準電源32の基準電圧の値をVrefとし、シャント抵抗20の抵抗値をRoutとし、負荷10に流れる定電流の値をIcとすると、Vref=Rout×Icとなるようにオペアンプ34が第1スイッチング素子35のゲートをフィードバック制御する。これにより、シャント抵抗20に流れる電流の大きさが一定に制御され、ひいては負荷10に流す定電流のばらつきが低減される。

(もっと読む)

正負電圧論理出力回路及びこれを用いた高周波スイッチ回路

【課題】負電圧の変化に対して正常な論理回路動作を確保できる範囲である動作ウィンドウの幅の拡張を可能とする。

【解決手段】負電圧レベルシフト回路4aは、第3のレベルシフタ13aと、第4のレベルシフタ14aとを具備すると共に、レベルシフト基準電圧回路3からの切替信号に応じて第4のレベルシフタ14aを短絡、開放するレベルシフト切替スイッチ8aとを具備してなり、負電圧VSSの大きさに応じて、レベルシフト切替スイッチ8aのオン、オフを選択することで、負電圧VSSの変動に対して正常な回路動作を確保できる範囲である動作ウィンドの拡張が可能に構成されたものとなっている。

(もっと読む)

負荷駆動装置

【課題】複数の負荷の駆動状態に応じて、スイッチング損失の低減とノイズの抑制とを図ることができる負荷駆動装置を提供する。

【解決手段】複数の負荷2A〜2Dについて個別に設けられ、半導体スイッチング素子5,6により前記負荷をスイッチング駆動する複数の負荷駆動手段3A〜3Dで、台形波傾き制御プリドライバ7が、NチャネルMOSFET5,6のゲートに対してそれぞれ台形波状のパルス信号を出力する場合に、台形波の立上り及び立下りの傾きを変更可能に構成し、4チャネル駆動の場合は傾きを大きく、1チャネル駆動の場合は台形波の傾きを小さくする。

(もっと読む)

クロック生成装置、クロック切り替え方法及びプログラム

【課題】クロック生成装置に接続されるスレーブ装置の数が変化し、接続先の負荷容量が変動したとしても、クロック生成装置とスレーブ装置間で定められた切り替え仕様を満たすクロック選択信号を出力する。

【解決手段】クロック生成装置は、スレーブ装置実装検出部において接続されたスレーブ装置の数を検出し、その検出数をバッファタイプ選択部に通知する。バッファタイプ選択部においては、この通知に基づきクロック選択信号を出力する際のバッファタイプを選択する。

(もっと読む)

スイッチングレギュレータ

【課題】 小型・低雑音のスイッチングレギュレータを提供する。

【解決手段】 導通、遮断の2状態が交互に切り替わる複数のトランジスタで構成されたスイッチングレギュレータの出力段と、その出力段トランジスタを各々個別に駆動するための駆動回路から構成され、当該駆動回路は、各々出力段トランジスタにおける遮断から導通状態への遷移時間が、導通から遮断状態への遷移時間に比べて長くなるように立ち上がり、立ち下がり時の駆動能力をアンバランスに設定され、各々の遷移時間は、出力信号の電位があらかじめ設定された電位に達したことを判定して変化させることを特徴とするスイッチングレギュレータとして構成される。

(もっと読む)

負荷駆動制御装置

【課題】消費電力を抑えつつ、高輝度で安定した駆動を得るとともに駆動制御回路全体の寿命を向上させる。

【解決手段】負荷20に接続される駆動制御部10を備え、駆動制御部10は、負荷20の定格電流値IFと、パルス駆動したときの絶対最大定格電流値Imaxから予め設定されたピーク電流値Ipに基づいてパルス幅変調することで、負荷20のオン期間を規定した第1のオン/オフ周期による第1駆動パルスP1を生成し、第1のオン/オフ周期のオン期間の中でさらにスイッチングさせることで、パルスの最大振幅がIpとなるように、第2のオン/オフ周期による第2駆動パルスP2を生成する定電流パルス駆動部14とを備え、第2駆動パルスP2によって駆動された電流を前記負荷20に印加することによって、負荷20を連続的に駆動させるとともに、充放電制御部15のキャパシタンスC1を信頼性寿命の高いセラミックコンデンサーを使用した。

(もっと読む)

半導体集積回路装置

【課題】超音波診断システム等に用いられる送信ドライバにて、出力トランジスタの製造ばらつきに依存せず、一定の出力波形の傾きを得る半導体集積回路装置を提供する。

【解決手段】出力トランジスタのゲート幅を縮小し模造したレプリカを同一基板上に作成しかつ近接して配置することで両者が同じ製造ばらつきを持つ特徴を利用し、レプリカのオン抵抗が理想値と同じになるゲートソース電圧を、出力トランジスタのゲートソース間に与える電位差にする。

(もっと読む)

駆動装置、及び表示装置

【課題】並列接続された複数の出力アンプ回路において所望の駆動能力を実現することができる駆動装置、及び表示装置を提供すること。

【解決手段】本発明に係る駆動装置(ソースドライバ1)は、並列接続された複数の出力アンプ回路10と、複数の出力アンプ回路10に、バイアス電圧供給源25からバイアス電圧を供給するバイアス配線(幹バイアス配線22)と、複数の出力アンプ回路10に、電源電圧供給源35から電源電圧を供給する電源配線31と、複数の出力アンプ回路10に供給される電源電圧とバイアス電圧との差が所望となるように、バイアス電圧にオフセット電圧を重畳する補正手段(バッファ26)とを備えた。

(もっと読む)

1 - 20 / 58

[ Back to top ]