Fターム[5J055DX72]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 慣用的な複合スイッチ (1,758) | 直列 (1,001)

Fターム[5J055DX72]に分類される特許

101 - 120 / 1,001

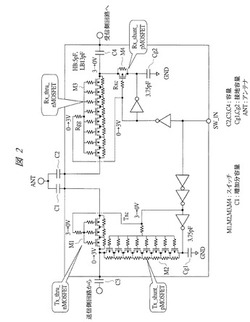

スイッチ回路、半導体装置及び携帯無線機

【課題】負バイアス発生回路を用いずにマージン電圧を改善することができる手段をスイッチ回路に提供する。

【解決手段】N型MOSFETを用いて構成されるスイッチM1を、信号をアンテナに同通するスイッチに、P型MOSFETを用いて構成されるスイッチM2を、信号を接地するシャント用にそれぞれ用いる。各スイッチを構成するMOSFETのゲート端子に共通の制御信号を入力する。この制御信号の反転信号をスイッチM2の接地端に接続することで、各MOSFETのゲート端子の電位を接地電圧に設定できる。

(もっと読む)

半導体装置および携帯電話機

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】RXスルートランジスタ群TH(RX)は、互いに直列に接続されたMISFETQ1〜Q5において、それぞれのMISFETのボディ領域と、隣接するMISFETのソース領域あるいはドレイン領域とを、それぞれ、ダイオード(整流素子)を介して接続する。そして、特に、nチャネル型MISFETの場合、MISFETのボディ領域から隣接するMISFETのソース領域あるいはドレイン領域へ向う向きが順方向となるようにダイオードを接続する。

(もっと読む)

半導体集積回路

【課題】 内部回路の内部ノードが初期状態に設定されたことを精度よく検出し、内部回路が動作を開始するまでの復帰時間を短縮する。

【解決手段】 第1電源スイッチは、内部電源電圧を受けて動作する内部回路の動作を開始させるための第1電源オン信号の活性化中に、外部電源線を内部電源電圧が供給される内部電源線に接続する。第2電源スイッチは、第2電源オン信号の活性化中に、外部電源線を内部電源線に接続する。検知部は、第1電源スイッチのオンにより上昇する内部電源電圧を受けて動作する回路を含む。検知部は、内部電源電圧が第1電圧を超えることにより、内部回路の内部ノードが初期状態に設定されたことを検出したときに第2電源オン信号を活性化する。

(もっと読む)

プリドライバ回路、および、駆動回路

【課題】回生電流がモータ等の負荷から駆動回路を構成するプリドライバ回路側に流れても、駆動回路の制御に影響を与えないようにすること。

【解決手段】第1の電源電圧(VM)に接続された第1の駆動トランジスタと、接地に接続された第2の駆動トランジスタとの間の負荷に接続される接続ノード(N1)を出力端子とするブリッジ回路に接続されたプリドライバ回路において、接続ノード(N1)である出力端子に接続された出力モニタ回路を有し、該出力モニタ回路を用いて、出力端子に現れる電圧(Vout)に基づいて電圧のみをフィードバックさせる第1のフィードバック信号(S1)を生成し、第1のフィードバック信号(S1)に基づいて第2のフィードバック信号(S2)を生成して、出力端子に現れる電圧(Vout)が第1の電源電圧(VM)に近づくように、第1の駆動トランジスタを駆動制御する。

(もっと読む)

誘導性負荷駆動装置

【課題】電源回路における回路素子の破壊を防止することが可能な誘導性負荷駆動装置を提供する。

【解決手段】誘導性負荷駆動装置の構成として、電源回路の出力端子と誘導性負荷の一端との間に介挿された第1のスイッチング素子と、前記誘導性負荷の他端とアースとの間に介挿された第2のスイッチング素子と、前記第1及び第2のスイッチング素子の両方がオフの時に前記誘導性負荷の他端から出力される逆起電流を前記電源回路の出力端子に回生させる逆起電流回生回路と、前記電源回路の出力電圧が予め設定された閾値以上となった場合に、前記第2のスイッチング素子をオンにする回路素子保護回路と、を備えた構成を採用する。

(もっと読む)

電源ユニット及び制御装置

【課題】電源ユニットの出力ラインにおける地絡などの故障に対し、電源の保護及び故障の検知を行う。

【解決手段】サブ電源供給ラインLSに、サブ電源101側をソースとして第1MOSFET102を直列に接続し、第1MOSFET102のドレインにドレインを接続させて第2MOSFET103を直列に接続する。制御ユニット200内のサブ電源供給ラインLSにも、サブ電源101側をソースとして第3MOSFET202を直列に接続し、第3MOSFET202のドレインにドレインを接続させて第4MOSFET203を直列に接続し、第1〜第4MOSFETを制御することで、サブ電源101の電力を負荷201に対して供給する。各MOSFETのドレイン電圧、及び、第2MOSFET103と第3MOSFET202との間の電圧をモニタし、MOSFETの故障及びサブ電源供給ラインLSの故障を診断する。

(もっと読む)

半導体装置

【課題】小型化と高いアイソレーションを実現可能な半導体装置を提供する。

【解決手段】装置本体2は、半導体素子搭載部3と、第1の導電体4及び第2の導電体5を有する。第1の導電体4及び第2の導電体5は、半導体素子搭載部3の周囲に互いに近接して設けられている。半導体素子は、半導体素子搭載部に配設される。半導体素子は、第1のスルースイッチFET1と、第1のシャントスイッチFET1と、第2のスルースイッチFET2と、第2のシャントスイッチFET2と、を有する。第1のスルースイッチFET1は、共通端子ANTと第1の高周波端子RF1との間に接続される。第1のシャントスイッチFET1は、第1の高周波端子RF1に接続される。第2のスルースイッチFET2は、共通端子ANTと第2の高周波端子RF2との間に接続される。第2のシャントスイッチFET2は、一端が第2の高周波端子RF2に接続される。

(もっと読む)

高周波モジュール

【課題】信頼性が高い省電力モードを実現可能な高周波モジュールを提供する。

【解決手段】例えば、送信ノードTXをアンテナANTに接続するスイッチ用トランジスタTSW2と、TXを接地電源電圧GNDに短絡するスイッチ用トランジスタTSW1と、TSW1,TSW2のオン・オフを正の電源電圧VSWと負の電源電圧(−VSS)で制御するレベルシフト回路LSを備える。LSは、TSW2をオン、TSW1をオフに制御する送信動作モードTXMDの状態でスリープ命令を受けた際に、一旦、TSW2をオフ、TSW1をオンに制御するアイソレーション動作モードISOMDに移行し、一定の期間(Twait)が経過したのち、VSW,−VSSが非活性状態となるスリープモードSLPMDに遷移する。

(もっと読む)

電気回路、充電制御装置、充電システム、および制御方法

【課題】より簡易的な構成で半導体スイッチを駆動する回路を実現する。

【解決手段】充放電切替回路11は、プラス側の電力線に挿入される半導体スイッチ12−1および12−2と、入力側の端子に入力される入力電圧を、所定の出力電圧に変換して出力側の端子から出力する絶縁型DCDCコンバータ23−1および23−2とを備える。そして、絶縁型DCDCコンバータ23−1および23−2の出力側のマイナス端子がプラス側の電力線に接続され、絶縁型DCDCコンバータ23−1および23−2の出力側のプラス端子が半導体スイッチ12−1および12−2の開閉を制御する端子に接続される。本発明は、例えば、高電圧の電源の充放電を制御する回路に適用できる。

(もっと読む)

高周波回路、高周波部品及び通信装置

【課題】 異なる通信システムに対応可能で、受信感度が高く送信電力の損失が抑制された高周波回路、高周波部品及びこれを用いた通信装置を提供する。

【解決手段】 第1及び第2のアンテナ端子と、第1の通信システム用の送信端子並びに第1及び第2の受信端子と、前記第1及び第2のアンテナ端子を選択して前記送信端子と接続するスイッチ回路を少なくとも備えた高周波回路であって、前記スイッチ回路と第1のアンテナ端子をつなぐ信号経路と、前記スイッチ回路と第2のアンテナ端子をつなぐ信号経路のそれぞれに整合回路を配置したことを特徴とする。

(もっと読む)

双方向スイッチおよびそれを用いたスイッチ回路

【課題】高耐圧の双方向スイッチを小型化する技術を提供する。

【解決手段】MOSFETを用いた双方向スイッチにおいて、MOSFETのソース端子とバックゲート端子間を、トランスファゲートTGを介して接続する。MOSFETのバッグゲート端子とトランスファゲートTG間の接続点と、グラウンド電位(上記MOSFETがnチャネルの場合)または電源電位(上記MOSFETがpチャネルの場合)との間にスイッチを用いてもよい。

(もっと読む)

CMOS回路及び半導体装置

【課題】しきい電圧VTが小さくてもリーク電流が小さく、また高速にかつ小さな電圧振幅で動作するCMOS回路さらには半導体装置を提供することである。

【解決手段】ゲートとソースを等しい電圧にしたときにドレインとソース間に実質的にサブスレショルド電流が流れるようなMOST(M)を含む出力段回路において、その非活性時には、前記MOST(M)のゲートとソース間を逆バイアスするように該MOST(M)のゲートに電圧を印加する。すなわち、MOST(M)がpチャンネル型の場合にはp型のソースに比べて高い電圧をゲートに印加し、また、MOST(M)がnチャンネル型の場合にはn型のソースに比べて低い電圧をゲートに印加する。活性時には、入力電圧に応じて該逆バイアス状態を保持するかあるいは順バイアス状態に制御する。

(もっと読む)

スイッチ回路

【課題】高周波信号が通る信号線と、オーディオ信号が通る複数の信号線が合流して使用される場合において、高周波信号およびオーディオ信号に発生する歪成分を抑制する。

【解決手段】高周波信号を伝送可能なケーブルの端子と、オーディオ信号を専用に伝送するケーブルの端子を共通に挿し込むことができる共通端子50からの信号線は二つに分岐して、高周波系スイッチ(USBスイッチ10)の一端と、第1階層のオーディオ系スイッチ(オーディオスイッチ20)の一端にそれぞれ接続される。高周波系スイッチの他端からの信号線は目的の回路に接続される。第1階層のオーディオ系スイッチの他端からの信号線は複数に分岐して、それぞれ第2階層のオーディオ系スイッチ(ヘッドホンスイッチ21、マイクスイッチ22)の一端に接続される。第2階層の複数のオーディオ系スイッチの他端からのそれぞれの信号線はそれぞれの目的の回路に接続される。

(もっと読む)

半導体スイッチ回路

【課題】スイッチング応答性を維持しながら、雑音が低減された出力特性をもつ半導体スイッチ回路を提供する。

【解決手段】本発明の実施形態の半導体スイッチ回路は、スイッチ部1、デコーダ部3、ドライバ部2、DC−DCコンバータ5、第1のフィルタ回路9n、第1のフィルタバイパス回路10、及び第1のバイパス制御回路11aを備える。DC−DCコンバータ5は、第1のフィルタ回路9nを介して第1の電位をドライバ部2に出力する。第1のフィルタバイパス回路10が、第1のフィルタ回路9nと並列に電気的に接続される。スイッチ部1の入出力端子Pと複数の高周波信号端子T1〜Tnのうちのいずれかの高周波信号端子との間の導通状態及び非導通状態が切り替えられたときに、第1のフィルタバイパス回路10が導通状態になるように、第1のバイパス制御回路11aが、第1のフィルタバイパス回路10に第1のモード信号Vmode1を供給する。

(もっと読む)

表示パネルドライバ及びそれを用いた表示装置

【課題】駆動電圧の極性切替(極性反転)が可能な表示パネルドライバの消費電力を低減する表示パネルドライバを提供する。

【解決手段】本発明による表示パネルドライバは、表示パネルの画素に接続された第1データ線及び第2データ線を駆動する出力段として、第1電源範囲で駆動する第1出力段24A及び第4出力段24Bを利用する第1モードと、第1電源範囲よりも広い第2電源範囲で駆動する第2出力段73A及び第3出力段73Bを利用する第2モードとを切替える第1スイッチ回路50と、第2モードの間に、正極性駆動電圧と負極性駆動電圧の出力先となるデータ線6を切替える第2スイッチ回路30とを備える。又、第1出力段24Aは、ウェルが他のNMOSトランジスタから分離され、バックゲートがソースに接続された第1プルダウン出力トランジスタMN18を備える。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力信号遅延を抑制し、消費電流の増大を抑制する出力回路の提供。

【解決手段】入力端子101と出力端子102の電圧を差動入力する差動入力段110からなる差動増幅回路と、第1及び第2の電源端子VDD、VSSに接続された第1及び第2のカレントミラー130、140と、前記第1及び第2のカレントミラーの入力間、出力間に接続される第1、第2の連絡回路150L、150Rと、第1導電型の第1のトランジスタ121と第2導電型の第2のトランジスタ122とからなる出力増幅回路と、前記第1、第2の電源端子VDD、VSSの電源電圧の間の電圧が供給される第3の電源端子VMLの電圧に応じたバイアス信号を受ける第1導電型の第3のトランジスタ161からなる制御回路160と、を備えている。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】ターンオフ用di/dt帰還部23OFFは、IGBT11Uがターンオフするときに、IGBT11Uのコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。ターンオン用di/dt帰還部23ONは、IGBT11Uがターンオンするときに、FWD12Dの転流電流IFWDに基づいて、帰還電圧VFBを生成する。この場合、ターンオン用di/dt帰還部23ONは、転流電流IFWの方向が、リバースリカバリー区間に対応する方向、即ち図13に示すFWD12Dのカソードからモータ等の負荷L側に流れる方向である場合、帰還電圧VFBを生成し、それ以外の場合、帰還電圧VFBの生成を禁止する。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】di/dt帰還部23は、IGBT11Uがターンオフするときに、IGBT11のコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。また、di/dt帰還部23は、IGBT11がターンオンするときに、図示せぬFWDの転流電流IFWDに基づいて、帰還電圧VFBを生成する。このようなdi/dt帰還部23は、帰還電圧VFBを駆動信号の電圧の一部として印加するタイミングを遅延させる遅延フィルタとして、LPF回路201を備えている。LPF201の遅延量、即ちインダクタンスLdを適度に調整することで、還流ダイオードの電圧におけるサージ電圧を低減させることができる。

(もっと読む)

スイッチ装置

【課題】トランジスタのチャネル部の異常を簡易且つ正確に検出できるスイッチ装置を提供する。

【解決手段】複数の半導体層で形成されて、ゲート電極にゲート電圧を印加されることによってドレイン電極−ソース電極間が導通し、ゲート電圧によって半導体層内で正孔と電子とが結合して発光する電界効果トランジスタ11,12と、ゲート電圧を制御する駆動部21と、トランジスタ11,12の発光量を検出する光検出部231,232とを備え、駆動部21は、光検出部231,232の検出結果に基づいて、トランジスタ11,12の異常を判定し、この判定結果に基づいてゲート電圧を制御する。

(もっと読む)

101 - 120 / 1,001

[ Back to top ]