Fターム[5J055DX72]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 慣用的な複合スイッチ (1,758) | 直列 (1,001)

Fターム[5J055DX72]に分類される特許

141 - 160 / 1,001

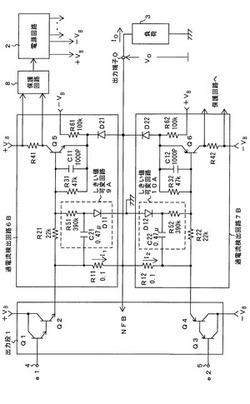

電力増幅器の過電流検出回路及びその方法

【課題】 しきい値を的確に可変して過電流検出の誤作動を防止する。

【解決手段】 過電流検出回路6Bは、Q2のエミッタと出力端子Oの間の電流検出抵抗R11の両端間に抵抗R21、R31が接続されている。R31の両端が過電流検出トランジスタQ5のベース−エミッタ間に接続されており、出力端子Oと−VB の間にダイオードD21、抵抗R61が接続されており、D21のカソードがQ5のエミッタと接続されている。R21とR31の接続点とグランド間には抵抗R51とD11が接続されており、R51とD11の接続点とQ2のエミッタの間にコンデンサC21が接続されている。R51、D11、C21のしきい値可変回路9Aは出力電圧の大きさが大きくなるとしきい値を大きくし、出力電圧の大きさが小さくなるとしきい値を小さくするが、C21とD11により、出力電圧の大きさが増加するときはしきい値を早く増大変化させ、減少するときはしきい値をゆっくり減少変化させる。

(もっと読む)

負荷駆動装置およびその制御方法

【課題】外乱等の影響を受けた場合でも、スイッチング電源のデッドタイムの最適値を誤認することなく、電力損失を低減することが可能な負荷駆動装置を提供する。

【解決手段】負荷駆動装置1は、直流電圧源Vccに直列に接続された2つのスイッチング素子Q1,Q2を有するスイッチング電源回路2と、スイッチング素子Q1,Q2をオン/オフさせる駆動信号を供給するスイッチ制御回路3と、2つのスイッチング素子Q1、Q2の両方がオフとなるデッドタイムを設定するデッドタイム設定回路6とを備えており、デッドタイム設定回路6は、デッドタイムの最適値を探索及び判別する最適値探索部9と、外乱が発生した場合にデッドタイムの最適値の探索及び判別から外乱の影響を排除するための演算を実行する外乱補正演算部10とを含んでいる。

(もっと読む)

インバータ回路および表示装置

【課題】耐圧を上げることなく、消費電力を低減することの可能なインバータ回路およびそれを備えた表示装置を提供する。

【解決手段】7Tr2Cで構成されるインバータ回路において、容量素子C1がトランジスタTr5のソースに接続されるとともに、トランジスタTr4を介してトランジスタTr7のゲートに接続されている。トランジスタTr7のソースには、トランジスタTr2のゲートが接続されている。これにより、入力端子INに立下り電圧が入力され、トランジスタTr1,Tr3,Tr6がオフしたときに、Vddが充電された容量素子C1によって、トランジスタTr7のゲートがVSS+Vth7以上の電圧にチャージされ、トランジスタTr7がオンし、さらにトランジスタTr2がオンする。

(もっと読む)

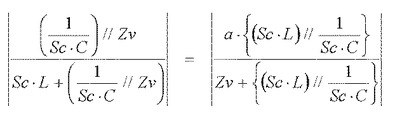

スイッチング回路のノイズ低減装置

【課題】ノイズ低減効果が大きく、小型化が可能なスイッチング回路のノイズ低減装置を提供する。

【解決手段】第1のスイッチングドライバの入力端に入力されるパルス信号と逆位相のパルス信号に基づいて動作する第2のスイッチングドライバと、一端が第2のスイッチングドライバの出力端に接続されるとともに他端がスイッチング回路の出力端子と接続されるインピーダンス素子とを具備し、インピーダンス素子のインピーダンス値Zvと、第1のコイルのインダクタンス値Lと、コンデンサの静電容量値Cと、第1及び第2のスイッチングドライバのスイッチング周波数fcとが、aを0以外の任意の定数として、(数3)の関係を満たす。 (もっと読む)

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、トランジスタの閾値電圧のばらつきに起因する出力電圧のばらつきを抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】6Tr3Cで構成されるインバータ回路において、入力端子IN2に、入力端子IN1に入力されるパルス信号の位相よりも進んだ位相のパルス信号が印加される。これにより、入力端子IN1の電圧がハイからローに変化する際に、トランジスタT5のゲート−ソース間電圧から、トランジスタT5の閾値電圧の影響が取り除かれるので、その後にトランジスタT5がオンしてトランジスタT5に電流が流れたときに、その電流値Idsからも、トランジスタT5の閾値電圧の影響が取り除かれる。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr2Cで構成されるインバータ回路において、トランジスタTr2のソースと低電圧線LLとの間、トランジスタTr5のゲートと低電圧線LLとの間、さらにトランジスタTr2のゲートと低電圧線LLとの間に、入力電圧Vinと低電圧線LLの電圧VLとの電位差に応じてオンオフ動作するトランジスタTr1,Tr3,Tr4が設けられている。トランジスタTr5のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr5のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

誘導素子駆動回路

【課題】 低消費電流化と高速動作化のトレードオフを克服し、貫通電流防止と駆動効率向上を可能にする誘導素子駆動回路を提供する。

【解決手段】 PWM信号を入力する入力端子11と、ソースが第1の電源端子に接続されたPMOS高耐圧トランジスタM0と、ソースがGNDに接続され、ドレインがトランジスタM0のドレインに接続されたNMOS高耐圧トランジスタM1と、トランジスタM0のドレイン及びトランジスタM1のドレインの接続点に設けられ、誘導素子L1を駆動する信号を出力する出力端子12と、出力端子12の電位変化を検出してトランジスタM0をオフした後にトランジスタM1をオンする電圧検出回路9とを備える。この電圧検出回路9は、出力端子12の端子電圧VLXがLowになったことを検知し、Highを出力してトランジスタM1をオンするので、貫通電流を防止する。

(もっと読む)

高周波スイッチ回路

【課題】少なくとも25GHz帯の高周波帯で高性能な特性が得られる高周波スイッチ回路を提供する。

【解決手段】第3整合回路112及び第4整合回路122は、マイクロストリップライン等の分布定数回路で構成されており、特性インピーダンスがZ0で線路長が1/4波長となるように形成されている。第3整合回路112と第1スイッチ113、及び第4整合回路122と第2スイッチ123をそれぞれ組み合わせることで、送信側高周波スイッチ110及び受信側高周波スイッチ120を、ショートまたはオープンの状態に切り替えることができる。送信側高周波スイッチ110または受信側高周波スイッチ120がショート状態になるとそのスイッチが閉となり、オープン状態になると開となる。

(もっと読む)

電子回路

【課題】

内部電源電圧を遮断するパワーダウンモードへの移行を誤動作無く確実に実行するパワーダウンモードの移行シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧から降圧してシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する第1の内部回路30と、電源電圧を供給されて動作する入出力回路24と、第1の内部回路30からの信号を入力し、電源電圧の電圧レベルに変換するレベルシフタ23と、システム電圧発生回路10を制御する制御回路40とを備え、制御回路40は起動信号P4を入力し、この起動信号に所定の遅延時間を与えた短絡制御信号P5を出力する遅延回路100を有し、起動信号はレベルシフタ23を非活性又は活性として制御し、短絡制御信号はシステム電圧発生回路10を停止状態又は動作状態として制御する構成とした。

(もっと読む)

双方向スイッチシステム、双方向スイッチ、スイッチングマトリックスおよび医療用刺激装置を制御する制御回路構造ならびに方法

スイッチタイミング制御回路及び半導体装置

【課題】回路規模を大きくせずに複数のスイッチを貫通電流が流れないように確実に導通非導通のタイミングを制御するスイッチタイミング制御回路を提供する。

【解決手段】複数のデータフリップフロップが縦続接続され、縦続接続されたデータフリップフロップには共通のクロック信号が接続され、それぞれ前段のデータ出力信号が後段のデータ入力信号として接続され、初段のデータ入力信号には、最終段のデータ出力信号の論理が反転されて接続された分周回路と、複数のデータフリップフロップのうちそれぞれ複数の異なるデータフリップフロップの出力信号が入力端子に接続された複数の組み合わせ論理回路と、複数の組み合わせ論理回路の出力信号によりそれぞれ導通、非導通が制御される複数のスイッチと、を備える。

(もっと読む)

半導体装置及び制御方法

【課題】メモリの出力バッファの平均電流値を低減し、消費電流を抑制すること。

【解決手段】本発明に係る半導体装置は、メモリリードアドレスDの連続性を判定し、判定結果Hを出力するアドレス連続性判定回路23と、判定結果Hに基づいて、メモリリードアドレスDに対応するリードデータを出力するメモリの出力バッファ22の駆動能力を制御する駆動能力切り替え制御回路24と、CPUの要求リードアドレスAに対応するリードデータが当該CPUへ到達するまでの期間に、CPU要求リードアドレスAに連続する予想アドレスを生成するアドレス生成部12と、予想アドレスに対応するリードデータを格納するプリロードバッファ14を備える。

(もっと読む)

出力バッファ回路およびそれを用いたドライバ回路

【課題】 入出力信号が変化する際の過渡期間に出力バッファを構成するトランジスタへのバイアス電流を一時的に増強することで、バッファ回路全体の定常的なバイアス電流を抑制しつつ、高スルーレートが得られるバッファ回路を提供する。

【解決手段】 ドライバ回路200は信号レベル発生回路100により発生した信号SGOを出力バッファ回路110を駆動する回路150(プリバッファ回路)を介し、出力バッファ回路110により伝送線路120を駆動することで測定対象回路DUT140に伝える。プリバッファ回路150とこれを模擬したレプリカバッファ回路160とを互いに並列に備え、信号SGOが変化する際の入出力新信号の過渡期間において、レプリカバッファ回路160の出力電流に基づいて出力バッファ回路110の出力段トランジスタQN12、QP22の入力バイアス電流を一時的に増強する。

(もっと読む)

電子スイッチ装置

【課題】商用交流電源から電子機器への電力供給をオン又はオフするために使用者が操作するスイッチ部品として、各国の安全規格を満たさないスイッチ部品であっても自在に利用可能な電子スイッチ装置を提供すること。

【解決手段】本発明によれば、発振手段が、操作スイッチにより二次側コイルの両端が開放されると発振し、該二次側コイルの両端が短絡されると、一次側コイルのインダクタ値の減少に起因し発振が停止するので、二次側コイルの両端の状態が発振手段からの出力の出力態様に反映される。よって、かかる出力態様に基づくことにより、電力供給路の導通又は遮断を操作スイッチの操作状態に応じて行うことができる。ここで、操作スイッチが接続される二次側コイルは、一次側コイルに対して絶縁されているので、各国の安全規格を満たさないスイッチ部品を操作スイッチとして使用したとしても、操作スイッチを操作する使用者の安全を確保できる。

(もっと読む)

半導体基板および半導体装置

【課題】トレンチゲート型などの微細MOSFETにおいて、MOSFETの動作電流とダイオード電流を検出することができる半導体基板を提供する。

【解決手段】半導体基板において、半導体基板1は、主電流領域2と主電流領域2に流れる主電流より小さい電流が流れる電流センス領域3を有し、主電流領域2は、主面にソース電極8が配置され、ソース電極8はp型半導体領域(ボディ)6とn+型半導体領域(ソース)7に接触し、電流センス領域3は、主面にMOSFET電流検出用電極10およびダイオード電流検出用電極11が配置され、MOSFET電流検出用電極10はp型半導体領域(ボディ)6とn+型半導体領域(ソース)7に接触し、ダイオード電流検出用電極11はp型半導体領域(ボディ)6に接触する。

(もっと読む)

半導体スイッチ集積回路

【課題】チップやパッケージのサイズやコストの増加を抑えるとともに、安定動作が実現できる半導体スイッチ集積回路を提供する。

【解決手段】制御電圧印加端子と、オン状態のFETとオフ状態のFETの接続点との間に、抵抗素子を接続する。さらにオフ状態のFETのソース端子とドレイン端子との間に抵抗素子を接続する。その結果、制御電圧以外に外部からGND電位を含めたDC電圧を加えなくとも、半導体スイッチ集積回路を構成するFETのドレイン端子、ソース端子に安定に電圧を供給することができ、オフ状態のFETのソース端子およびドレイン端子の電位を所定の電位に設定することができる。

(もっと読む)

レベルシフト回路、および電力変換装置

【課題】電源電圧の変動の際に、半導体装置の製造ばらつきがあったとしても、容易に誤動作しない低電圧側回路から高電圧側回路に制御信号を伝達するレベルシフト回路を提供する。

【解決手段】レベルシフト回路において、高電圧側の電源電圧変動dV/dtが回路のロジックレベルに影響を与える程度に発生した時において、この変動はセット側にもリセット側にも起こることを利用し、時定数生成回路、もしくは電源電圧変動が先に起こる個所からの信号によって、第1、第2の論理回路において、誤動作の信号が通過するのをマスクして防止する。このマスクするタイミングに充分、余裕をとることにより、半導体プロセスにおける製造ばらつきが個々の素子にあったとしても、高電圧側の電源電圧変動dV/dtが発生時の誤信号がフリップフロップに伝わるのを防止でき、誤動作しない低電圧側回路から高電圧側回路に制御信号を伝達する。

(もっと読む)

パワーオンリセット回路

【課題】誤動作を起こす可能性があった。

【解決手段】電源投入初期もしくは電源電圧降下時にリセット信号を発生し初期化するパワーオンリセット回路であって、電源電圧に応じた電圧を分圧した第1の比較電圧を生成する第1の比較電圧生成部と、電源電圧に応じた第1の電圧を出力する基準電圧生成部と、電源電圧端子と第1のノードとの間に接続され、制御端子に前記第1の電圧を入力するデプレッション型の第1のトランジスタと、前記第1のノードと接地端子との間に接続され、制御端子が前記第1のノードに接続されるエンハンスメント型の第2のトランジスタと、を備え、前記第1のノードの電位に応じた電圧を第2の比較電圧として生成する第2の比較電圧生成部と、前記第1、第2の比較電圧との比較結果に応じてリセット信号を出力する比較器と、を有するパワーオンリセット回路。

(もっと読む)

コンパレータ回路

【課題】低消費電力動作を実現しつつ信号処理に向けた論理判定時間を格段に削減することができる。

【解決手段】入力電圧と参照電圧とを比較して論理判定結果の出力電圧を発生して差動増幅器を含むコンパレータ回路において、微小電流であるバイアス電流を発生して差動増幅器に供給する電流源と、差動増幅器からの差動電圧を反転して反転信号を出力する第1のインバータ回路と、電流源のバイアス電流を検出し、第1のインバータ回路の貫通電流を検出し、検出したバイアス電流及び検出した貫通電流に基づいて、差動増幅器が論理判定を行わない期間はバイアス電流で差動増幅器を動作させる一方、差動増幅器が論理判定する期間はバイアス電流を増加させてなる適応バイアス電流を用いて差動増幅器を動作させるように適応バイアス電流制御を行うための適応バイアス電流を発生して差動増幅器に供給する適応バイアス電流生成回路とを備える。

(もっと読む)

信号保持回路およびこれを使用したシステム保護装置

【課題】電源電圧が低下したときに信号保持回路での信号保持を確実に解除する。

【解決手段】出力端子toを複数の入力端子のうちの1つtbに接続し、残りの外部入力端子taに外部信号が入力される論理和回路14と、該論理和回路14の出力端子に接続された単一パルスを生成するパルス生成回路15とを備え、前記論理和回路14の前記外部入力端子tbにハイレベルのパルス信号が入力されたときに、当該論理和回路14の出力をハイレベルに保持する信号保持回路13であって、前記論理和回路14の前記出力端子toと前記入力端子tbとの間に、電源電圧低下時に当該論理和回路14によるハイレベル保持状態を解除する電圧を高めるダイオードDを介挿した。

(もっと読む)

141 - 160 / 1,001

[ Back to top ]