Fターム[5J055EZ57]の内容

電子的スイッチ (55,123) | 機能的回路 (8,211) | 電源回路、特徴がある定電圧回路 (631) | バッテリ、電池 (74)

Fターム[5J055EZ57]に分類される特許

1 - 20 / 74

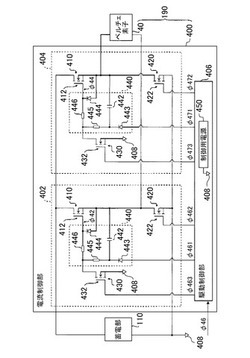

駆動回路および電流制御回路

【課題】ペルチェ素子を加熱および冷却を切替えて使用する。

【解決手段】一端が負荷と接続され、他端が負荷を駆動する駆動用電源と接続され、少なくとも、入力端子に入力される第1の制御信号に応じてオン状態およびオフ状態を切り替える第1のスイッチング素子と、一端が負荷および第1のスイッチング素子の一端と接続され、他端が基準電位と接続され、第2の制御信号に応じてオン状態およびオフ状態を切り替える第2のスイッチング素子と、第2のスイッチング素子がオフ状態である場合に、第1のスイッチング素子の入力端子に電圧を供給する電圧供給部と、第1の制御信号および第2の制御信号のそれぞれを、第1のスイッチング素子および第2のスイッチング素子のそれぞれに供給し、第1のスイッチング素子と第2のスイッチング素子とを交互にオン・オフ動作させる制御部とを備える。

(もっと読む)

ゲートタイミング制御回路

【課題】半導体スイッチ,負荷電流,温度,主回路構成等によるサージ電圧の波形に応じて半導体スイッチの動作タイミングを調整することなく、各半導体スイッチの電圧分担を均等化させる。

【解決手段】直列接続された複数の半導体スイッチA,Bに出力されるゲート信号のタイミングを調整するゲートタイミング制御回路3において、コンパレータ4,4により、各半導体スイッチA,BのVce検出(A),(B)と、予め設定されたしきい値とを比較してVce検出における立ち上がりのタイミングを示すVce信号(A),(B)を出力する。そして、時間差制御部8において、ゲート信号に基づいて、前記各Vce信号(A),(B)の変化のタイミングが整合するように生成されたゲート出力(A),(B)をゲートドライバ2に出力する。

(もっと読む)

入出力回路

【課題】回路規模の増大を抑制しながら、コネクタに接続されたチャージャーの種類を的確に認識する。

【解決手段】電源検出回路12は、VBUS端子への外部からの給電を検出する。チャージャー検出回路14は、DP端子およびDM端子の電圧を検出することにより、チャージャーの種類を特定する。チャージャー検出回路14は、DP端子およびDM端子の少なくとも一方のオープン、プルアップ、プルダウンまたは両端子間のショートを検出する。

(もっと読む)

無線通信装置及び高周波スイッチ回路

【課題】回路規模が小さく、かつ消費電力の小さい無線通信装置及び高周波スイッチ回路を提供する。

【解決手段】無線通信装置100は、共用アンテナ101と、整合回路110、120と、高周波スイッチ回路130と、充電電力受電回路140と、応答器150と、から構成される。高周波スイッチ回路130は、電界効果トランジスタ131、132と、検波回路と、を備える。電界効果トランジスタ131、132のソース端子は共通接続される。検波回路は共通接続点に接続され、電界効果トランジスタ131のドレイン端子から出力された高周波信号を検波し、共通接続点の電位を基準とした検波電圧を電界効果トランジスタ131、132のゲート端子に印加する。電界効果トランジスタ131、132のドレイン端子間のインピーダンスは検波電圧に従って変化する。

(もっと読む)

地絡保護回路及びこれを用いたスイッチ駆動装置

【課題】部品点数の増加や出力効率の低下、セットのコストアップ、モノリシックICで実現する場合のチップ面積の増大を低減できる、スイッチ駆動装置用地絡保護回路の提供。

【解決手段】ブートストラップ回路D1、C1の充電電流IBが流れる経路上に設けられたセンス抵抗R3と、センス抵抗R3の両端間電圧ΔVと所定の閾値電圧Vthとを比較して地絡保護信号S1を生成するコンパレータ361と、前記ブートストラップ回路の正規充電動作中には地絡保護信号S1を無効としておく論理ゲート362と、を有する。

(もっと読む)

半導体回路、半導体装置、及び電池監視システム

【課題】過大電流による素子の破壊を防止することができる、半導体回路、半導体装置、及び電池監視システムを提供する。

【解決手段】短絡保護回路30のPMOSトランジスタMP3により短絡状態の場合は、電源電圧VDDからFETゲート電圧出力端子FET_PAD(外部FET0)に電流が流れる経路をPMOSトランジスタMP0及び短絡電流検出用抵抗素子R0を経由する経路から、PMOSトランジスタMP1及び抵抗素子Rpuを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC14が破壊されるのを防止することができる。

(もっと読む)

電気負荷駆動装置

【課題】電気負荷に電流を流す複数の各トランジスタが設けられている並列な通電用配線の断線を、各トランジスタに大きな電流負担をかけることなく、また電気負荷への通電を中断してしまうことなく検出する。

【解決手段】トランジスタTr1,Tr2によりリレーのコイル13aに通電する装置11では、コイル13aへの通電期間中に、電圧変動制御部31が、トランジスタTr1,Tr2へのゲート電圧VG1,VG2の両方を定期的に所定時間だけ低下させることにより、両トランジスタTr1,Tr2の通電能力が落ちてドレイン・ソース間電圧が所定値以上になる検査用期間を発生させ、該検査用期間中に、故障判定部32が、各トランジスタTr1,Tr2のドレイン・ソース間電圧を監視し、ドレイン・ソース間電圧が判定値未満のトランジスタがあれば、該トランジスタが設けられている通電用配線の反負荷側部分(LD1又はLD2)が断線していると判定する。

(もっと読む)

電気負荷駆動装置

【課題】電気負荷に電流を流す複数の各トランジスタが設けられている並列な通電用配線の断線を、各トランジスタに大きな電流負担をかけることなく、また電気負荷への通電を中断してしまうことなく検出する。

【解決手段】2つのトランジスタTr1,Tr2によりリレーのコイル13aに通電するECU11では、コイル13aへの通電期間中に、電圧変動制御部31が、トランジスタTr1,Tr2へのゲート電圧VG1,VG2の各々を定期的に且つ互いに時間をずらして所定時間だけ低下させることにより、一方のトランジスタの通電能力が落ちてドレイン・ソース間電圧が所定値以上になる期間を発生させる。そして、故障判定部32は、各トランジスタのソース電圧VS1,VS2の差が所定の閾値以上になったことを検知すると、トランジスタTr1,Tr2が設けられている通電用配線L1,L2の負荷側部分LS1,LS2の何れかが断線していると判断する。

(もっと読む)

駆動装置、スイッチ装置、および試験装置

【課題】非反転増幅によるFETドライブ回路を提供する。

【解決手段】第1基準電圧出力部と、入力端子および第1基準電圧出力部の間に位置する第1端子および第2端子の間に設けられ、第1端子から第2端子へと流れる電流に応じて電圧を降下させる第1電圧降下部と、第1端子および出力端子の間に接続された第1電流源と、第2基準電圧を出力する第2基準電圧出力部と、出力端子および第2端子の間に設けられ、第2基準電圧と第2端子の電圧との差に応じてオンまたはオフとなる第1スイッチ部と、第1スイッチ部がオンおよびオフの状態における第1電圧降下部が降下させる電圧の変化を補償する補償部と、を備える駆動装置を提供する。

(もっと読む)

誘導性負荷駆動装置

【課題】電源回路における回路素子の破壊を防止することが可能な誘導性負荷駆動装置を提供する。

【解決手段】誘導性負荷駆動装置の構成として、電源回路の出力端子と誘導性負荷の一端との間に介挿された第1のスイッチング素子と、前記誘導性負荷の他端とアースとの間に介挿された第2のスイッチング素子と、前記第1及び第2のスイッチング素子の両方がオフの時に前記誘導性負荷の他端から出力される逆起電流を前記電源回路の出力端子に回生させる逆起電流回生回路と、前記電源回路の出力電圧が予め設定された閾値以上となった場合に、前記第2のスイッチング素子をオンにする回路素子保護回路と、を備えた構成を採用する。

(もっと読む)

電気回路、充電制御装置、充電システム、および制御方法

【課題】より簡易的な構成で半導体スイッチを駆動する回路を実現する。

【解決手段】充放電切替回路11は、プラス側の電力線に挿入される半導体スイッチ12−1および12−2と、入力側の端子に入力される入力電圧を、所定の出力電圧に変換して出力側の端子から出力する絶縁型DCDCコンバータ23−1および23−2とを備える。そして、絶縁型DCDCコンバータ23−1および23−2の出力側のマイナス端子がプラス側の電力線に接続され、絶縁型DCDCコンバータ23−1および23−2の出力側のプラス端子が半導体スイッチ12−1および12−2の開閉を制御する端子に接続される。本発明は、例えば、高電圧の電源の充放電を制御する回路に適用できる。

(もっと読む)

負荷制御装置

【課題】FET(T1)のドレイン電圧の低下量が大きくなった場合であっても過電流を検出するための回路を正常に作動させることが可能な負荷制御装置を提供する。

【解決手段】FET(T1)のゲートとドレインとの間にコンデンサC1を設けることにより、点P1の電圧V1が減少した場合に、FET(T1)のゲート電流がコンデンサC1側にバイパスしてFET(T1)に流れ、FET(T1)のゲートに供給される電荷量が低減する。このため、FET(T1)のドレイン電流の増加を抑制でき、電圧V1の急激な変動を防止できる。その結果、比較器CMP1が作動不能となる程度まで電圧V1が低下することを防止でき、比較器CMP1が誤動作することを防止できる。

(もっと読む)

負荷制御装置

【課題】ノイズ対策用のコンデンサC1を設置した場合であっても過電流を検出するための回路を正常に作動させることが可能な負荷制御装置を提供する。

【解決手段】プラス端子P11とマイナス端子P12より電力が供給されて駆動する制御回路10により、FET(T1)のオン、オフを切り替えて、負荷RLの駆動、停止を制御する場合に、マイナス端子P12とグランドとを接続するアース線に、抵抗R5とダイオードD1の並列接続回路を設ける。従って、入力スイッチSW1の投入時にプラス端子11とマイナス端子12の間に配置されたコンデンサC1の放電電流I2が流れる場合であっても、抵抗R5の電圧降下VR5によりマイナス端子P12の電圧をグランドレベルよりも相対的に低くすることができ、コンデンサC1の両端電圧VC1を拡大させて、放電電流I2を抑制し、電圧V1の低下を抑えることができる。

(もっと読む)

負荷制御装置

【課題】ノイズ対策用のコンデンサC1を設置した場合であっても過電流を検出するための回路を正常に作動させることが可能な負荷制御装置を提供する。

【解決手段】FET(T1)のゲートとドレインとの間に第2のコンデンサC2を設けることにより、点P1の電圧V1が減少した場合に、FET(T1)のゲート電流がコンデンサC2側にバイパスしてFET(T1)に流れ、FET(T1)のゲートに供給される電荷量が低減する。このため、FET(T1)のドレイン電流の増加を抑制でき、電圧V1の急激な変動を防止できる。その結果、比較器CMP1が作動不能となる程度まで電圧V1が低下することを防止でき、比較器CMP1が誤動作することを防止できる。

(もっと読む)

半導体装置

【課題】コモンノイズを低減する。

【解決手段】半導体装置10は、直列に接続された半導体スイッチング素子11,12と、正極端子13と、負極端子14と、出力端子15とを具備する半導体モジュール16と、半導体モジュール16に絶縁されたボディ17とを備える。ボディ17と、各端子13,15,14およびデバイスとの間の各浮遊容量C1,C2,C3,C0と、ボディ17の浮遊インダクタンスLbと、コモンノイズの電流経路に応じた角速度ωとに対して、

[1/(ω・C1)<{ω・Lb+1/(ω・C0)}]と、[1/(ω・C3)<{ω・Lb+1/(ω・C0)}]と、(C2<C1)と、(C2<C3)とを満たす。

(もっと読む)

半導体集積回路装置

【課題】出力トランジスタの過電流を簡略な回路構成で抑制する。

【解決手段】半導体集積回路装置70の過電流保護回路30には、過電流検出部1と過電流制御部2が設けられる。過電流検出部1には、電流源11乃至13、NPNトランジスタQ1乃至Q3が設けられる。NPNトランジスタQ1及びNPNトランジスタQ2は第1のカレントミラー回路を構成し、NPNトランジスタQ2のコレクタ側から過電流検出信号Skkを出力する。NPNトランジスタQ1及びNPNトランジスタQ3は、第2のカレントミラー回路を構成し、NPNトランジスタQ3のコレクタ側から過電流制御信号Sksを過電流制御部2に出力する。過電流保護回路30は、出力トランジスタMDT1に流れる過電流を出力トランジスタMDT1のソースと抵抗R1の間で検出して、過電流を抑制する。

(もっと読む)

電子回路

【課題】

内部電源電圧を遮断するパワーダウンモードへの移行を誤動作無く確実に実行するパワーダウンモードの移行シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧から降圧してシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する第1の内部回路30と、電源電圧を供給されて動作する入出力回路24と、第1の内部回路30からの信号を入力し、電源電圧の電圧レベルに変換するレベルシフタ23と、システム電圧発生回路10を制御する制御回路40とを備え、制御回路40は起動信号P4を入力し、この起動信号に所定の遅延時間を与えた短絡制御信号P5を出力する遅延回路100を有し、起動信号はレベルシフタ23を非活性又は活性として制御し、短絡制御信号はシステム電圧発生回路10を停止状態又は動作状態として制御する構成とした。

(もっと読む)

負荷駆動装置

【課題】FETをオン状態に維持するための電流を従来よりも低減することができる負荷駆動装置を提供する。

【解決手段】FET11のソースは、ヒューズ2を介してバッテリ電圧+Vに接続され、FET11のドレインには電気負荷1を接続してある。FET11のゲートには、コンデンサ121と抵抗122で構成される直列回路12のコンデンサ121と抵抗122との接続ノードが接続されている。直列回路12には、FET14を直列に接続している。コンデンサ121の両端には、FET15のソース、ドレインが接続されている。FET15のゲートには、抵抗16と抵抗18との接続ノードが接続されている。抵抗17には、FET18を接続している。

(もっと読む)

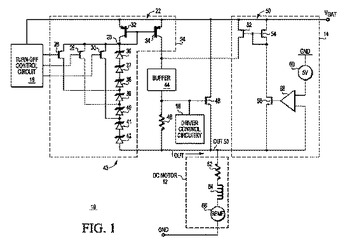

ターンオフ制御を有する電力トランジスタおよびその動作方法

回路が、電力トランジスタ48、駆動制御回路16、可変クランプ回路24、およびターンオフ制御回路18を有する。電力トランジスタが、第1電源端子に接続される第1電流電極、回路の出力50としての第2電流電極、および制御電極を有する。駆動制御回路が、電力トランジスタの制御電極に接続される出力を有して、回路のアクティブモードの間、電力トランジスタを制御する。可変クランプ回路は、回路の出力と第1電源端子との間に接続される。ターンオフ制御回路は、可変クランプ回路に接続され、回路をアクティブモードから非アクティブモードに移行する間、可変クランプ回路のクランプレベルを選択する。  (もっと読む)

(もっと読む)

スイッチング回路

【課題】 受信機が受信するノイズを低減することができるスイッチング回路を提供すること。

【解決手段】 パワートランジスタM1を駆動して負荷5を作動させる駆動電圧波形を生成するスイッチング回路1において、ラジオ受信機7が受信している送信局の周波数を検出する受信周波数検出部33と、負荷5を制御する制御パルスを生成する制御パルス生成部と、駆動電圧の変位により生じる高調波のスペクトル包絡線の谷部が、ラジオ受信機7が受信している送信局の周波数を含むように駆動電圧波形の立ち上がり部分と立ち下がり部分の波形を生成する最適波形記憶部32と、最適波形記憶部32が生成した駆動電圧波形の立ち上がり部分と立ち下がり部分の波形を、制御パルスに適用して駆動波形を生成する波形生成部31とを備えた。

(もっと読む)

1 - 20 / 74

[ Back to top ]