Fターム[5J055FX05]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 帰還を行うもの (2,113) | 電気信号に変えられる現象、物理量 (2,102) | 電圧値 (1,457)

Fターム[5J055FX05]に分類される特許

201 - 220 / 1,457

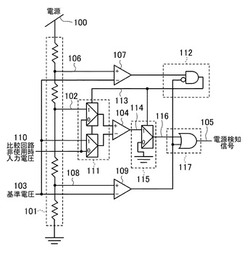

電源検知回路

【課題】電源検知回路において、BT劣化によって比較回路のミスマッチが増大することに起因する電源検知信号の精度の劣化を抑制する。

【解決手段】検知用比較回路104は、入力切替信号生成回路112によって、その出力の活性状態と非活性状態との切替時付近では、入力信号102と基準電圧103とを入力して、その両者の比較を行う。一方、前記切替時付近以外では、比較回路非使用時入力電圧110が検知用比較回路104に入力されて、その差動入力が同電位に固定される。従って、BT劣化による電源検知精度の経年劣化が有効に抑制される。

(もっと読む)

交流スイッチ

【課題】高耐圧の用途に適用可能な交流スイッチ(半導体リレー)を提供する。

【解決手段】交流スイッチ1は、ソース(S)同士を接続した第1化合物半導体MOSFET11および第2化合物半導体MOSFET12と、第1化合物半導体MOSFET11のドレイン(D)に接続された第1出力端子13と、第2化合物半導体MOSFET12のドレイン(D)に接続された第2出力端子14とを含む。交流スイッチ1は、オフ時の第1出力端子13および第2出力端子14の間の耐圧が400V以上(より好ましくは600V以上)であり、オン時の第1出力端子13および第2出力端子14の間の抵抗が20mΩ以下(より好ましくは10mΩ以下)である。

(もっと読む)

CMOSアナログスイッチ回路、負電圧サンプリング回路

【課題】オン抵抗が低い導通状態で、グランド電圧に対して正電圧側と負電圧側に振幅する大信号入力を可能とするCMOSアナログスイッチ回路を提供する。

【解決手段】PMOSトランジスタ101、NMOSトランジスタ102のソース同士を入力端子106に接続し、ドレイン同士を出力端子107に接続して構成される相補構成のCMOSアナログスイッチ回路103において、PMOSトランジスタ101のバックゲートに正電源電圧を供給し、NMOSトランジスタ102のバックゲートに負電源電圧を供給し、正電源電圧または負電源電圧のうち、いずれか一方を負電圧制御信号S1としてPMOSトランジスタのゲートに供給し、他方を負電圧制御信号S2としてNMOSトランジスタのゲートに供給する。

(もっと読む)

負荷容量の駆動回路

【課題】2相クロックによる負荷容量の駆動において、負荷容量間の電荷の再利用を行うと共に、出力クロックの高速化を容易にする。

【解決手段】第1クロック信号とその逆位相の第2クロック信号とに対してそれぞれ遅延した第1及び第2遅延クロック信号が生成される。インバータ回路は第1クロック信号と第1遅延クロック信号とが逆位相である逆転期間において第1クロック信号と逆位相の第1電位を第1出力ノードに生成し且つ第2クロック信号と逆位相の第2電位を第2出力ノードに生成し、第1クロック信号と第1遅延クロック信号とが同位相である一致期間において第1出力ノードと第2出力ノードとをハイインピーダンスとする。スイッチ回路は、逆転期間において第1出力ノードと第2出力ノードとを接続するオン状態とする。第1出力ノードと第2出力ノードとは、駆動対象回路の負荷容量に接続される。

(もっと読む)

活線挿抜制御回路

【課題】解除電圧のばらつきを低減した活線挿抜制御回路を提供する。

【解決手段】実施形態によれば、出力回路と、電圧発生回路と、検出回路と、補正回路とを備えた活線挿抜制御回路が提供される。前記出力回路は、活線挿抜基板に設けられた半導体装置の出力信号を電源電圧が解除電圧以下のときディスエーブルに切替え、前記電源電圧が前記解除電圧よりも高いときイネーブルに切替えることのできるイネーブル信号を生成する。前記電圧発生回路は、前記電源電圧が供給されるMOSFETを含み、前記電源電圧に応じて変化し前記解除電圧を検出する基準となる第1の電圧を発生する。前記検出回路は、前記第1の電圧を検出する。前記補正回路は、前記検出回路の出力に応じて前記第1の電圧を一定値に補正する。

(もっと読む)

モータ制御装置及びバルブタイミング調整装置並びにインバータ回路の通電制御方法

【課題】モータの実回転方向が回転方向指令と逆になった場合に、フリーホイールダイオードにおいて発生する損失を軽減できるモータ制御装置を提供する。

【解決手段】制御回路60は、外部より指令として与えられるモータ4の目標回転方向Dtと、回転角センサSU,SV,SWが出力するセンサ信号に基づき信号生成ブロック72により検出されるモータ4の実回転方向Drとが相違する方向不一致状態を検出すると、120度通電方式から180度通電方式に切り替えてインバータ部76を構成する上段スイッチング素子FU,FV,FWのオン期間を進み位相側に拡げるように制御し、還流電流を上段スイッチング素子FU,FV,FWを介して流す。

(もっと読む)

タイマー回路

【課題】容量素子を利用したタイマー回路において、容量素子が短絡状態になったことを検出することができるタイマー回路を提供する。

【解決手段】容量素子の充電又は放電が開始されてから、容量素子Cの電位と、グランドGDNの電位より高く電源VDDの電位より低い基準電圧VREF_Hの電位とを比較して、容量素子Cの電位が基準電圧VREF_Hの電位に到達した場合に、予め定められたタイムアップ信号を出力するコンパレータCMP1と、容量素子Cの電位が、グランドGNDの電位より高く基準電圧VREF_Hの電位より低い基準電圧VREF_Sの電位より高くなるように制御する制御部と、容量素子Cの電位と基準電圧VREF_Sの電位とを比較して、容量素子Cの電位が基準電圧VREF_Sの電位より低くなった場合に、前記容量素子の短絡状態が検出された旨を示す短絡検出信号を出力するコンパレータCMP2と、を備える。

(もっと読む)

半導体スイッチ回路

【課題】低周波帯域において線形性劣化のない半導体スイッチ回路を提供する。

【解決手段】入出力端子間に直列にソースおよびドレインを接続した1又は2以上の電界効果トランジスタと、電界効果トランジスタのゲートに接続した抵抗を備えた半導体スイッチ回路において、電界効果トランジスタのゲート−ドレイン間およびゲート−ソース間に、キャパシタをそれぞれ接続可能とした。

【効果】FETのゲート−ドレイン間およびゲート−ソース間すべてにキャパシタを接続したことにより、従来より低い周波数帯域においてゲート電極に接続する抵抗よりFETのインピーダンスが十分低くなるため、線形性を向上させることが可能となる。

(もっと読む)

ランプ波形生成装置および方法

【課題】本発明は、ランプ波形生成装置および方法に関する。

【解決手段】ランプ波形生成装置は、入力信号を用いて基準波形を生成し、負荷の電圧と基準波形の電圧を比較して第1端子が負荷に連結していて第2端子が電源に連結しているスイッチをオンオフさせる駆動制御信号を生成する。このような駆動制御信号に応じてスイッチのオンオフが反復しながらランプ波形が生成される。

(もっと読む)

スイッチング素子駆動回路

【課題】電力伝送効率が良く、より小型化できるスイッチング素子駆動回路を提供する。

【解決手段】スイッチング素子102のゲート信号を発生させる制御演算装置101と、スイッチング素子と制御演算装置との絶縁を確保するトランス110と、第1の周波数とより速い第2の周波数の信号を発生する発振装置105,107と、ゲート信号の立ち上がり及び立ち下りの瞬間に一定時間だけ第1の周波数から第2の周波数に変化させた交流信号を出力する交流周波数変更手段111と、第1の周波数を第1のゲインにて変圧し、第2の周波数をより大きな第2のゲインで変圧して出力する共振回路110,109と、交流信号の振幅変化に従ってゲート信号の立ち上がり及び立ち下がりを復調して復調ゲート信号を出力する復調回路132,133,134と、復調ゲート信号によりスイッチング素子のゲートをオン/オフ駆動するゲートドライブ回路142,143を備えている。

(もっと読む)

ワイヤ遷移を検出し支援する回路および方法

【課題】ワイヤ上の信号遷移を支援する回路及び方法を提供する。

【解決手段】回路は、第1のサブ回路を含み、サブ回路は、回路の出力(34)に結合されている第1のトランジスタ(16)を、立ち上がり遷移の間ターンオンさせ、その後ターンオフさせる。第1のトランジスタ(16)は、出力(34)を高状態に駆動して、立ち上がり遷移を支援する。回路は、第2のサブ回路を含み、第2のサブ回路は、回路の出力(34)に結合されている第2のトランジスタ(25)を、立ち下がり遷移の間ターンオンさせ、その後ターンオフさせる。第2のトランジスタ(25)は、出力(34)を定状態に駆動して、立ち下がり遷移を支援する。

(もっと読む)

スイッチングゲートドライバ

【課題】スイッチングゲートドライバにおいて、スイッチング時間を短くして、スイッチング損失を低減すること。

【解決手段】本発明は、IGBT素子のスイッチングゲートドライバであって、IGBT素子のゲート電流を制御するための抵抗部、及び、前記IGBT素子のコレクタ−エミッタ間の電圧に応じて、前記抵抗部の可変抵抗を制御するための制御信号を前記抵抗部に出力する電圧検針部を含むスイッチングゲートドライバを提供する。

(もっと読む)

位相制御装置

【課題】位相制御装置において、トランジスタに与えるゲート駆動電圧を、簡単な構成を用いて全波整流により生成する。

【解決手段】スイッチング手段3は、ソースが交流電源1の一端と、ドレインが負荷2の一端と接続される第1トランジスタ31と、ソースが交流電源1の他端と、ドレインが負荷2の他端と接続される第2トランジスタ32とを含む。定電圧生成手段7のダイオードブリッジ71の一方の入力端子は、交流電源1と第1トランジスタ31の接続点に接続され、ダイオードブリッジ71の他方の入力端子は、交流電源1と第2トランジスタ32の接続点に接続される。定電圧生成手段7の出力端子間には、抵抗72とツェナーダイオード74及びコンデンサ73の並列回路とが直列に接続される。トランジスタ31,32の制御端子の電位は、この並列回路と抵抗72の接点の電位と、ダイオードブリッジ71の負側の出力端子の電位との間で切り換わる。

(もっと読む)

レギュレータ用半導体集積回路

【課題】 外部から回路をオン、オフ制御するための制御端子を有するレギュレータ用ICにおいて、制御信号による起動直後に出力端子に向かってラッシュ電流が流れるのを防止できるようにする。

【解決手段】 制御回路のオン、オフを指示する制御信号が入力される外部制御端子(CE)とを備えたレギュレータ用ICにおいて、電圧入力端子または出力端子と接地電位端子との間に直列に接続された電流源(Tr0,R3)と基準電圧回路(Tr2,Tr3)を設け、該電流源と基準電圧回路との接続ノードは外付けのコンデンサが接続される外部端子(CS)に接続し、基準電圧回路はデプレッション型MOSトランジスタとエンハンスメント型MOSトランジスタが直列に接続され、それらのトランジスタのしきい値電圧の差に相当する電圧を出力するように構成した。

(もっと読む)

電子制御装置

【課題】複数の開閉素子と第二の多チャンネルAD変換器を内蔵したインテリジェントパワーモジュール(IPM)において、多様な制御信号に対応したデジタル変換値をマイクロプロセッサで正確に読み出す。

【解決手段】電子制御装置100A内のCPU110Aは、直並列変換器114a、114bと第二の多チャンネルAD変換器116bを介してIPM190A内の開閉素子140nの通電電流を読み出し、開閉素子140nは、シリアル制御信号SRn又はパラレル制御信号PWMnによって開閉制御され、読出時期制御回路170nは、制御信号の種別を問わず常に開閉素子140nが閉路駆動されている期間に読出しするよう読出タイミングを調整するように構成され、直並列変換器によってIPMとマイクロプロセッサ間の配線数が削減できると共に、シリアル信号とパラレル信号間のタイミング誤差を調整して、正確にデジタル変換値を読み出す。

(もっと読む)

半導体集積回路および高周波モジュール

【課題】出力波形のリップルを低減可能な半導体集積回路を提供する。

【解決手段】例えば、高周波スイッチ回路RFSWと、そのオン・オフを制御するスイッチ制御回路SWCTLを備え、SWCTLは、2個のダウンコンバータ回路VGEN1,VGEN2と、レベルシフト回路LS[1]〜LS[4]を備える。各LS[n]は、レベルシフト段LSSG[n]とその後段に接続された出力段OTSG[n]を持ち、RFSWは、OTSG[n]からの制御信号OUT[n]によって制御される。LSSG[n]は、VGEN1からの負の電源電圧(−VSS1)を用いて動作し、OTSG[n]は、VGEN2からの負の電源電圧(−VSS2)を用いて動作する。−VSS1では、LSSG[n]のレベルシフト動作に伴いリップルが生じ得るが、−VSS2ではOTSG[n]の動作がスイッチング動作であるためリップルが生じ難い。

(もっと読む)

負荷駆動回路

【課題】誘導性負荷の逆起電力による負荷駆動装置における誤動作を防止する。

【解決手段】出力トランジスタQN1にオン電流が流れている場合、第2トランジスタMN4aは、出力トランジスタQN1のソースに供給された電源電圧を第1トランジスタMN2のバックゲートに供給する。一方、出力トランジスタQN1においてオン電流の逆方向の負電流が流れている場合、第2トランジスタMN4aは、出力トランジスタQN1のドレインに供給された電源電圧を第1トランジスタMN2のバックゲートに供給する。

(もっと読む)

駆動回路及びこれを含む電源装置及び電気装置

【課題】駆動回路及びこれを含む電源装置及び電気装置を提供する。

【解決手段】制御端子及び出力端子を有するスイッチング素子、及び制御端子と出力端子との間の電圧が臨界電圧以下に維持されるように、前記スイッチング素子を制御するための駆動電圧が目標レベルに達するのにかかる上昇時間を制御する制御部を含み、制御端子と出力端子との間の電圧が臨界電圧より高ければ、制御端子と出力端子との間に漏れ電流が発生する電源装置である。

(もっと読む)

パワーオンリセット回路

【課題】回路の消費電流を低減可能な、パワーオンリセット回路を提供すること。

【解決手段】抵抗分圧回路(R3,R4)によって得られた電源電圧VDDの検出電圧Vcが基準電圧Vrefを超えているとき、リセット解除信号を出力するコンパレータC2と、基準電圧Vrefよりも高い所定電圧を検出する第2の電圧検出回路D2と、第2の電圧検出回路D2によって前記の所定電圧が検出されているときに抵抗分圧回路(R3,R4)とコンパレータC2に流れる電流を遮断するスイッチM1,M2と、スイッチM1,M2によって電流が遮断されているときにリセット解除信号の出力を補償する補償回路とを備え、第2の電圧検出回路D2の消費電流を、抵抗分圧回路(R3,R4)とコンパレータC2との合計消費電流よりも低く設定した、パワーオンリセット回路。

(もっと読む)

ゲート駆動回路

【課題】本発明は、レベルシフト高圧トランジスタのゲートに接続される電源の電圧が高い場合にも低い場合にも弊害なく稼動するゲート駆動回路を提供することを目的とする。

【解決手段】ゲート電圧の波形がパルス信号で制御されるレベルシフト高圧トランジスタと、該レベルシフト高圧トランジスタのゲートと電源を接続する抵抗と、該レベルシフト高圧トランジスタのドレインと接続され、該レベルシフト高圧トランジスタのドレイン電流に応じてゲート駆動信号を出力する高電圧回路と、該レベルシフト高圧トランジスタのソース及びゲートと接続され、該ドレイン電流が増大すると該抵抗を流れる電流を増大させるように構成されたカレントミラー回路と、該電源の電源電圧が低い場合は該抵抗の抵抗値を低減させ、該電源の電源電圧が高い場合は該抵抗の抵抗値を維持する抵抗調整手段とを有する。

(もっと読む)

201 - 220 / 1,457

[ Back to top ]