Fターム[5J056DD51]の内容

Fターム[5J056DD51]の下位に属するFターム

浮遊容量、寄生容量 (42)

Fターム[5J056DD51]に分類される特許

161 - 180 / 589

出力バッファ回路

【課題】出力遅延を短縮できる出力バッファ回路を提供する。

【解決手段】信号PenがLレベルからHレベルに切り替わり信号NenがHレベルからLレベルに切り替わった直後において、定電流源Is1が追従しきれずまた切り替わっていない場合には、ノードPは未だHレベルのままであるので、ノードOUTはLレベルのままである。この状態で、切り替え前にHレベルのノードNに接続されていたノードAは、切り替えによりHレベルのノードPへ接続される。これと同時に、インバータinv3の出力部がHレベルからLレベルに切り替わっているので、キャパシタC2を介して、ノードAもHレベルからLレベルに切り替えられる。このとき、ノードPの電位はノードAと等しくなるまで引き下げられ、Lレベルへ遷移する。

(もっと読む)

RFID用リーダ装置及びその制御方法

【課題】直流遮断コンデンサを用いるリーダ装置の送受信の切り替え待機時間を短縮する。

【解決手段】リーダ装置2は、RFID3に対し、高周波搬送波信号を送信する送信回路4と、送信回路5により送信された高周波搬送波信号から、RFID3の応答データを抽出する受信回路5とを備え、受信回路5は、高周波搬送波信号を検波する検波回路14と、検波回路14による検波後の高周波搬送波信号の信号処理を行い、RFID3の応答データを取得する信号処理回路18と、検波回路14と信号処理回路18とを接続する配線に間挿された直流遮断コンデンサ15と、直流遮断コンデンサ15と直列に接続され、オフのときに直流遮断コンデンサ15の少なくとも一方の端子をオープンとするスイッチ素子16とを有することを特徴とする。

(もっと読む)

送信ドライバ回路

【課題】フリーホイールダイオードを用いることなく、より低い電圧のアンダーシュートでも低減できる送信ドライバ回路を提供する。

【解決手段】PチャネルMOSFET22のドレインをグランドに接続して、NチャネルMOSFET21,PチャネルMOSFET22のソースをそれぞれ信号線3H,3Lに接続する。第1データ電圧設定部41は、信号出力部がハイレベル信号を出力すると、ゲート21G,22G間の電位差を(2・R1・Iref)にする電圧信号を設定し、第2データ電圧設定部42は、信号出力部がロウレベル信号を出力すると、ゲート21G,22G間の電位差をゼロにする電圧信号を設定する。これらの作用により、伝送線路3を構成する信号線3H,3L間の電圧を変化させて差動信号を伝送する。

(もっと読む)

レベルシフト回路、信号駆動回路、表示装置および電子機器

【課題】内部波形や出力波形の振幅を保ちつつ、入力された信号の振幅よりも大きな振幅の信号を出力できるレベルシフト回路を得る。

【解決手段】第1および第2の入力信号(セット信号VSおよびリセット信号VR)が供給される第1の入力回路(MOSトランジスタ11,12)と、第1および第2の入力信号が供給される第2の入力回路(MOSトランジスタ13,14)と、第1の入力信号に同期した第3の入力信号(反転セット信号VSb)が一方に供給され、他方が第2の入力回路の出力端子に接続された第1の容量素子22と、第2の入力回路の出力端子と電源PVSSとの間に挿入配置された第2の容量素子23と、第1および第2の入力回路の出力電圧に基づいて、前記第1から第3の入力信号の振幅よりも大きな振幅の出力信号VOutを生成する出力回路(MOSトランジスタ16,17)とを備える。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、3つのトランジスタTr21,Tr22,Tr23を有している。そのうちの2つのトランジスタTr21,Tr22は、デュアルゲート型のトランジスタである。これらトランジスタTr21,Tr22のバックゲートの電圧を調整することにより、トランジスタTr21,Tr22の閾値電圧を調整することができる。

(もっと読む)

バッファ回路

【課題】出力の反射を抑制しつつスルーレートを高い自由度を持って調整可能なバッファ回路を提供する。

【解決手段】

複数の出力トランジスタPOA1〜POE1は、電源端子(電源電圧VCCQ)と出力端子DoutP1との間に電流経路を並列接続され導通することにより出力端子DoutP1の電圧を変化させる。ゲート制御用トランジスタTA1〜TE1は、接地端子Dgndと出力トランジスタPOA1〜POE1のゲートとの間、又は2つの出力トランジスタのゲートの間に電流経路を形成するように接続され、出力トランジスタにゲート電圧を与える。ゲート制御用トランジスタTA1〜TE1のゲートは、ゲート制御用トランジスタTA1〜TE1のソースの電圧が変化したときにゲート−ソース間の電位差が閾値電圧以上となって導通するよう、所定の電圧を与えられている。

(もっと読む)

半導体集積回路、半導体装置及び電子機器

【課題】内部動作に起因する半導体基板の電位的変動を抑制することが容易な半導体集積回路を提供する。

【解決手段】半導体集積回路(1)の内部において、外部電源端子(Pvcc)と半導体基板(Psub)との間および外部グランド端子(Pvss)と半導体基板との間の何れか一方又は双方に可変インピーダンス回路(VZ)を配置し、可変インピーダンス回路に対するインピーダンスの設定に従って、半導体集積回路に形成されたトランジスタの動作に応じて半導体基板に生起される電源電圧側の変動成分とグランド電圧側の変動成分とをバランスさせるようにその変動成分の大きさや波形を決定する。半導体集積回路の電源及びグランド側の変動に起因して半導体基板に与えられる変動成分が抑えられることにより、半導体基板を通して外部でコモンモード電流経路が形成されることを抑制することが可能になる。

(もっと読む)

半導体装置

【課題】従来技術において、制御回路に発生する電源ノイズを出力バッファに影響させないようにするには、出力バッファと制御回路の電源ラインを別々に設ける方法があった。しかし、この方法には、電源・グランドピン数の増加、給電ラインインダクタンスの増加といった問題があった。

【解決手段】本発明では、上記課題である(1)電源・グランドピン数増加と(2)給電ラインインダクタンスの増加を生じることなく、制御回路で問題となるノイズが出力バッファに回り込まないような技術を提供する。具体的な手法は、(A)制御回路用のオンチップバイパスキャパシタンスを設け、AC的に制御回路と出力バッファの給電経路を切り分ける方法、と(B)給電経路の電気パラメータノイズの振動モードが過減衰になるような設計(抵抗の挿入)をする方法がある。

(もっと読む)

回路装置、電子機器及び電源供給方法

【課題】断熱的回路動作と非断熱的回路動作を切り替え可能である回路装置、電子機器及び電源供給方法等を提供すること。

【解決手段】回路装置は、論理回路200と、電源回路100と、を含む。第1のモードでは、電源回路100は、非直流の電源電圧VPK、VMKを論理回路200に供給し、論理回路200は、その非直流の電源電圧VPK、VMKが供給されることで断熱的回路動作を行う。第2のモードでは、電源回路100は、直流の電源電圧VDD、VSSを論理回路200に供給し、論理回路200は、その直流の電源電圧VDD、VSSが供給されることで非断熱的回路動作を行う。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層を含むトランジスタと、酸化物半導体以外の半導体材料を用いて構成された論理回路と、を有し、前記トランジスタのソース電極またはドレイン電極の一方と、前記論理回路の少なくとも一の入力とは電気的に接続され、前記トランジスタを介して、前記論理回路に少なくとも一の入力信号が供給される半導体装置である。ここで、トランジスタのオフ電流は1×10−13A以下であるのが望ましい。

(もっと読む)

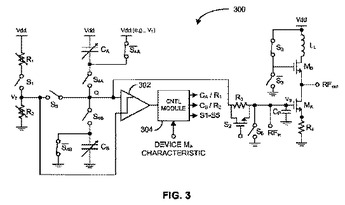

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

半導体記憶装置および昇圧回路

【課題】回路面積の削減しつつ、消費電流やピーク電流の増大を抑制することが可能な半導体記憶装置を提供する。

【解決手段】昇圧回路は、第1ないし第4の整流素子と、第1ないし第4のMOSトランジスタと、第1ないし第4のキャパシタと、スイッチ回路と、を備える。スイッチ回路は、第1のMOSトランジスタの他端と第3の整流素子の一端との間の第1の接続点、および、第2のMOSトランジスタの他端と第4の整流素子の一端との間の第2の接続点に接続された低レベル端子と、第3のMOSトランジスタの他端、および、第4のMOSトランジスタの他端に接続された高レベル端子と、を有し、低レベル端子の電圧または高レベル端子の電圧を切り換えて、出力端子に出力するスイッチ回路と、を含む。

(もっと読む)

スイッチトキャパシタ型積分器

【課題】待機電流を抑制することによって、低消費電力のスイッチトキャパシタ型積分器を実現する。

【解決手段】φ1において入力信号の電荷をサンプリングするサンプルキャパシタC1と、φ2においてサンプルキャパシタC1の電荷を仮想ノード4を介して累積する蓄積キャパシタC2と、蓄積キャパシタC2にサンプルキャパシタC1の電荷を供給する主トランジスタMP1,MN1と、主トランジスタMP1,MN1のゲート端子と仮想接地ノード4の間に挿入された校正キャパシタC3,C4と、φ1において校正キャパシタC3,C4に対して、仮想ノード4が基準電位Vcmにあるときの主トランジスタMP1,MN1のゲート・ソース間電圧が略閾値電圧となる電位差が生じるように電荷を供給する校正装置12と、を有する。

(もっと読む)

半導体集積回路

【課題】デジタル回路とアナログ回路とを混載して成る半導体集積回路において、前記デジタル回路によってメモリなどの外部負荷を駆動するにあたって、グランドバウンスによるアナログ回路への影響を抑えつつ、前記外部負荷がデジタル回路からの矩形波パルスを受信するにあたって、ON/OFF(「1」/「0」)判定のマージンを最大にする。

【解決手段】外部負荷3を駆動するメインドライバ回路7を、複数段のインバータINV1〜INV3を備える多段階電圧制御型のプリドライバ回路6を介して駆動するようにし、そのインバータINV1〜INV3の使用段数を切換え回路12で切換えられるようにする。そして、雑音検出回路13によって検出されるグランドバウンスのレベルが、小さいときにはインバータINV3のみを使用して前記矩形波パルスの鈍りを小さくし、大きいときにはインバータINV1〜INV3を使用して、グランドバウンスを抑える。

(もっと読む)

半導体集積回路およびその調整方法

【課題】一対の信号線に差動の信号を出力する差動出力駆動回路を備える半導体集積回路において、立ち上がり時間と立ち下がり時間とをそれぞれ独立に調整できるようにする。

【解決手段】一対の信号線4a,4bのそれぞれとGNDとの間に出力容量Ca,Cbを備えるとともに、それぞれの信号線4a,4bに直列に第1の抵抗R1a,R1bを介在し、かつ前記信号線4a,4bを第2の抵抗R2a,R2bによって電源電位にプルアップする。そして、該半導体集積回路1を基板に実装した後に測定された立ち上がり時間と立ち下がり時間とに応じて、抵抗値調整回路Aa,Abが、前記抵抗R1a,R2a;R1b,R2bの抵抗値をそれぞれ調整する。したがって、立ち上がり時間と立ち下がり時間とをそれぞれ独立に調整できるようになり、それらの対称性を維持しなければならないような規格に対しても対応可能となる。

(もっと読む)

レベルシフタ誤動作防止回路

【課題】本発明は、レベルシフタ誤動作防止回路に係り、レベルシフタの誤動作を、信号伝達の過大な遅延と消費電流の増大とを招くことなく防止することにある。

【解決手段】伝達すべき信号に応じて駆動されるN型トランジスタ30と、N型トランジスタ30の出力に応じて駆動されるP型トランジスタ32と、P型トランジスタ32を駆動するために設けられるプルアップ抵抗34と、を有する、基準電圧が互いに異なる2つの回路系の間で信号伝達を行うレベルシフタ16の誤動作を防止する回路において、2つの回路系の基準電圧が相対変位した際、N型トランジスタ30に存在する寄生容量36へプルアップ抵抗34を介して充電電流が供給される前に、その寄生容量36へ充電電流を供給する急速充電手段を設ける。

(もっと読む)

信号入出力回路

【課題】従来、データ受信するとき、データを判別する為、大小判定を行うコンパレータを備えており、このコンパレータには、動作時、入力信号の変化に追従するため、定常的に電流が流れている。このコンパレータに流れる定常的な電流が、大きな電力を消費しているという問題があった。

【解決手段】本発明は、一方のレベルを検知する第1検出回路と、他方のレベルを検知する第2検出回路とを有する受信部と、前記一方のレベルを出力するか、前記他方のレベルを出力するか、信号線から電気的に切り離したハイインピーダンス状態とするか、3つのうち何れかを1つの値を出力する三値出力器と有する送信部と、前記受信部と前記送信部を制御する制御回路と、を備え、前記制御回路は、受信の状態では、前記第1検出回路及び前記第2検出回路からの検知結果に応じて、入力される信号のレベルを判断し、送信の状態では、前記三値出力器からの出力値を制御することを特徴とする

(もっと読む)

半導体装置及び半導体装置の電源制御方法

【課題】1つの回路ブロックに対して設けた複数の電源スイッチを順次オンさせていく構成において、スイッチオンのタイミングを適切に制御可能な半導体装置を提供する。

【解決手段】半導体装置は、内部回路と、内部回路へ電流を供給する複数の並列な経路にそれぞれ設けられ、導通状態又は非導通状態に制御される複数の電源スイッチと、内部回路への電源を遮断する指示又は電源を供給する指示を行なう命令部と、内部回路に電源スイッチを介して供給される電流が定常状態であるか否かを検知して検知結果を出力する変動検知部と、命令部の電源供給指示に応答して、複数の電源スイッチを順次導通状態にして内部回路への電流供給量を増やしていく際に、複数の電源スイッチを導通させるタイミングを検知結果に応じて制御する論理回路とを含む。

(もっと読む)

半導体集積回路装置

【課題】

本発明は、外部電源の立ち上げ時にあっても安定した基準電位が得られる半導体集積回路装置を提供する。

【解決手段】

入力される第1の信号vbgrと第2の信号との電位差に応じて第3の信号を出力する第1の出力部を備える差動対と、第3の信号がゲートに入力されるトランジスタP3、トランジスタP3のドレインと接地電位との間に接続される抵抗R1,R2,VR、トランジスタP3のドレインから第4の信号vrefを出力する第2の出力部及び抵抗R1,R2,VRによって第4の信号vrefを分圧した第2の信号を出力する第3の出力部を備えるバイアス回路と、第1の出力部と第2の出力部との間に設けられ、差動対とバイアス回路に接続されるキャパシタC1と、少なくともキャパシタC1と差動対との間又はキャパシタC1とバイアス回路との接続を開閉する開閉部とを含む電位調整回路を備えることを特徴とする半導体集積回路装置。

(もっと読む)

半導体装置、及びその制御方法

【課題】発振回路と信号入出力回路とを切り替えて使用可能な半導体装置、及びその制御方法を提供することである。

【解決手段】本発明にかかる半導体装置は、発振素子1が接続可能な第1及び第2の外部接続端子2、3と、反転増幅器4と、反転増幅器の出力側と入力側との間に接続されたフィードバック抵抗5と、反転増幅器4の入力側に接続されたカップリング容量11に印加されるバイアスを安定化するバイアス安定化回路6と、第1の信号入出力部7と、第2の信号入出力部8と、を備える。半導体装置を発振回路として使用する場合は、反転増幅器4およびバイアス安定化回路6を動作状態とし、第1及び第2の信号入出力部7、8を停止状態とする。信号入出力回路として使用する場合は、反転増幅器4およびバイアス安定化回路6を停止状態とし、第1及び第2の信号入出力部7、8を動作状態とする。

(もっと読む)

161 - 180 / 589

[ Back to top ]