Fターム[5J056DD51]の内容

Fターム[5J056DD51]の下位に属するFターム

浮遊容量、寄生容量 (42)

Fターム[5J056DD51]に分類される特許

141 - 160 / 589

情報処理装置

【課題】 電源遮断機能を有するLSIにおいて、電源遮断をオンオフするときにリーク電流による電流が急激に変化すると電源線にノイズを生ずる。

【解決手段】 情報処理装置であって、回路ブロックと、前記回路ブロックに電源を供給するためのローカル電源線と、電源線と、前記電源線と前記ローカル電源線の間にそのソース―ドレイン経路が設けられる第1のトランジスタとを有し、前記第1のトランジスタは、第1の状態においてはオフ状態に制御され、第2の状態においてはオン状態に制御され、前記第1の状態から前記第2の状態に移行する際に、前記第1のトランジスタは、前記第1のトランジスタのソース―ドレイン経路を流れる電流の変化率が、所定の値を超えないように制御されることを特徴とする。

(もっと読む)

デジタル信号入力装置

【課題】動作が安定するとともに、後段に接続されるCMOSのLSIの安定な動作を実現するデジタル信号入力装置を提供する。

【解決手段】外部から入力された信号を増幅する増幅部と、前記増幅部で増幅された信号を波形整形する波形整形部と、オフセット電圧を保持するコンデンサと、前記波形整形部の出力をハイレベル状態に固定するように、前記コンデンサの充電と放電を制御して前記オフセット電圧を決定する制御部とを備える。

(もっと読む)

可変容量回路及びこれを備える発振回路

【課題】リーク電流を少なくできる可変容量回路及びこれを備える発振回路を提供する。

【解決手段】オフ時のNMOSトランジスタ12において、ソース電圧がPMOSトランジスタ11によって電源電圧VDDになるので、基板バイアス効果によってNMOSトランジスタ12の閾値電圧が高くなる。よって、オフ時のNMOSトランジスタ12のリーク電流が流れにくくなり、可変容量回路30のリーク電流が少なくなる。NMOSトランジスタ22も同様である。

(もっと読む)

半導体集積回路装置

【課題】入力容量および雑音を小さくした半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、入力信号が入力される入力端子と出力信号が出力される出力端子とを有する増幅器と、バイアス電流を生成する第1のトランジスタを有し、前記バイアス電流により動作し、前記出力信号を入力してフィードバック信号を前記入力端子に供給するフィードバック回路と、を備え、前記第1のトランジスタのゲートに、前記出力信号とは逆相の信号が入力されることを特徴とする。

(もっと読む)

半導体装置及び電子機器

【課題】消費電力を低減することができる半導体装置及びそれを用いた電子機器を提供す

ることを課題とする。

【解決手段】本発明の半導体装置は、高電位電源から第1の電位が供給され、低電位電源

から第2の電位が供給され、入力ノードに第1の信号が入力されると、出力ノードから第

2の信号を出力する。本発明の半導体装置は、第2の信号の電位差を、第1の電位と第2

の電位の電位差よりも小さくすることにより、配線の充電と放電に伴う消費電力を低減す

ることができる。

(もっと読む)

OFDM方式モデム

【課題】OFDM方式モデムにおいて、受信信号の最大値以上の電圧を発生する高電圧生成回路を設けることなく受信スイッチの動作の信頼性を確保できるようにする。

【解決手段】制御部2が変調および復調を行い回線接続部4を介して通信の回線10に接続されるOFDM方式モデムにおいて、受信通信路11に設けられ子機の受信インピーダンスを親機に対して子機を複数台接続したときの通信性能の低下を抑える高インピーダンスとする高インピーダンス受信部20、および受信通信路の開閉を行うフォトモスリレー21,211,212を備え、前記高インピーダンス受信部が前記フォトモスリレーの出力回路のMOS FETにながれる電流を許容電流以下とし、前記制御部が前記フォトモスリレーを開閉制御する。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの同期を保ったまま、再生クロックの適切なジッタ量と適切なバースト応答時間とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aの駆動力は、CDR回路のバースト応答時間が仕様の範囲内で最大となるように予め設定される。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

信号出力回路

【課題】より簡単な構成で、正弦波と同様に緩やかに変化する波形でスイッチング素子を制御できる信号出力回路を提供する。

【解決手段】NチャネルMOSFET8Tは、ゲートに与えられるPWM信号のレベル変化に応じてカレントミラー回路7の動作を制御し、カレントミラー回路7が動作すると電流源6が発生した電流がミラー電流として流れ、NチャネルMOSFET1のゲートを介してゲート−ソース間の容量成分に充電されている電荷を放電させる電流が流れる。カレントミラー回路7の動作が停止すると、カレントミラー回路5より電流源6を介して流れる電流が、NチャネルMOSFET1のゲートに充電電流として供給される。

(もっと読む)

レベルシフト回路及びそれを用いた発振器

【課題】 出力波形の割れや抜けを無くし、回路の誤動作が防止される低電圧動作のレベルシフト回路を提供する。

【解決手段】 レベルシフト回路は、電源端子VDDにソースを接続した第1のPMOSトランジスタP1と、接地端子GNDにソースを接続したNMOSトランジスタN1と、PMOSP1のドレインとNMOSN1のドレインとの接続点に接続された出力端子OUTと、NMOSN1のゲートに接続された入力端子INと、電源端子VDDにソースを接続し、PMOSP1のゲートにドレイン及びゲートを接続し、このドレインを第2の抵抗R2を介して接地端子GNDに接続した第2のPMOSトランジスタP2とを有し、PMOSP1及びP2は、カレントミラー回路を構成している。レベルシフト回路の出力波形の割れや抜けが無くなって誤動作を防止することが可能になる。

(もっと読む)

ソースドライバ及び液晶表示装置

【課題】液晶表示パネルを駆動するソースドライバのソースアンプの振幅差偏差を向上する。

【解決手段】液晶表示パネルを駆動するソースドライバ100が、画素データDINに対応する階調電圧を出力するD/Aコンバータ23と、階調電圧に対応する駆動電圧を出力するソースアンプ25とを備えている。ソースアンプ25は、第1及び第2NMOSトランジスタMN11,MN12を含むNMOS差動対と、第1及び第2PMOSトランジスタMP11,MP12を含むPMOS差動対と、NMOS差動対とPMOS差動対に流れる電流に応じて駆動電圧を出力する出力回路部(2,3)と、第1及び第2入力レベル変換回路4、5とを備えている。第1及び第2入力レベル変換回路4、5は、ソースアンプ25に入力される階調電圧と、ソースアンプ25の入力にフィードバックされる駆動電圧とに対し、駆動電圧の極性及び/又は階調電圧に応じて入力レベル変換を行う。

(もっと読む)

出力ドライバ回路

【課題】通信速度の高速化に加えて、消費電力の低減や、あるいは伝送波形品質の向上が図れる出力ドライバ回路を提供する。

【解決手段】例えば、正極および負極出力ノード(TXP,TXN)を電圧で駆動する電圧信号生成回路ブロックVSG_BKと、データ入力信号DIN_P,DIN_Nの遷移を受けてパルス信号を生成するパルス信号生成回路PGEN1,PGEN2と、当該パルス信号のパルス幅の期間でTXP,TXNを電流で駆動する電流信号生成回路ブロックISG_BKp1,ISG_BKn1を備える。電流信号生成回路ブロックは、TXP,TXNの寄生容量(Cp1,Cp2)を高速に充電すると共に、パルス幅に応じたプリエンファシスを行う。VSG_BKは、TXP,TXNにおける定常状態の電圧レベルを定めると共に、TXP,TXNをインピーダンスZ0で終端する。

(もっと読む)

電気光学装置、シフトレジスタ回路および半導体装置

【課題】ゲート線駆動回路の領域を効率よく利用できると共に、ゲート線選択信号の立ち上がり速度の低下(立ち上がり遅延)を防止できる電気光学装置、並びに、それに適した単一導電型のトランジスタで構成されたシフトレジスタ回路を提供する。

【解決手段】ゲート線駆動回路30は、複数のゲート線GLの奇数行を駆動する奇数ドライバ30aと、偶数行を駆動する偶数ドライバ30bとから成る。奇数および偶数ドライバ30a,30bの単位シフトレジスタSRの各々は、2行前の選択信号Gk-2を受け、その2水平期間遅れて自己の選択信号Gkを活性化させる。偶数ドライバ30bのスタートパルスSP1は、奇数ドライバ30aのスタートパルスSP2よりも1水平期間だけ位相が遅れている。

(もっと読む)

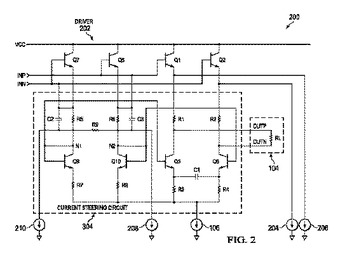

正確な電流ステアリングを備えた低電力高速差動ドライバ

BiCMOSプロセストランジスタを用いる混合又はハイブリッドモードドライバが、ドライバのプルアップ部の電圧に調和するプルダウン電流を生成するため電流ステアリング回路(電圧駆動差動対の代わりに)を有する。ドライバは、速度を速め、生成する出力同相電圧ゆらぎが一層小さい。回路200が、出力端子(OUTP、OUTN)を介して電流を供給して負荷104を駆動するドライバ202(これは、電圧モードと電流モードの組み合わせを用いる)を有する。ドライバ202は、NPNトランジスタ(Q1、Q2、Q7、Q8)、電流源(106、204、206)、及び電流ステアリング回路304を有する。電流ステアリング回路304は、フィードフォワード・レジスタ・キャパシタ(RC)ネットワーク(R5、R6、C2、C3)、入力NPNトランジスタ(Q9、Q10)、出力NPNトランジスタ(Q5、Q6)、電流源(208、210)、レジスタ(Rl〜R4及びR7〜R8)、及びバイパスキャパシタC1を有する。NPNトランジスタはPNPトランジスタで置き換えてもよい。  (もっと読む)

(もっと読む)

圧電アクチュエータ用のドライバ

【課題】複数の半導体デバイスを使用する電池駆動のドライバと同程度に効率的な圧電アクチュエータ用のシングルチップドライバを提供する。

【解決手段】圧電アクチュエータ用のドライバは、単一の半導体デバイスとしてパッケージされる、好ましくは単一の半導体ダイの上に形成されるパルス幅変調器33および出力増幅器34を含む。ドライバは、好ましくはプログラム可能な利得を有する出力増幅器34に電力を供給する第1の昇圧コンバータを含む。第1の昇圧コンバータのスイッチングトランジスタのゲートを駆動するための第2の増幅器は、第2の昇圧コンバータによって電力が供給される。圧電アクチュエータ22は、電池駆動の電子デバイスのキーボードまたはディスプレイに対して触覚フィードバックを提供する。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

レベルシフト回路

【課題】消費電力低下および速度向上が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路2は、第1入力端子11、第2入力端子12、第1出力端子21、第2出力端子22、第1PMOSトランジスタ31、第2PMOSトランジスタ32、第1NMOSトランジスタ41、第2NMOSトランジスタ42、第1ブートストラップ回路51および第2ブートストラップ回路52を備える。第1ブートストラップ回路51は、第1充電用スイッチ511,第1転送用スイッチ512,第1容量部513および第1インバータ回路514を含む。第2ブートストラップ回路52は、第2充電用スイッチ521,第2転送用スイッチ522,第2容量部523および第2インバータ回路524を含む。

(もっと読む)

半導体スイッチ及び無線機器

【課題】オフ歪みを低減した半導体スイッチを提供する。

【解決手段】負の第1の電位を生成する電圧生成回路と、外部から入力される端子切替信号に応じて前記第1の電位を変化させる電圧制御回路と、電源電圧または電源電圧よりも高い正の第2の電位と前記第1の電位とが供給され、前記端子切替信号を入力し前記端子切替信号に基づいて前記第1の電位及び前記第2の電位の少なくとも一方を出力する駆動回路と、SOI基板に設けられ、前記駆動回路の出力により端子間の接続を切り替えるスイッチ部と、を備えたことを特徴とする半導体スイッチが提供される。

(もっと読む)

電源回路

【課題】どの条件下でも一定のパルス幅で駆動する電源回路を提供する

【解決手段】電源回路10は、外部回路20と接続可能である。電源回路10は、一定の内部電圧を外部回路20に印加するフィードバック回路12と、パルスのパルス幅に応じた電荷を外部回路20に供給する電荷供給回路14と、外部回路20のオペレーションに対応するオペレーション状態に依存しない一定のパルスを電荷供給回路14に供給する電源制御回路16と、備える。

(もっと読む)

電源変動緩和回路を有する集積回路

【課題】

内部回路の一部の回路が起動または停止したときに内部電源電圧の変動が緩和されるようにした集積回路を提供する。

【解決手段】

電源が供給される集積回路において,電源が供給され内部電源を内部に供給する電源配線と,内部電源を供給される第1及び第2の内部回路と,第2の内部回路を非動作状態から動作状態に制御するイネーブル信号を第2の内部回路に供給するイネーブル信号供給回路とを有し,イネーブル信号供給回路は,イネーブル信号が非動作状態から動作状態に変化したときに動作状態の期間を間欠的に発生する調整イネーブル信号を生成し第2の内部回路に供給する。

(もっと読む)

141 - 160 / 589

[ Back to top ]