Fターム[5J056DD51]の内容

Fターム[5J056DD51]の下位に属するFターム

浮遊容量、寄生容量 (42)

Fターム[5J056DD51]に分類される特許

81 - 100 / 589

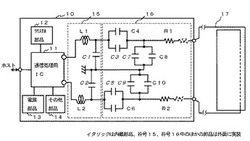

通信モジュール、リーダライタ

【課題】部品を内蔵できる配線板を有する通信モジュールであって、アンテナの特性に応じて整合の調整が可能な通信モジュールおよびこれを用いたリーダライタを提供すること。

【解決手段】配線板と、配線板に備えられた通信処理用ICと、通信処理用ICに電気的に接続されて配線板に備えられた、外部に設けられるアンテナとの整合をとる整合回路と、を具備し、整合回路が、キャパシタまたはインダクタを少なくとも含む受動素子回路網の回路であり、該受動素子回路網を構成する回路エレメントのうちの少なくともひとつが、配線板に内蔵された第1の受動素子部品と、配線板の面上に実装された、該第1の受動素子部品と同じ種の受動素子部品である第2の受動素子部品との並列接続または直列接続でできた回路エレメントである。

(もっと読む)

レベルシフト回路および半導体集積回路装置

【課題】回路面積を大きくせずに電源投入時の貫通電流を防止するレベルシフト回路を提供する。

【解決手段】アシスト回路(200)は、第1および第2スイッチ(N21、P21)と、電圧設定回路(300)とを備える。第1および第2スイッチ(N21、P21)は、第1インバータ(101)の出力ノード(BB)と、レベルシフタ(104)の入力ノード(AA)との間に挿入され、第1電源電圧(VDD1)に応答して回路を開閉する。第2電源電圧(VDD2)に基づいて設定電圧を生成する。第1電源電圧(VDD1)が供給される前に第2電源電圧(VDD2)が供給されたときに、レベルシフタ(104)の入力ノード(AA)の電圧を設定電圧に設定する。

(もっと読む)

半導体集積回路

【課題】

CMOS回路に中間電圧の入力信号が長時間連続して入力された場合にも貫通電流の発生を短時間にとどめることができる半導体集積回路を提供する。

【解決手段】

本発明の一実施態様に係る半導体集積回路は、入力端子と、出力端子と、ゲートが前記入力端子に接続されソースが高電位電源配線に接続された第1PMOSトランジスタ及びゲートが前記入力端子に接続されソースが低電位電源配線に接続された第1NMOSトランジスタを含み、当該第1PMOSトランジスタと当該第1NMOSトランジスタとが同時に導通しないように構成された第1CMOS回路と、入力端が前記第1CMOS回路に接続され出力端が前記出力端子に接続された第2CMOS回路と、この第2CMOS回路の出力端とと高電位電源配線及び高電位電源配線との間にそれぞれ配置された第2PMOSトランジスタと第2NMOSトランジスタと、を備える。

(もっと読む)

半導体装置

【課題】回路面積の増大を抑え、回路ブロックに電源供給するための複数の電源スイッチをオンするための時間間隔を適切に制御できるようにする。

【解決手段】回路ブロックに対する電源供給を管理する電源管理ユニット11と、回路ブロックA12への電源供給を制御する複数の電源スイッチPSWAと、回路ブロックAに供給する電源で動作し、その電位に応じた遅延を生成する遅延生成器13とを備え、電源スイッチは、電源供給を行うためにオン状態に制御されるときに、電源管理ユニット及び遅延生成器13の出力に基づいて回路ブロックAに供給される電源電位に応じた時間間隔で順次オン状態にするようにして、電源スイッチをオンするための時間間隔を回路ブロックAに供給される電源電位に応じて自動的に調整して電源供給を行う。

(もっと読む)

レベルシフト回路並びにレベルシフト回路を備えたインバータ装置

【課題】VM電位のdv/dtに起因する上アーム電力用スイッチング素子の誤動作を抑制できるレベルシフト回路並びにこれを備えたインバータ装置を提供する。

【解決手段】支持体Si基板上にBOX酸化膜を介しN型Si活性層を形成したSOI基板により構成し、分離酸化膜により分離されN型MOSFETを形成する第1のN型Si活性層、分離酸化膜により分離されP型拡散層による拡散抵抗を形成する第2のN型Si活性層、分離酸化膜により分離され上アーム制御電源の一端側に接続する第4のN型Si活性層から構成され、第1のN型Si活性層を形成する分離酸化膜と第4のN型Si活性層を形成する分離酸化膜は、隣接配置されるとともに、N型MOSFETのドレイン電極と拡散抵抗の第一の電極を接続し、拡散抵抗の第2の電極を上アーム制御電源の他端側に接続した。

(もっと読む)

差動信号出力装置、および、携帯機器

【課題】出力信号のスルーレートをより適切に制御することが可能な差動信号出力装置を提供する。

【解決手段】差動信号出力装置は、差動信号およびコモンモード信号を重畳して出力するための第1の送信端子および第2の送信端子を備える。差動信号出力装置は、データ信号に応じて前記差動信号を生成し前記第1の送信端子および前記第2の送信端子に出力する差動信号生成回路を備える。差動信号出力装置は、クロック信号に応じて前記コモンモード信号を生成し前記第1の送信端子および前記第2の送信端子に出力し、且つ、制御信号に応じて前記コモンモード信号のスルーレートを制御するコモンモード信号生成回路を備える。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

反転電圧出力回路

【課題】入力信号の変化に応じて直流電源の非接地電圧と接地電圧の間で反転する電圧を出力する回路であり、非接地端子に接続されている電源線に生じる電圧変動を抑制する。

【解決手段】電流制限素子14とスイッチング回路16が直列に接続されており、電流制限素子とスイッチング回路の中間点22の電圧を出力する。スイッチング回路の導通時にスイッチング回路を流れる電流が電流制限素子によって制限される。直流電源の非接地端子に接続されている電源線12に生じる電圧変動が抑制され、電源線12に接続されているアナログ回路等の動作が安定する。

(もっと読む)

電気信号の伝送回路、IC、プリント配線板、機器およびシステム

【課題】CMOS伝送回路において、レシーバの動作を不安定にしたり不要輻射を放出したりするリンギングの発生を抑制した電気信号の伝送回路を提供する。

【解決手段】本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、CMOSドライバのPMOS FET1と並列にアノード電極がドライバ出力端子につながれるように第1のダイオード6を接続し、CMOSドライバのNMOS FET2と並列にカソード電極がドライバ出力端子につながれるように第2のダイオード7を接続し、PMOS FET1のデバイストランスコンダクタンスと第1のダイオード6の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、NMOS FET2のデバイストランスコンダクタンスと第2のダイオード7の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

(もっと読む)

半導体装置およびその検査方法

【課題】本発明の実施形態は、高周波スイッチ回路の高周波特性の良否を簡便に判定することができる半導体装置およびその検査方法を提供する。

【解決手段】実施形態に係る半導体装置は、複数の高周波端子と、共通高周波端子と、の間の信号経路を、前記高周波端子と前記共通高周波端子との間に直列に設けられた複数のFETにより切り替える高周波スイッチ回路を有する半導体装置であって、前記共通高周波端子に接続された複数のFETを含む半導体スイッチと、前記半導体スイッチを介して前記共通高周波端子に接続された発振回路と、前記発振回路の出力を入力とする検波回路と、前記検波回路の出力端子と、を備える。

(もっと読む)

通信ドライバ回路

【課題】外乱ノイズが侵入した場合でも、通信線の信号レベルの変動をより確実に防止できる通信ドライバ回路を提供する。

【解決手段】通信ドライバ部11は、信号バス17にノイズが印加されると、信号レベル変化阻止回路14が、出力段がオープンコレクタタイプで構成される反転増幅回路13の出力信号がローレベル側に変化することを阻止するように動作する。

(もっと読む)

シフト・レジスタユニット、ゲート駆動回路及び表示装置

【課題】瞬時電流を低減し、シフト・レジスタユニットの消費電力を低減する。

【解決手段】本発明のシフト・レジスタユニットは、第1のクロック信号、第2のクロック信号、フレームスタート信号、高電圧信号および低電圧信号を入力する入力モジュールと、入力モジュールに接続され、複数の薄膜トランジスタを含み、第1のクロック信号、第2クロック信号およびフレームスタート信号に基づいてゲート駆動信号を生成し、薄膜トランジスタが形成した第1のノードのシフト・レジスタユニットの値を求める段階における電圧を電源信号のローレベルより低くなるよう制御し、薄膜トランジスタが形成した第2のノードをリセットするよう制御することを特徴とする。

(もっと読む)

入出力回路

【課題】昇圧した電圧でLCDを駆動するような場合でも、その共用の入出力端子から実用的な出力データ信号の出力が可能となる。

【解決手段】入出力回路100において、スリーステート出力バッファが出力データ信号とLCD駆動信号の両方に対してそれぞれ第1、第2出力バッファ106、108として設けられ、第1出力バッファ106を構成するPチャンネルMOSトランジスタ116のソース端子に電源電圧V1が供給され、且つ出力データ信号が出力として選択されていない状態でPチャンネルMOSトランジスタ116、118のバックゲート端子に電源電圧V1から昇圧された昇圧電圧V2が供給され、更に、第2出力バッファ108を構成するPチャンネルMOSトランジスタ116のソース端子とバックゲート端子とに昇圧電圧V2が供給される。

(もっと読む)

二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路

【課題】単位回路の、高速動作と未使用時(注を入れる)または定常時または待機時における消費電力の減少を両立させた二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路を提供することである。

【解決手段】四端子二重絶縁ゲート電界効果トランジスタからなるMOSトランジスタ回路において、前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートを入力端子とし、他方のゲートに抵抗の一方の端を接続し、ソースを第一の電源に接続し、ドレインを出力端子とすると供に負荷素子を通して第二の電源に接続し、前記抵抗の他端を一定電位の第三の電源に接続したことを特徴とする。

(もっと読む)

二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路

【課題】単位回路の、高速動作と未使用時(注を入れる)または定常時または待機時における消費電力の減少を両立させた二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路を提供することである。

【解決手段】四端子二重絶縁ゲート電界効果トランジスタからなるMOSトランジスタ回路において、前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートを入力端子とし、他方のゲートに抵抗の一方の端を接続し、ソースを第一の電源に接続し、ドレインを出力端子とすると供に負荷素子を通して第二の電源に接続し、前記抵抗の他端を一定電位の第三の電源に接続したことを特徴とする。

(もっと読む)

半導体集積回路およびその動作方法

【課題】伝送線路の特性インピーダンスと終端抵抗のインピーダンス整合を容易とする。

【解決手段】差動終端抵抗回路3は直列の第1と第2の素子Q1、Q2を含み、レプリカ抵抗回路4は直列の第3と第4の素子Q3、Q4を含み、制御電圧生成回路5は制御差動増幅器DA2と直列の制御素子Q8と第1と第2の電圧降下回路R7、8;R9とを含む。増幅器DA2の非反転入力と反転入力に、基準電圧Vrefと回路4の素子Q3、Q4のレプリカ抵抗電圧Vrcmがそれぞれ供給される。回路5の第1と第2のレプリカ抵抗制御電圧Vcont0、1は、回路4の素子Q3、Q4の制御入力にそれぞれ供給される。差動終端抵抗回路3の素子Q1、Q2は、第2のレプリカ抵抗制御電圧Vcont1と第2の電圧降下回路R9の電圧降下との合計電圧である差動終端抵抗制御電圧Vcont1.5に基づく制御出力電圧Voutによって制御される。

(もっと読む)

半導体集積回路およびその動作方法

【課題】多ビットの差動受信回路および差動終端抵抗を内蔵して、半導体チップ面積と消費電流の増大を軽減する。

【解決手段】複数の差動受信回路2A、B〜Nと複数の差動終端抵抗回路3A、B〜Nと複数の制御電圧供給回路6A、B〜Nに、レプリカ抵抗回路4と制御電圧生成回路5が共用される。複数の回路6A、B〜Nの各回路は、第1非反転入力と第1反転入力と出力を有する差動増幅器DA1を含む。第1供給回路6Aの第1差動増幅器の第1非反転入力と、第2供給回路6Bの第2差動増幅器の第1非反転入力と、第N供給回路6Nの第N差動増幅器の第1非反転入力とに、生成回路5から生成される差動終端抵抗制御電圧Vcont1.5が共通に供給される。第1差動増幅器の出力電圧VoutAと第2差動増幅器の力電圧VoutBと第N差動増幅器の出力電圧VoutNとは、第1と第2と第Nの差動終端抵抗回路3A、3B、3Nにそれぞれ供給される。

(もっと読む)

半導体装置

【課題】画素部の周辺領域にTFTを用いて駆動回路を基板上に同時形成するポリシリコンTFTによって回路を構成する際、TFTのしきい値によって出力振幅が減衰しない、表示装置の駆動回路を提供する。

【解決手段】信号出力端子に電気的に接続されるTFTのゲート電極に、容量手段に保持されている電圧を加えた電位が与えられることにより、当該TFTにおける振幅減衰が生ずることなく、信号出力端子からは正常な振幅の出力を得ることができる。

(もっと読む)

レベルシフト回路及び通信回路

【課題】 入力信号の電圧振幅の最大値と同電圧を供給する電源電圧の入力を必要とせず、異なる電圧振幅の入力信号が入力された場合でも動作可能であり、貫通電流による消費電力の増大を低減できるレベルシフト回路及び通信回路を提供する。

【解決手段】 出力信号の電圧振幅の最大値と同電圧を供給する第1電圧源と内部出力ノードN1の間に設けられた負荷抵抗回路R1と、入力信号の入力電圧を受け付け、制御ノードN2の電圧値を入力信号の電圧振幅の最大値に対応する制御電圧値に保持する電圧記憶回路11と、内部出力ノードN1と入力信号の入力ノードN3の間に設けられ、制御ノードN2の電圧と入力信号の電圧の電圧差に応じてON状態とOFF状態が切り替わるように構成され、入力信号の電圧値が電圧振幅の最大値の場合にOFF状態に、入力信号の電圧値が電圧振幅の最小値の場合にON状態になる第1スイッチング回路MN1と、を備える。

(もっと読む)

半導体集積回路

【課題】 内部回路の内部ノードが初期状態に設定されたことを精度よく検出し、内部回路が動作を開始するまでの復帰時間を短縮する。

【解決手段】 第1電源スイッチは、内部電源電圧を受けて動作する内部回路の動作を開始させるための第1電源オン信号の活性化中に、外部電源線を内部電源電圧が供給される内部電源線に接続する。第2電源スイッチは、第2電源オン信号の活性化中に、外部電源線を内部電源線に接続する。検知部は、第1電源スイッチのオンにより上昇する内部電源電圧を受けて動作する回路を含む。検知部は、内部電源電圧が第1電圧を超えることにより、内部回路の内部ノードが初期状態に設定されたことを検出したときに第2電源オン信号を活性化する。

(もっと読む)

81 - 100 / 589

[ Back to top ]