Fターム[5J056DD51]の内容

Fターム[5J056DD51]の下位に属するFターム

浮遊容量、寄生容量 (42)

Fターム[5J056DD51]に分類される特許

121 - 140 / 589

負荷容量の駆動回路

【課題】2相クロックによる負荷容量の駆動において、負荷容量間の電荷の再利用を行うと共に、出力クロックの高速化を容易にする。

【解決手段】第1クロック信号とその逆位相の第2クロック信号とに対してそれぞれ遅延した第1及び第2遅延クロック信号が生成される。インバータ回路は第1クロック信号と第1遅延クロック信号とが逆位相である逆転期間において第1クロック信号と逆位相の第1電位を第1出力ノードに生成し且つ第2クロック信号と逆位相の第2電位を第2出力ノードに生成し、第1クロック信号と第1遅延クロック信号とが同位相である一致期間において第1出力ノードと第2出力ノードとをハイインピーダンスとする。スイッチ回路は、逆転期間において第1出力ノードと第2出力ノードとを接続するオン状態とする。第1出力ノードと第2出力ノードとは、駆動対象回路の負荷容量に接続される。

(もっと読む)

トランスミッタ、インタフェイス装置、車載通信システム

【課題】電源電圧の変動に起因する入力信号と出力信号のデューティばらつきを抑制する。

【解決手段】トランスミッタ10は、一端から充電電圧Vaが引き出されるコンデンサ105と、コンデンサ105の充電電流I1を生成する第1定電流源103と、コンデンサ103の放電電流I2を生成する第2定電流源104と、送信入力信号INの論理レベル、及び、充電電圧Vaと基準電圧Vrefとの比較結果に基づいて、コンデンサ105の充放電制御を行う充放電制御部(101、102、106)と、充電電圧Vaに応じてスルーレートが設定され、出力側電源電圧V2に応じて信号振幅が設定される送信出力信号OUTを生成する出力段(109〜116)と、出力側電源電圧V2に依存して基準電圧Vrefを変動させる基準電圧生成部107と、基準電圧Vrefに依存して充電電流I1及び放電電流I2の各電流値を変動させる定電流制御部108と、を有する。

(もっと読む)

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

インバータ回路および表示装置

【課題】耐圧を上げることなく、低消費電力と高速化とを両立することの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】7Tr3Cで構成されるインバータ回路において、高電圧線LH側のトランジスタTr5,Tr2のゲート−ソース間に容量素子C1,C3が接続され、トランジスタTr5のゲートと入力端子INとの間に容量素子C1,C2が直列挿入されている。これにより、高電圧線LH側の電圧値を出力する際に、トランジスタTr7,Tr5,Tr2はオフ状態からゲート電圧およびソース電圧を上昇させ、ゲート−ソース間電圧を変化させながら順次オン状態となり、最終的に、トランジスタTr5がオフ状態となったときに、トランジスタTr2から出力電圧として高電圧線LH側の電圧値が出力される。

(もっと読む)

半導体集積回路装置

【課題】高い耐圧を有する入出力バッファ回路を備えた半導体集積回路装置を、中耐圧の素子のみで構成すること。

【解決手段】入出力バッファ回路を備えた半導体集積回路装置であって、入出力バッファ回路は、低スルーレートを実現するための帰還容量素子として、直列に接続された第1の容量素子及び第2の容量素子を有するとともに、第1の容量素子と第2の容量素子との間のノードの電位を入出力モードに応じて調整する電位調整回路を有する。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】3Tr2Cで構成されるインバータ回路において、トランジスタTr2のゲートと低電圧線L1との間、さらにトランジスタTr2のソースと低電圧線L1との間に、入力電圧Vinと低電圧線L1の電圧との電位差に応じてオンオフ動作するトランジスタTr1,Tr2が設けられている。トランジスタTr2のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr2のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

差動出力回路

【課題】出力信号の波形品質を改善する。

【解決手段】制御部(102)は、スイッチング素子(SW1,SW4)がオン状態であるとともにスイッチング素子(SW2,SW3)がオフ状態である第1の出力状態と、スイッチング素子(SW1,SW4)がオフ状態であるとともにスイッチング素子(SW2,SW3)がオン状態である第2の出力状態とを切り替える。また、制御部(102)は、第1の出力状態から第2の出力状態に切り替える場合には、スイッチング素子(SW2,SW3)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW1,SW4)をオン状態からオフ状態に切り替える。さらに、制御部(102)は、第2の出力状態から第1の出力状態に切り替える場合には、スイッチング素子(SW1,SW4)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW2,SW3)をオン状態からオフ状態に切り替える。

(もっと読む)

半導体装置

【課題】データストローブ信号のスルーレートを変更することなくデータストローブ信号のクロスポイントの電位を調整可能な半導体装置を提供する。

【解決手段】半導体装置は、外部クロックに基づき第1内部クロックを発生する発生回路と、第1内部クロックに基づき第2及び第3内部クロックを生成する分割回路であり第3内部クロックの立ち上がり及び立ち下がりの少なくとも一方のタイミングを調整するエッジ調整回路を含む分割回路と、エッジ調整回路にエッジ調整信号を供給する調整情報保持部と、第2内部クロックに応じて第1データストローブ信号を発生し第3内部クロックに応じて第1データストローブ信号と位相が異なる第2データストローブ信号を発生する出力回路を備え、エッジ調整回路はエッジ調整信号に応じて第3内部クロックの立ち上がり及び立ち下がりの少なくとも一方のタイミングを可変に調整する。

(もっと読む)

半導体装置及び情報処理システム

【課題】FETの閾値電圧の変動に起因するアンプのセンスマージンの低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、信号線(BL)に信号を出力する第1の回路(MC)と、FET(Q1、Q2、Q3)と、信号線に基準電位を与える第2の回路(Q5)を備えている。FETQ1はノードN1の電位と駆動信号SETの電位との間の電位差に応じてゲート容量が制御されるゲーテッドダイオードとして機能し、FETQ2は制御信号TGに応じて信号線とノードN1との間の接続を制御し、FETQ3はゲートがノードN1に接続されノードN1の信号電圧を増幅する。導通状態のFETQ2を非導通に制御した後、駆動信号SETの電位は第1の電位から第2の電位に遷移する。FETQ1の閾値電圧の変動量に対応して少なくとも第1の電位をオフセット制御し、FETQ3のセンス増幅時にFETQ1の閾値電圧の変動を補償する。

(もっと読む)

インバータ回路および表示装置

【課題】耐圧を上げることなく、消費電力を低減することの可能なインバータ回路およびそれを備えた表示装置を提供する。

【解決手段】7Tr2Cで構成されるインバータ回路において、容量素子C1がトランジスタTr5のソースに接続されるとともに、トランジスタTr4を介してトランジスタTr7のゲートに接続されている。トランジスタTr7のソースには、トランジスタTr2のゲートが接続されている。これにより、入力端子INに立下り電圧が入力され、トランジスタTr1,Tr3,Tr6がオフしたときに、Vddが充電された容量素子C1によって、トランジスタTr7のゲートがVSS+Vth7以上の電圧にチャージされ、トランジスタTr7がオンし、さらにトランジスタTr2がオンする。

(もっと読む)

半導体集積回路

【課題】 スイッチの信頼性を低下することなく、内部電圧線を所定の電圧に迅速に設定し、半導体集積回路の動作速度を向上する。

【解決手段】 半導体集積回路は、第1高電圧が供給される第1高電圧線を内部電圧線に接続するために第1スイッチ制御信号の活性化に応じてオンする第1スイッチと、第1高電圧を生成するために第1電圧生成信号の活性化に応じて動作する第1電圧生成回路と、第1電圧生成信号の活性化に応じて動作し、第1高電圧と内部電圧線の電圧とを比較し、第1高電圧と内部電圧線の電圧との差が所定値になったときに第1スイッチ制御信号を活性化するレベル比較器とを備えている。第1スイッチの両端に掛かる電圧を比較し、電圧差が小さくなったときに第1スイッチをオンすることで、第1スイッチの信頼性を低下することなく、内部電圧線を所定の電圧に迅速に設定できる。

(もっと読む)

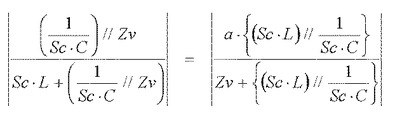

スイッチング回路のノイズ低減装置

【課題】ノイズ低減効果が大きく、小型化が可能なスイッチング回路のノイズ低減装置を提供する。

【解決手段】第1のスイッチングドライバの入力端に入力されるパルス信号と逆位相のパルス信号に基づいて動作する第2のスイッチングドライバと、一端が第2のスイッチングドライバの出力端に接続されるとともに他端がスイッチング回路の出力端子と接続されるインピーダンス素子とを具備し、インピーダンス素子のインピーダンス値Zvと、第1のコイルのインダクタンス値Lと、コンデンサの静電容量値Cと、第1及び第2のスイッチングドライバのスイッチング周波数fcとが、aを0以外の任意の定数として、(数3)の関係を満たす。 (もっと読む)

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、トランジスタの閾値電圧のばらつきに起因する出力電圧のばらつきを抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】6Tr3Cで構成されるインバータ回路において、入力端子IN2に、入力端子IN1に入力されるパルス信号の位相よりも進んだ位相のパルス信号が印加される。これにより、入力端子IN1の電圧がハイからローに変化する際に、トランジスタT5のゲート−ソース間電圧から、トランジスタT5の閾値電圧の影響が取り除かれるので、その後にトランジスタT5がオンしてトランジスタT5に電流が流れたときに、その電流値Idsからも、トランジスタT5の閾値電圧の影響が取り除かれる。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr2Cで構成されるインバータ回路において、容量素子C1がトランジスタTr5のソースに接続されるとともに、トランジスタTr4を介してトランジスタTr2のソースに接続されている。これにより、入力端子INに立下り電圧が入力され、トランジスタTr1,Tr3がオフしたときに、Vdd2が充電された容量素子C1によって、トランジスタTr2のゲートがVSS+Vth2以上の電圧にチャージされ、トランジスタTr2がオンする。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr2Cで構成されるインバータ回路において、トランジスタTr2のソースと低電圧線LLとの間、トランジスタTr5のゲートと低電圧線LLとの間、さらにトランジスタTr2のゲートと低電圧線LLとの間に、入力電圧Vinと低電圧線LLの電圧VLとの電位差に応じてオンオフ動作するトランジスタTr1,Tr3,Tr4が設けられている。トランジスタTr5のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr5のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

受信回路、受信方法及び受信回路を備える通信システム

【課題】従来の受信回路では、耐ノイズ性が低い問題があった。

【解決手段】本発明の受信回路の一態様は、送信回路Txとは異なる電源系において動作する受信回路Rxであって、送信回路Rxが絶縁素子ISOを介して出力する送信信号に基づき生成される受信信号Aの信号レベルの変化に応じて受信データDrx1の論理レベルを切り替える状態保持回路10と、受信データDrx1の論理レベルが切り替わる第1のタイミングから予め設定された第1の期間が経過するまでの期間において、状態保持回路10に受信データDrx1の論理レベルの保持を指示するホールド信号Dを生成する状態保持制御回路20と、を有する。

(もっと読む)

電子回路

【課題】

内部電源電圧を遮断するパワーダウンモードへの移行を誤動作無く確実に実行するパワーダウンモードの移行シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧から降圧してシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する第1の内部回路30と、電源電圧を供給されて動作する入出力回路24と、第1の内部回路30からの信号を入力し、電源電圧の電圧レベルに変換するレベルシフタ23と、システム電圧発生回路10を制御する制御回路40とを備え、制御回路40は起動信号P4を入力し、この起動信号に所定の遅延時間を与えた短絡制御信号P5を出力する遅延回路100を有し、起動信号はレベルシフタ23を非活性又は活性として制御し、短絡制御信号はシステム電圧発生回路10を停止状態又は動作状態として制御する構成とした。

(もっと読む)

出力バッファ回路およびそれを用いたドライバ回路

【課題】 入出力信号が変化する際の過渡期間に出力バッファを構成するトランジスタへのバイアス電流を一時的に増強することで、バッファ回路全体の定常的なバイアス電流を抑制しつつ、高スルーレートが得られるバッファ回路を提供する。

【解決手段】 ドライバ回路200は信号レベル発生回路100により発生した信号SGOを出力バッファ回路110を駆動する回路150(プリバッファ回路)を介し、出力バッファ回路110により伝送線路120を駆動することで測定対象回路DUT140に伝える。プリバッファ回路150とこれを模擬したレプリカバッファ回路160とを互いに並列に備え、信号SGOが変化する際の入出力新信号の過渡期間において、レプリカバッファ回路160の出力電流に基づいて出力バッファ回路110の出力段トランジスタQN12、QP22の入力バイアス電流を一時的に増強する。

(もっと読む)

レベルシフト回路及びデータドライバ及び表示装置

【課題】低振幅のデジタル入力信号を高振幅の電圧信号に高速にレベル変換可能としレベル変換信号の安定な保持を可能とし、構成を簡易化する。

【解決手段】第1のトランジスタM1のゲートと、第2及び第3のトランジスタM2、M3の一方のトランジスタのゲートには、第1の制御信号S1が共通に入力され、第2及び第3のトランジスタM2、M3の他方のトランジスタのゲートには、第1の電源と第2の電源の電源振幅よりも低振幅の入力信号INが入力される入力端子1に接続される。第2の制御信号S2によりオン又はオフに制御されるクロックドインバータ10と、第1の出力端子3に入力が接続されたインバータ20と、第1のノード2とインバータ20の出力との間に接続され、第3の制御信号S3によりオン又はオフに制御されるスイッチSW1を備えている。

(もっと読む)

回路装置、電子機器及び電源回路

【課題】実装面積を削減できる回路装置、電子機器及び電源回路等を提供すること。

【解決手段】回路装置は、共振回路を有する電源回路と、論理回路と、を含む。共振回路は、第1のコイルL1と、第1のコイルL1とコア部を共有する第2のコイルL2と、を有する。論理回路は、共振回路により生成された電源電圧VP、VMが供給されることで断熱的回路動作を行う。

(もっと読む)

121 - 140 / 589

[ Back to top ]