Fターム[5J056GG09]の内容

論理回路 (30,215) | 制御対象、制御態様 (2,427) | 出力電圧を制御するもの (1,446) | 段階的に制御するもの (1,382) | あるノードの電位を利用するもの (888)

Fターム[5J056GG09]に分類される特許

81 - 100 / 888

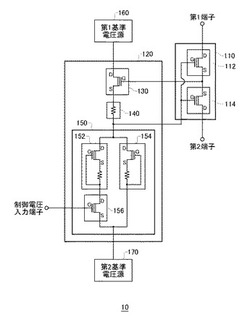

スイッチ装置および試験装置

【課題】入力電圧範囲の大きな半導体スイッチ装置を提供する。

【解決手段】外部から入力される制御電圧に応じて第1端子および第2端子間を電気的に接続または切断するスイッチ装置であって、第1端子および第2端子の間にソースおよびドレインが接続され、当該スイッチ装置に入力される入力電圧とゲート電圧との差に応じてオンまたはオフとなるメインスイッチと、制御電圧および入力電圧に応じて第1基準電圧を電圧シフトさせた駆動電圧をメインスイッチのゲートに供給する制御部と、を備えるスイッチ装置を提供する。

(もっと読む)

レベルシフト回路及びそれを備えた駆動回路

【課題】容易に低振幅信号を高振幅信号に変換可能なレベルシフト回路を提供すること。

【解決手段】本発明にかかるレベルシフト回路は、電源端子E1と出力ノード3、4間にそれぞれ接続され低振幅の入力信号を制御端子にそれぞれ受けるNMOトランジスタM1、M2と、電源端子E2と出力ノード3、4間にそれぞれ接続されたPMOSトランジスタM3、M4と、PMOSトランジスタM3のゲートと出力ノード4との間に接続され、ゲートが出力ノード3に接続されたPMOSトランジスタM5と、PMOSトランジスタM4のゲートと出力ノード3との間に接続され、ゲートが出力ノード4に接続されたPMOSトランジスタM6と、PMOSトランジスタM3をオフする方向にそのゲート電圧を変化させる作用を有する負荷素子11と、PMOSトランジスタM4をオフする方向にそのゲート電圧を変化させる作用を有する負荷素子12と、を備える。

(もっと読む)

レベルシフト回路及び半導体装置

【課題】電源電圧が低電圧化したときの動作不良の発生を抑制することのできるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、第1の高電位電圧VLを信号レベルとする入力信号Siに応じて相補的にスイッチング制御されるNチャネルMOSトランジスタTN1,TN2を有するレベル変換部10を備える。レベルシフト回路1は、第1の高電位電圧VLの低下を検出したことを示す検出信号DSを生成する検出部20と、検出信号DSに応じて、トランジスタTN1,TN2の閾値電圧が低くなるようにトランジスタTN1,TN2のボディバイアスVbbを制御する制御部30とを備える。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

半導体装置

【課題】立ち上がり時間と立ち下がり時間の差を解消しつつ、動作に伴う貫通電流の発生が防止されたレベルシフト回路を提供する。

【解決手段】互いに同じ回路構成を有するレベルシフト回路LV1,LV2と、レベルシフト回路LV1,LV2に相補の入力信号をそれぞれ供給する入力回路と、レベルシフト回路LV1,LV2から出力される相補の出力信号を同相に変換した後に短絡する出力回路とを備える。本発明によれば、同じ回路構成を有する2つのレベルシフト回路LV1,LV2を用いるとともに、これらレベルシフト回路LV1,LV2から出力される相補の出力信号を同相に変換した後に短絡していることから、レベルシフト回路LV1,LV2の動作速度差による貫通電流の発生がほとんど生じない。

(もっと読む)

信号入力回路

【課題】信号入力端子のプルアップ機能を有したまま、信号入力端子に入力する信号電圧が高電位電源端子の電圧を超えるときがあっても、上記したような問題が生じないようにした信号入力回路を提供する。

【解決手段】エンハンスメント型NMOSトランジスタMN1のバックゲートを低電位電源端子2に接続し、ドレインとゲートを高電位電源端子1に接続し、ソースを信号入力端子3に接続する。エンハンスメント型NMOSトランジスタMN1のオン抵抗を、信号入力端子3に接続される前段回路のドライバの“L”レベル電圧出力時の出力インピーダンスよりも高い値に設定する。

(もっと読む)

通信ドライバ回路

【課題】外乱ノイズが侵入した場合でも、通信線の信号レベルの変動をより確実に防止できる通信ドライバ回路を提供する。

【解決手段】通信ドライバ部11は、信号バス17にノイズが印加されると、信号レベル変化阻止回路14が、出力段がオープンコレクタタイプで構成される反転増幅回路13の出力信号がローレベル側に変化することを阻止するように動作する。

(もっと読む)

半導体スイッチ

【課題】端子切替時の応答特性を改善した半導体スイッチを提供する。

【解決手段】電源回路部は、正の電源電位よりも高い第1の電位と、負の第2の電位と、を生成する。駆動回路部は、前記電源回路部に接続され、端子切替信号に応じて前記第1の電位をハイレベルとし前記第2の電位をローレベルとする制御信号を出力する。スイッチ部は、制御信号を入力して端子間の接続を切り替える。前記駆動回路部は、第1と、第2のレベルシフタと、第1の回路と、を有する。前記第2のレベルシフタは、前記第1のレベルシフタの出力電位に応じて互いに排他的にオンする第2のハイサイドスイッチと第2のローサイドスイッチとを有し、前記制御信号を出力する。前記第1の回路は、前記端子切替信号に応じて、前記制御信号の電位の変化よりも前に前記第2のローサイドスイッチに前記電源電位を供給し、または前記ハイサイドスイッチに前記接地電位を供給する。

(もっと読む)

半導体集積回路及び半導体集積回路の電源制御方法

【課題】製造プロセス条件の変動に関わらず短い電源立ち上げ時間を確保することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第1の電源線と第2の電源線との間に並列に配置された複数の電源スイッチと、複数の電源スイッチを設定時間間隔で順次導通させる駆動回路と、第2の電源線と第3の電源線との間に配置される内部回路と、第2の電源線と第3の電源線との間の電圧が上昇して所定値に到達すると検知信号をアサートする昇圧検知回路と、検知信号のアサート時において導通状態にある複数の電源スイッチの数に応じて設定時間間隔を変化させる制御回路とを含む。

(もっと読む)

電圧発生装置

【課題】低電源電圧状態で、ビットラインプリチャージ電圧又はセルプレート電圧を安定的に駆動し、待機電流IDD2P及び動作電流を最小化すること。

【解決手段】電源電圧のハーフレベルの基準電圧を利用し、異なるレベルのバイアス信号を生成するバイアス信号生成手段と、出力端の電圧レベルに応答してプルダウン駆動信号を生成する駆動信号生成手段と、駆動信号に応答して出力端を駆動する電圧駆動手段と、出力端の電圧レベルに応じてプルアップ駆動信号/プルダウン駆動信号を生成する駆動信号生成手段と、前記プルアップ駆動信号/プルダウン駆動信号に応答して前記出力端をプルアップ駆動/プルダウン駆動するプルアップPMOSトランジスタ/プルダウンNMOSトランジスタと、第1多重化手段と、第2多重化手段とを備える半導体メモリ素子の電圧発生装置。

(もっと読む)

レベル変換器、それを含むシステムオンチップ、及びそれを含むマルチメディア装置

【課題】向上された信頼性を有するレベル変換器、それを含むシステムオンチップ、及びそれを含むマルチメディア装置が提供される。

【解決手段】本発明のレベル変換器は、入力ノードを通じて受信される第1電圧ドメインの入力クロックに応じて第2電圧ドメインの出力クロックを発生する第1及び第2電圧変換回路を含み、第1及び第2電圧変換回路は同一の構造を有し、入力ノード及び出力ノードの間に並列に連結される。

(もっと読む)

レベルシフト回路及びその方法

【課題】レベルシフト回路及びその方法の提供。

【解決手段】本発明のレベルシフト回路及びその方法は、レベルシフト回路のラッチ装置と電圧源の間に限流回路を接続して、前記ラッチ装置の駆動電流が設定値を超えないように制限する。これにより、レベルシフト回路を変換する時の消耗電流を減らし、通路の短いトランジスタを使用したラッチ装置を実現し、レベルシフト回路面積を縮小する。前記設定値は調節可能とし、レベルシフト回路の出力駆動能力を調整することにより、前記レベルシフト回路の変換速度を加速させることができる。

(もっと読む)

レベルシフト回路及び通信回路

【課題】 入力信号の電圧振幅の最大値と同電圧を供給する電源電圧の入力を必要とせず、異なる電圧振幅の入力信号が入力された場合でも動作可能であり、貫通電流による消費電力の増大を低減できるレベルシフト回路及び通信回路を提供する。

【解決手段】 出力信号の電圧振幅の最大値と同電圧を供給する第1電圧源と内部出力ノードN1の間に設けられた負荷抵抗回路R1と、入力信号の入力電圧を受け付け、制御ノードN2の電圧値を入力信号の電圧振幅の最大値に対応する制御電圧値に保持する電圧記憶回路11と、内部出力ノードN1と入力信号の入力ノードN3の間に設けられ、制御ノードN2の電圧と入力信号の電圧の電圧差に応じてON状態とOFF状態が切り替わるように構成され、入力信号の電圧値が電圧振幅の最大値の場合にOFF状態に、入力信号の電圧値が電圧振幅の最小値の場合にON状態になる第1スイッチング回路MN1と、を備える。

(もっと読む)

レベル変換回路および表示装置、並びに電子機器

【課題】回路構成の複雑化、消費電流の増加、特性低下を防止することができ、レイアウト面積の削減を図れるレベル変換回路および表示装置、並びに電子機器を提供する。

【解決手段】バイアス部12は、第5のNMOSトランジスタNT15と、抵抗素子R11を含む降圧部16と、電圧源15に接続された電流源I11と、を含み、第5のNMOSトランジスタNT15のソースが第1電圧源14に接続され、ドレインが抵抗素子R11の一端に接続され、抵抗素子R11の他端が電流源I11に接続され、第5のNMOSトランジスタNT15のゲートが抵抗素子R11の他端側に接続され、第1電圧から第1および第2のNMOSトランジスタNT11,NT12のしきい電圧分高く、または第1電圧より高くこのしきい値電圧より低いバイアス電圧を抵抗素子の一端側に生成し、レベル変換部11の第1および第2のNMOSトランジスタNT11,NT12のゲートに供給する。

(もっと読む)

論理否定型電子回路

【課題】 ブートストラップ機能を有する電子回路に関し、出力電圧の降下を防止して、論理否定型電子回路の誤作動を阻止し、また、長い作動時間を確保する。

【解決手段】 負荷トランジスタ、駆動トランジスタ部、充電用トランジスタ並びにブートストラップ容量を具備し、入力電圧の位相を出力部から反転せしめて出力する論理否定型電子回路について、入力される電圧の位相を反転させて出力するインバータ回路をさらに設け、このインバータ回路の入力節点を前記出力部に、出力節点を前記充電用トランジスタのゲートにそれぞれ接続する。

(もっと読む)

論理否定型電子回路

【課題】 ブートストラップ機能を有する電子回路に関し、出力電圧の降下を防止して、論理否定型電子回路の誤作動を阻止し、また、長い作動時間を確保する。

【解決手段】 負荷トランジスタ、駆動トランジスタ部、充電用トランジスタ並びにブートストラップ容量を具備し、入力電圧の位相を出力部から反転せしめて出力する論理否定型電子回路について、前記充電用トランジスタのソース−ドレイン間の電圧が電源の電圧Vddと同値の電圧であるときに、これらソース−ドレイン間を流れる電流が1×10−9A以下となる範囲の電圧をこの充電用トランジスタのゲートに印加する定電圧印加手段を接続する。

(もっと読む)

半導体装置

【課題】基準電圧生成回路に電源電圧が投入されてから安定平衡状態に達するまでの時間を短縮する回路を提供することを課題とする。

【解決手段】スタートアップ回路から基準電圧生成回路に入力される初期電圧を、基準電圧生成回路の安定平衡状態における内部電圧に近い電圧とすればよい。また、このような電圧を電源が遮断された状態でも保持しておくことができ、且つ起動時に出力することのできるスタートアップ回路とすればよい。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】複数の基準電位を要する半導体装置、及び半導体装置の駆動において、より消費電力を軽減する。

【解決手段】電源線に直列に接続された複数の抵抗素子により、電源線に供給された電位を抵抗分割し、電源線と電気的に接続するスイッチトランジスタを介して所望の分割された電位を出力する電位分割回路を有する半導体装置であり、スイッチトランジスタのドレイン端子は出力側の回路に設けられたトランジスタのゲート端子(又は容量素子の一方の端子)と電気的に接続しノードを構成する。

(もっと読む)

半導体集積回路

【課題】 電源ノイズを緩和しながら、内部回路が動作を開始するまでの時間を短縮する。

【解決手段】 内部回路は、基板電圧が供給されるトランジスタを含み、内部電源電圧を受けて動作する。電源スイッチは、内部回路を動作させるための電源オン信号の活性化中に外部電源線を内部電源線に接続する。基板電圧制御回路は、電源オン信号の活性化により上昇する内部電源電圧が目標電圧を超えたときに、基板電圧を第1電圧から第2電圧に変更する。第1電圧を基板電圧として受けているトランジスタのソース・ドレイン間電流は、第2電圧を基板電圧として受けているトランジスタのソース・ドレイン間電流より少ない。このため、電源スイッチがオンした後、内部電源電圧が低い期間にトランジスタのソース・ドレイン間電流を少なくでき、内部回路を流れる貫通電流を少なくできる。

(もっと読む)

ドライバアンプ回路および通信システム

【課題】バイアス調整回路やプリドライバ回路が不要で、しかも出力波形の波形歪みを低減することが可能なドライバアンプ回路および通信システムを提供する。

【解決手段】スイッチングトランジスタM11〜M14を駆動するゲート電圧を均一にするため、スイッチングトランジスタM11〜M14を電源およびGND側に配置し、さらに、スイッチングトランジスタM11〜M14の駆動振幅を安定させるために、各スイッチングトランジスタM11のドレインと出力ノードND11、ND12間にそれぞれ第1から第4の抵抗素子R11〜R14を接続している。

(もっと読む)

81 - 100 / 888

[ Back to top ]