Fターム[5J056GG09]の内容

論理回路 (30,215) | 制御対象、制御態様 (2,427) | 出力電圧を制御するもの (1,446) | 段階的に制御するもの (1,382) | あるノードの電位を利用するもの (888)

Fターム[5J056GG09]に分類される特許

61 - 80 / 888

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

半導体装置

【課題】可変抵抗回路の抵抗値の調整可能範囲が大きな半導体装置を提供する。

【解決手段】この半導体装置は、複数組の抵抗素子RA,RBおよび複数組のトランジスタP,Qを含む出力バッファDOBと、複数のレプリカ回路RPと、複数組の演算増幅器AP,ANとを備え、出力バッファDOBの出力インピーダンスZp,Znが所定値になるように、複数組のトランジスタP,Qのドレイン電流を調整する。したがって、製造プロセスなどの変動によって抵抗素子RA,RBの抵抗値が大きく変動した場合でも、出力インピーダンスZp,Znを所定値に設定できる。

(もっと読む)

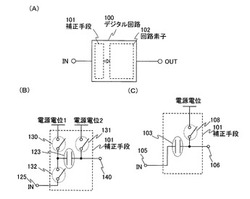

バッファ回路

【課題】入力信号の交流成分の歪み等の影響をなるべく受けることなく、本来のデューティー比(目標デューティー比)で出力信号を出力することのできるバッファ回路を提供する。

【解決手段】バッファ回路10は、デューティー比検出部16と直流成分生成部17とから構成される負帰還回路部によって、入力信号増幅部15の入出力間で出力信号SOのデューティー比に応じた直流成分の信号を帰還させている。つまり、バッファ回路10は、出力信号SOのデューティー比に応じて、入力信号SI´の直流成分をさらに小さくしたり、大きくしたりする。これにより、バッファ回路10は、出力信号SOのデューティー比を目的デューティー比に変更した上で、その出力信号SOを出力することができる。

(もっと読む)

出力回路

【課題】負荷容量の要求仕様に適合する出力回路を提供する。

【解決手段】出力回路1は,第1の電源VDDと出力トランジスタP1のソースとの間に設けられた電流調整用トランジスタP2と,出力信号EXが,第2の電位から第1の電位に変化する途中で,電流調整用トランジスタP2の電流を増大させるよう,出力信号EXの電位に応じて,電流調整用トランジスタP2のゲートを制御する電流調整回路11とを有する。

(もっと読む)

半導体装置

【課題】切り替えスイッチのオンオフに伴うノイズがバイアスラインに重畳するのを防ぐ。

【解決手段】バイアス電流が流れるバイアスラインVLと、バイアス電流の量を制御信号DDに基づいて切り替える切り替えスイッチ70と、制御信号DDが供給される制御ラインとバイアスラインVLとの間の寄生容量を介して制御信号DDの変化時に生じるバイアスラインVLの電位変動を相殺する相殺回路91〜93とを備える。本発明によれば、切り替えスイッチ70のオンオフに伴ってバイアスラインVLに生じるノイズを相殺することが可能となる。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路の出力信号のノイズを低減する。

【解決手段】一つの実施形態によれば、レベルシフト回路は第一及び第二のレベル変換部が設けられる。第一の出力加速回路は、レベルシフトされた第一の入力信号の立ち上りエッジを制御し、信号変化部分が多段階に分割された第一の信号を生成する。第二の出力加速回路は、レベルシフトされた第一の入力信号の立ち下りエッジを制御し、信号変化部分が多段階に分割された第二の信号を生成する。第三の出力加速回路は、レベルシフトされた第二の入力信号の立ち上りエッジを制御し、信号変化部分が多段階に分割された第三の信号を生成する。第四の出力加速回路は、レベルシフトされた第二の入力信号の立ち下りエッジを制御し、信号変化部分が多段階に分割された第四の信号を生成する。

(もっと読む)

送信ドライバ回路

【課題】信号の伝送速度が速い差動通信においても、コモンモード電圧の発生を適切に抑制できる送信ドライバ回路を提供する。

【解決手段】レベルホールド回路3は、通信信号出力部2が差動信号の電圧レベルを変化させる際に伝送線路5に発生するコモンモード電圧の変化を検出し、その検出レベルをレベルホールドする。そして、信号処理回路4は、前記検出レベルを上限基準値及び下限基準値と比較し、検出レベルが上限基準値を上回るか又は下限基準値を下回ると、次回の信号送信時に発生するコモンモード電圧を低減するように、通信信号出力部2による電圧の出力状態を調整する。

(もっと読む)

演算およびスリープ・モード中のデータ格納回路並びに方法

【課題】スリープ・モード中に信号を格納するための回路を提供する。

【解決手段】スリープ信号を受け取るスリープ信号入力と、クロック信号を受け取るクロック信号入力と、クロック信号でクロックされる複数のラッチと、クロック信号でクロックされるトライステート素子であって、トライステート素子は1つの入力に、少なくとも1つの格納ラッチが接続され、格納ラッチは複数のラッチの1つであり、トライステート素子は格納ラッチの入力を、予め定められたクロック信号値に応答して選択的に分離するトライステート素子とを含み、回路への電源供給が、スリープ信号に応答して、回路の少なくとも1部の電圧差が低減されて回路の部分の電源が遮断され、格納ラッチに掛かる電圧差が維持され、トライステート素子で受け取られるクロック信号が予め定められた値に保持されて、格納ラッチの入力が分離される。

(もっと読む)

出力回路

【課題】スキューの少ない出力信号を出力する回路の実現。

【解決手段】差動入力信号INN,INPを受けて、差動駆動信号を出力する駆動回路BF1,BF2;BF3,BF4と、共通の定電流源12に接続され、差動駆動信号に応じて逆相のスイッチ動作を行う2個のトランジスタMN1,MN2を有する差動出力部と、駆動回路の2個の駆動部の電源15,16の電位を、定電流源12と2個のトランジスタの接続ノードTailの電位に応じた電位にするレベル調整回路AMP1,AMP2と、を有する出力回路。

(もっと読む)

出力回路、システム、及び出力回路の制御方法

【課題】信号波形の変異を抑制すること。

【解決手段】第1のトランジスタT1は、信号S3に応答してオンオフし、オンしたトランジスタT1は外部端子P2に接続された伝送路27をプルダウンする。伝送路27のレベルは、トランジスタT1のゲートと外部端子P2とをACカップリングするキャパシタC1により、キャパシタC1の容量値に応じた傾きで立ち下がる。プルダウン回路44は、外部端子P2の電位に応じて、トランジスタT1のゲート電圧をプルダウンする。

(もっと読む)

定電圧回路とその半導体装置

【課題】 ツェナーダイオードと同等の動作を行える回路ないしは半導体装置を提供することを目的とする。

【解決手段】 実施形態の基準電圧発生回路は、第1のFETと、第2のFETと、一方を電源に接続し他方を前記第1のFETのドレインに接続した第1の抵抗と、前記第1のFETのドレイン−ゲート間に接続した第2の抵抗とを有し、前記第2のFETのゲート−ソース間を接続し、前記第2のFETのドレインを前記第1のFETのゲートに接続し、前記第1のFETのドレインが基準電圧を出力し、前記第1のFETのソースと前記第1のFETのソースがグランド又は他の回路と接続していることを特徴とする。

(もっと読む)

プリエンファシス回路及びこれを備えた差動電流信号伝送システム

【課題】プリエンファシス回路及びこれを備えた差動電流信号伝送システムを提供する。

【解決手段】本発明はプリエンファシス回路に関し、より詳細にはプリエンファシス回路を動作させるために必要なスイッチングトランジスタの数を減らして寄生抵抗及び寄生キャパシタを減少させ、それぞれのスイッチングトランジスタを制御するそれぞれのプリエンファシス制御信号を供給することによって望まない電流の発生を防止できるプリエンファシス回路及びこれを備えた差動電流信号伝送システムに関する。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

レベルコンバータ

【課題】ラッチ回路の初期値が確定可能であり、出力信号の立ち上がり/立ち下がり特性の対称性に優れたレベルコンバータを提供すること。

【解決手段】シフト回路12のラッチ回路31を構成する第1及び第2インバータ回路32,33の出力端子となるノードN1,N2とトランジスタTp1,Tp2との間に初期値設定用のMOSトランジスタTp3,Tp4を挿入接続した。そして、MOSトランジスタTp3のゲートをグランドに接続し、MOSトランジスタTp4のゲートを初期値設定回路34に接続した。初期値設定回路34は、第2の高電位電源VDEが所定レベル以下の場合には該MOSトランジスタTp4のゲート電位を第2の高電位電源VDEとグランドとの間の中間電位に制御し、第2の高電位電源VDEが所定レベルより高い場合には該MOSトランジスタTp4をオンするようそのゲート電位をグランドレベルに制御する。

(もっと読む)

双方向レベルシフト回路

【課題】高速に信号の伝達が可能な双方向レベルシフト回路を提供する。

【解決手段】実施形態によれば、第1の回路と、第2の回路と、第3の回路と、第4の回路と、を備えた双方向レベルシフト回路が提供される。前記第1の回路は、双方向に信号を伝達する。前記第2の回路は、前記第1の回路の両端の電位の変化に基づいて前記第1の回路の伝達方向を検出する。前記第3の回路は、前記第1の回路の両端の電位のいずれかがローレベルからハイレベルに上昇してから、前記第1の回路の両端の電位のいずれもがハイレベルになるまでの第1の期間を検出する。前記第4の回路は、前記第1の回路の両端にそれぞれ接続され、前記第1の回路の出力側に前記第1の期間ハイレベルの電位を供給する。

(もっと読む)

半導体装置

【課題】 ゲート−ソース逆バイアス駆動の動作原理を定量化し、MOSTのしきい電圧と動作電圧の関係を明らかにすることにより、逆バイアス駆動の原理を活用した複数のMOSTの組み合わせを用いて、動作電圧1V以下の高速低電圧動作を可能にする。

【解決手段】 低VtのMOSTを含む回路のリーク電流を、MOSTのゲート(G)とソース(S)を逆バイアスする各種の駆動方式によって低減する。低VtのMOSTに各種のG−S逆バイアスを加えることにより、リーク電流の少ない1V以下の高速低電圧CMOS論理回路、あるいはメモリ回路が実現される。

(もっと読む)

出力回路

【課題】回路規模が小さく、出力トランジスタのしきい値電圧がばらついてもノイズを抑えつつターンオフ時間を短縮する。

【解決手段】駆動信号SdがLの時、トランジスタT1がオン、T2がオフしてVGS(T3)がほぼ電源電圧Vccに等しくなりトランジスタT3がオンする。駆動信号SdがHになるとトランジスタT1がオフ、T2がオンする。トランジスタT4がオンするので抵抗R2がバイパスされ、トランジスタT3のゲート電荷はトランジスタT4、T2を通して急速に放電する。VGS(T3)がVth(T4)+VDS(T2)よりも低下すると、トランジスタT4はオフとなり、以後はトランジスタT3のゲート電荷が抵抗R2とトランジスタT2を通して緩やかに放電する。トランジスタT3、T4のしきい値電圧は一致する傾向があるので、VGS(T3)がVTH(T3)に低下した時点でトランジスタT4をオフできる。

(もっと読む)

レベル変換回路及び半導体装置

【課題】低面積化を図ること。

【解決手段】各信号BDT1〜BDTmをレベルシフトする回路として、クロックトレベルシフト回路(CLS回路)36(361〜36m)を用いた。CLS回路361は、ダイナミックコンパレータ回路(DC回路)411と、ラッチ回路421とを備える。DC回路411は、Lレベルのクロック信号ACKに応答してリセット状態となり、Lレベルの信号CDTm,XCDTmを出力する。また、CLS回路361は、Hレベルのクロック信号ACKに応答して比較状態となり、H1レベルの信号BDTm,XBDTmをH2レベルの信号CDTm,XCDTmにレベル変換する。ラッチ回路421は、相補な信号CDTm、XCDTmに応じた信号ADTm,XADTmを出力し、Lレベルの信号CDTm,XCDTmに応答して出力レベルを保持する。

(もっと読む)

半導体集積回路

【課題】

CMOS回路に中間電圧の入力信号が長時間連続して入力された場合にも貫通電流の発生を短時間にとどめることができる半導体集積回路を提供する。

【解決手段】

本発明の一実施態様に係る半導体集積回路は、入力端子と、出力端子と、ゲートが前記入力端子に接続されソースが高電位電源配線に接続された第1PMOSトランジスタ及びゲートが前記入力端子に接続されソースが低電位電源配線に接続された第1NMOSトランジスタを含み、当該第1PMOSトランジスタと当該第1NMOSトランジスタとが同時に導通しないように構成された第1CMOS回路と、入力端が前記第1CMOS回路に接続され出力端が前記出力端子に接続された第2CMOS回路と、この第2CMOS回路の出力端とと高電位電源配線及び高電位電源配線との間にそれぞれ配置された第2PMOSトランジスタと第2NMOSトランジスタと、を備える。

(もっと読む)

半導体出力回路及び外部出力信号生成方法並びに半導体装置

【課題】電源電圧の低下による外部出力信号のばらつきを抑制する。

【解決手段】内部入力信号Aの電位がグランド側からVDD側、あるいはVDD側からグランド側へ変化するのに応じて、出力部1は外部出力信号EBの電位を変化させる。差動部2は、外部出力信号EBと、所定の基準信号VREFとに応じた出力信号を出力し、外部出力信号EBが所定の基準信号VREFに応じた電位となるようボルテージフォロアとして機能する。これにより、外部出力信号EBの低電圧側出力電圧VOLのばらつきを抑制する。

(もっと読む)

61 - 80 / 888

[ Back to top ]