Fターム[5J067TA01]の内容

Fターム[5J067TA01]に分類される特許

41 - 60 / 219

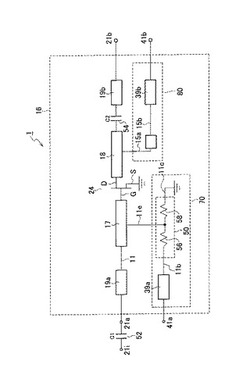

高周波モジュールおよびその動作方法

【課題】高温通電時にはバイアスジャンプを回避し、実運用時には外部電源を製品によらず共通化し、かつ端子数を削減する。

【解決手段】半導体装置24と、入力整合回路17と、出力整合回路18と、運用時用ゲートバイアス回路70と、運用時用ゲートバイアス回路70に接続された運用時用ゲートバイアス端子41aと、入力整合回路17に接続された高周波入力端子兼高温動作時用ゲートバイアス端子21aと、出力整合回路18に接続されたドレインバイアス回路80と、ドレインバイアス回路80に接続されたドレインバイアス端子41bと、出力整合回路18に接続された高周波出力端子21bとを備え、1つのパッケージに収納された高周波モジュール1およびその動作方法。

(もっと読む)

III族窒化物系高電子移動度トランジスタを含む低雑音増幅器

【課題】高い入力電力耐性と、低い雑音指数の両者を達成する低雑音増幅器を提供すること。

【解決手段】低雑音増幅器は、第一のIII族窒化物系トランジスタと、第一のIII族窒化物系トランジスタに結合された第二のIII族窒化物系トランジスタとを含んでいる。第一のIII族窒化物系トランジスタは、入力信号に対する第一増幅段を提供するように構成され、第二のIII族窒化物系トランジスタは、入力信号に対する第二増幅段を提供するように構成される。

(もっと読む)

電力合成分配器および電力合成分配器を用いた送信機

【課題】複数の増幅器のうちの一部が故障しても、電力合成分配器の分配損、合成損を最小とする。

【解決手段】複数の並列接続された第1の分岐側端子(113、114)と1つの第1の合成側端子(115)が第1の電力合成点(116)を介して接続された第1の分岐回路(127)と、複数の並列接続された第2の分岐側端子(133、134)と1つの第2の合成側端子(135)が第2の電力合成点(136)を介して接続された第2の分岐回路(137)とを有し、第1の合成側端子と複数の第2の分岐側端子が接続された電力合成あるいは電力分配を行う電力合成分配器において、第1の電力合成点から第2の電力合成点までの長さが1/2波長の整数倍である。

(もっと読む)

電力増幅器

【課題】 高調波成分の負荷を、基本波の調整に影響されることなく短絡から開放までの範囲で最適な負荷となるよう独立して設定することができ、高い電力変換効率を得ることができる電力増幅器を提供する。

【解決手段】 トランジスタ3の出力に、高調波に対する負荷を設定して反射する高調波反射回路4と、設定された高調波に対する後段の負荷の影響を分離する負荷分離回路5と、基本波についてトランジスタ3と出力負荷との整合を取る基本波整合調整回路6を備え、高調波反射回路4に設けられた先端開放スタブ23の長さが調整されることで、高調波の負荷を調整する電力増幅器としており、高調波成分及び基本波について独立して最適な負荷調整を行うことができ、電力変換効率を向上させることができるものである。

(もっと読む)

インピーダンス変換器、集積回路装置、増幅器および通信機モジュール

【課題】小型で伝送損失の少ないインピーダンス変換器、集積回路装置を実現する。

【解決手段】集積回路装置は、インピーダンス変換器15と、集積回路11A,11Bとを有し、インピーダンス変換器15は、第1の誘電率を有する第1の基板21の上方に設けられ、第1のインピーダンスを有する第1の伝送線路22A,22Bと、第1の誘電率より高い誘電率を有する第2の基板31の上方に設けられ、第1の伝送線路22A,22Bと電気的に接続され、第1のインピーダンスよりも低い特性インピーダンスを有する第2の伝送線路32AA,32ABおよび第3の伝送線路32BA,32BBと、第2の伝送線路32AA,32ABと第3の伝送線路32BA,32BBとの間に接続される抵抗35A,35Bとを有し、集積回路11A,11Bは、第2の伝送線路32AA,32ABおよび第3の伝送線路32BA,32BBと電気的に接続される。

(もっと読む)

広帯域高出力増幅器

【課題】広帯域増幅器の出力不整合と周波数切り替え回路で発生する不整合を調整し、高効率化を図ることができる広帯域高出力増幅器を得る。

【解決手段】少なくとも2倍高調波が広帯域増幅器1自身の帯域に含まれる広帯域高出力増幅器において、広帯域増幅器1の後段に、周波数帯域に応じた信号出力の切り替えを行う周波数切り替え回路2と、インピーダンス不整合を調整する整合回路5と、周波数帯域に応じて高調波成分を抑制するフィルタ回路4とを順次接続し、インピーダンス調整用整合回路5は、広帯域増幅器1の出力不整合と周波数切り替え回路2で発生する不整合を調整する。

(もっと読む)

バイアス回路

【課題】 不要波の出力を抑制することのできる小型なバイアス回路を得ることを目的とする。

【解決手段】 半導体素子3に電力を供給するバイアス回路において、インダクタ5及びキャパシタ6が直列に接続された直列回路と、直列回路に並列に接続されて並列回路を構成するインダクタ7と、接地されたキャパシタ8とインダクタ7との間に接続され、外部から電力が供給されるバイアス端子9を備えて、直列回路および並列回路の共振により、半導体素子3の不要波を除去し所望の周波数のみを伝達する。

(もっと読む)

電力増幅器

【課題】異なる周波数、出力電力または変調方式において動作可能な電力増幅器および通信機器を提供できる。

【解決手段】入力端子および出力端子を有する第1増幅器PA2と、入力端子および出力端子を有する受動回路PC3と、単極端子と、2つの多投端子とを有する第1スイッチSW2と、を備えた電力増幅器であって、該第1スイッチSW2の該多投端子の一方は、該第1増幅器PA201の該入力端子に接続されており、該第1スイッチSW2の該多投端子の他方は、該受動回路PC3の該入力端子に接続されている。

(もっと読む)

信号合成分配回路、電力増幅器および信号合成分配回路の製造方法

【課題】 簡単な構造で枝回路間の位相ずれによる利得低下を防止可能な信号合成分配回路を提供する。

【解決手段】 本発明の信号合成分配回路10は、基板11に、信号合成点または信号分配点14を有する複数の枝回路12a、12bおよび12cが配線され、前記複数の枝回路の少なくとも1本の枝回路12bが、他の枝回路12aおよび12cと異なる線路長であり、前記異なる線路長の枝回路12bの一部または全部15が、前記基板11中に配線されていることを特徴とする。

(もっと読む)

マイクロ波受信機

【課題】複数の増幅器を有するマイクロ波受信機において、小形な保護回路で、大電力のマイクロ波信号が入力されたときの後段増幅器の破壊・劣化を防ぐとともに、前段増幅器への反射電力を抑圧する。

【解決手段】この発明のマイクロ波受信機の前段増幅器の出力端と後段増幅器の入力端の間に挿入接続される保護回路は、その入力端子から出力端子へ至る使用周波数で約4分の1波長の伝送線路と、前記入力端子に一端が接続された第1の抵抗と、前記第1の抵抗の他端にカソード端子が接続されアノード端子が接地されたダイオードと、前記バイアス端子と前記ダイオードのカソード端子間に接続された第2の抵抗と、前記ダイオードのカソード端子と前記ゲートバイアス回路間に接続された第3の抵抗と、から構成した。

(もっと読む)

電力増幅回路及びフロントエンド回路

所定の送信信号に依存する前置増幅されたドライバー信号(S_DR)を供給するよう適用可能なドライバー段(DR)を備えた電力増幅回路(DIPPA)である。電力増幅回路(DIPPA)はまた、ドライバー段(DR)に電気的に結合されていて、ドライバー信号(S_DR)を第1及び第2の信号(S_1、S_2)へと分離するよう適用可能な周波数選択器(DIP)を備える。第1の信号(S_1)は第1の所定の周波数帯に対応付けられており、第2の信号(S_2)は第2の所定の周波数帯に対応付けられている。電力増幅回路(DIPPA)は、少なくとも第1及び第2の電力増幅段(PA1、PA2)を備える。第1及び第2の電力増幅段(PA1、PA2)は、周波数選択器(DIP)に電気的に結合される。第1及び第2の電力増幅段(PA1、PA2)は、それぞれ第1及び第2の信号(S_1、S_2)に依存する、それぞれ第1及び第2の増幅された信号(S_A1、S_A2)を供給する。 (もっと読む)

フィルタ、送受信装置及び増幅回路

【課題】高調波信号を抑制し、且つ、通過信号である基本波信号の減衰量を低減させる。

【解決手段】フィルタ200は、基本波信号f0及び基本波信号f0の高調波信号群2f0、3f0、4f0、5f0、6f0が入力される入力端子210と、入力端子210に入力された基本波信号f0を出力する出力端子220と、入力端子210と出力端子220とを接続する伝送線路230と、高調波信号群2f0〜6f0のうちの奇数高調波信号3f0、5f0に対応して設けられ、伝送線路230に接続し、対応する奇数高調波信号3f0、5f0の波長の1/4の長さを備えたオープンスタブ243、245と、伝送線路230に接続し、基本波信号f0の波長の1/4の長さを備えた第1のショートスタブ251と、伝送線路230に接続した第2のショートスタブ252と、を有する。

(もっと読む)

電力増幅装置

【課題】トランスを用いて複数の増幅器対の出力を合成する電力増幅装置において、各増幅器対の差動動作のずれによって生じる出力の低下を抑制する。

【解決手段】電力増幅装置110は、基板上に全体で環状に設けられた複数の一次インダクタ7,8と、複数の増幅器対3〜6と、二次インダクタ9と、接続配線10とを備える。各増幅器対は、対応の一次インダクタの両端に接続され、差動入力信号として与えられた一対の第1および第2の信号IN(+),IN(−)をそれぞれ増幅して対応の一次インダクタに出力する。二次インダクタ9は、複数の一次インダクタ7,8に隣接して環状に設けられ、各一次インダクタで合成された第1および第2の信号の合成信号をさらに合成して出力する。接続配線10は、基板上で複数の一次インダクタ7,8の内側に設けられ、各一次インダクタの中点MP1,MP2を互いに電気的に接続する。

(もっと読む)

マイクロ波高調波処理回路

【課題】電力効率を向上できるマイクロ波高調波処理回路。

【解決手段】入力端子がトランジスタの出力端子に接続され、所定の電気長を有する直列伝送線路T11の出力端子に1点で並列接続され2次以上でn次(nは任意の整数)までの高調波に対してそれぞれが所定の電気長を持つ異なる長さの(n−1)個の並列先端開放スタブT21〜T26、直列伝送線路と(n−1)個の並列先端開放スタブの内の2つの並列先端開放スタブT25,T26が1つの接続点で接続されて構成された第1ストリップ導体7、(n−3)個の並列先端開放スタブT21,T22,T34,T24が1つの接続点で接続されて構成された第2ストリップ導体3、第1ストリップ導体と第2ストリップ導体との間に配置された接地層5、第1ストリップ導体の接続部20と第2ストリップ導体の接続部22とを電気的に接続するビア10を有する。

(もっと読む)

マルチチップモジュール構造を有する高周波回路

【課題】マイクロ波・ミリ波における集積回路寸法を小型化し、安価なマルチチップモジュール構造を有する高周波回路を提供する。

【解決手段】複数のディスクリートトランジスタFET1〜FET3をそれぞれ形成する半導体基板161〜163と、複数のキャパシタC1〜C4をそれぞれ形成する第1誘電体基板141〜144と、複数の整合回路をそれぞれ形成する第2誘電体基板181,182とを備え、複数のディスクリートトランジスタFET1〜FET3は直列接続されたことを特徴とするマルチチップモジュール構造を有する高周波回路30。

(もっと読む)

増幅回路

【課題】増幅器と逆の利得偏移および位相偏移特性を持つリニアライザを具備する増幅回路を提供する。

【解決手段】複数のダイオードのそれぞれについて、所望の基本特性を有するダイオードを選択し、かつ、複数のダイオードのそれぞれに対応するバイアス回路について、所望のバイアス電圧を選択する。このように、複数のダイオードに複数のバイアス電圧をそれぞれ印加することによって、異なるダイオード特性を重ね合わせている。その結果、3次の非線形性よりもさらに複雑な5次の非線形性を有する増幅器の入出力電力特性の線形化が可能となる。

(もっと読む)

高周波回路の設計方法、高周波回路

【課題】少数の部品で高周波回路の安定性を向上させる。

【解決手段】電子回路と、該電子回路に並列に接続されたスタブと、該電子回路に並列に接続された抵抗と、を有する高周波回路において、該抵抗を分布定数回路である等価回路に置き換え、該高周波回路で用いられる第1の周波数で前記高周波回路のインピーダンスマッチングがとれており、且つ前記高周波回路が安定すべき第2の周波数で前記高周波回路が安定するように、前記スタブのインピーダンス値と、前記等価回路の抵抗値とを設定する。

(もっと読む)

増幅装置、無線基地局、及び増幅装置の制御方法

【課題】温度変化等に起因して回路特性が変化した場合であっても増幅装置の利得を所定範囲内に設定することが可能な増幅装置を得る。

【解決手段】増幅装置3は、ドハティ型の増幅装置であって、入力信号S1を入力信号S3と入力信号S4とに分配する分配器16と、入力信号S3を増幅するメインアンプ12と、入力信号S1の信号レベルが所定値以上である場合に、入力信号S4を増幅するピークアンプ13と、メインアンプ12から出力された出力信号S5と、ピークアンプ13から出力された出力信号S6とを合成して出力する出力部17と、メインアンプ12及びピークアンプ13の双方のゲートバイアス電圧Vgm,Vgpを略線形関係で制御することによって、増幅装置3の利得を所定範囲内に設定する制御部19とを備える。

(もっと読む)

増幅器

【課題】複数の増幅部(例えばキャリア増幅器及びピーク増幅器等)を有する増幅器を小型化することを目的としている。

【解決手段】入力信号が入力される入力部3と、入力信号を複数の信号に分岐させる分岐部4と、分岐部4で分岐された信号を増幅させる第一及び第二増幅部5、6と、第一及び第二増幅部5、6からそれぞれ出力されて合成された信号を出力する出力部9と、第一及び第二増幅部5、6が実装された基板2と、を備えており、第一増幅部5は、基板2の一方の主面2aに設けられ、第二増幅部6は、基板2の他方の主面2bに設けられている。

(もっと読む)

高調波終端回路

【課題】負荷条件が異なっても高調波を適切なインピーダンスで終端し、基本波に対しては影響のない高調波終端回路を得る。

【解決手段】高調波終端回路は、マイクロ波電力増幅器(4)のマイクロ波出力または入力を高調波処理する高調波終端回路において、基本波のおよそ4分の1波長の先端短絡スタブ(1a、1b、1c)および上記先端短絡スタブに直列に接続される抵抗(3a、3b、3c)を有する並列回路(30a、30b、30c)を3組備え、上記並列回路は、二次高調波のおよそ4分の1波長ずつ離れて伝送線路(2a、2b)に並列に接続される。

(もっと読む)

41 - 60 / 219

[ Back to top ]