Fターム[5J079EA03]の内容

電気機械共振器を用いた発振回路 (23,106) | 起動停止 (199) | 起動時の時限手段あり (64) | 自己出力検出 (21)

Fターム[5J079EA03]の下位に属するFターム

自己出力カウント (3)

Fターム[5J079EA03]に分類される特許

1 - 18 / 18

発振器

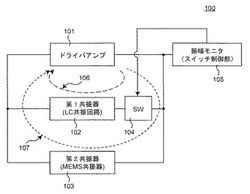

【課題】消費電流を増大させることなしに高速起動可能なMEMS発振器の提供。

【解決手段】ドライバアンプと、LC共振回路を備える第1共振器と、MEMS共振器を備える第2共振器と、接続および開放を切り換え可能なスイッチ回路と、スイッチ回路を制御するスイッチ制御部と、を有するMEMS発振器であって、ドライバアンプ、第1共振器、および、スイッチ回路は、ドライバアンプの出力信号の少なくとも一部をドライバアンプへ帰還させる第1閉ループ回路を形成し、ドライバアンプ、および、第2共振器は、第1閉ループ回路とは別の、ドライバアンプの出力信号の少なくとも一部をドライバアンプへ帰還させる第2閉ループ回路を形成し、スイッチ制御部は、MEMS発振器の起動期間の少なくとも一部においてスイッチ回路を接続し、所定の条件が満たされる場合に、スイッチ回路を開放する、MEMS発振器。

(もっと読む)

発振装置

【課題】水晶発振回路の消費電力の低減を図りつつ後段回路を作動させることができる発振装置を提供する。

【解決手段】第1電源V1が、振幅検出回路3に対して第1電源電圧(3V)を供給する。第2電源V2が、水晶振動回路2に対して第1電源電圧(3V)よりも小さい第2電源電圧(1V)を供給する。振幅検出回路3は、CMOSインバータIV1の出力端子から出力される発振信号と、第2電源電圧(1V)を分圧して得た基準電圧Vrefと、それぞれのベースに接続される一対のトランジスタが設けられたコンパレータ31を備えている。

(もっと読む)

発振回路

【課題】発振バッファへの過電圧の印加を防止し、発振起動時間を短縮できる発振回路を提供する。

【解決手段】発振回路10は、PTAT電流源12と、PTAT電流源12と接続されると共に、共振回路46と並列接続された発振バッファ14と、発振バッファ14と並列接続された帰還抵抗Rfと、帰還抵抗Rfよりも抵抗値が小さいバイパス抵抗Rbと、帰還抵抗Rfとバイパス抵抗Rbとの間に接続され、帰還抵抗Rf及びバイパス抵抗Rbの何れかに切り替えるためのPMOSトランジスタ48A、48Bと、PTAT電流源12からの電流が共振回路46へ供給開始されてから予め定めた発振起動期間は、PTAT電流源12からの電流がバイパス抵抗Rbへバイパスされるように、予め定めた発振起動期間経過後は、PTAT電流源12からの電流が帰還抵抗Rfへ流れるようにPMOSトランジスタ48A、48Bを制御するバイパスノード充電回路58と、を備える。

(もっと読む)

共振マイクロエレクトロメカニカルシステムをスターとするのに用いられるアンプにおけるDCオフセットを克服するためのシステム及び方法

【課題】共振マイクロエレクトロメカニカルシステム(MEMS)初期化成功を補償するシステム及び方法、特にESDによるDCオフセットを克服する方法を提供する。

【解決手段】システム20は、共振センサ24、駆動デバイス26、チャージアンプおよび電圧利得回路28を含む。スタートアップ時に、チャージアンプ及び電圧利得回路は、共振センサから信号を受信し、DCオフセットに関するこの信号を補償するために、駆動に関するクロック信号を生成し、これを用いて、安定した状態の動作モードにおける共振センサを実現する。回路は、受信された信号に関する信号にグリッチを生成するようにトグル切り替えされた複数の利得スイッチを含む。グリッチは、DCオフセットを補償する。受信された信号に関する信号が、リファレンス信号を越えている場合、比較器は、駆動デバイスに関するクロック信号を生成する。

(もっと読む)

発振器

【課題】面積を大きく増加させることなく消費電力の低減を可能にした発振器を提供すること。

【解決手段】本発明にかかる発振器は、水晶発振回路1の発振出力に応じたパルス信号SPに基づいて基準電圧VREFを生成し、基準電圧に応じて水晶発振回路1への供給電圧を制御する発振器である。パルス信号SPに基づいて制御信号SP2を生成する制御信号生成回路15と、制御信号SP2に基づいて基準電圧が制御される基準電圧発生回路16、17を備える。制御信号生成回路15は、パルス信号SPがロウレベルの場合にロウレベルの制御信号を生成し、パルス信号SPがハイレベルの場合にハイレベルの制御信号を生成するとともに、制御信号のハイレベルからロウレベルへの遷移を抑制することを特徴とする。それにより、水晶発振回路1への供給電圧が振幅しないので、面積を大きく増加させることなく消費電力を低減することが可能である。

(もっと読む)

発振検出回路

【課題】低電力化を可能とし、リーク電流による誤動作の発生を無くした発振検出回路を提供する。

【解決手段】発振検出回路は、基準電圧源に接続された第1の入力端子と発振回路出力端に接続された第2の入力端子とを有しており、複数のバイポーラトランジスタにより構成される差動回路を採用し、差動回路の出力端に接続され出力端の電位に応じて充電または放電を行う容量素子と、容量素子の電位に基づいて発振信号端の所望の発振状態を検出する検出回路を有する。

(もっと読む)

発振器

【課題】初期状態では発振余裕度を最大にして発振停止が発生しないようにし、安定状態へ遷移するに従い発振余裕度も小さくし、高調波も減少させてシステムとしての受信感度を向上させる発振器を提供する。

【解決手段】振動子を備え、発振余裕度の異なる複数の発振回路を備えた発振部と、発振部の出力電圧のピークを検出するピーク検出部と、ピーク検出部の検出したピーク電圧をアナログ信号からディジタル信号に変換するアナログ/ディジタル変換部と、ディジタル信号に基づいて所定の時間を計測する計測部と、ディジタル信号と計測部の出力に基づいて発振部の出力の切り替えを制御する切替信号と、計測部を制御する制御部と、を備える発振器である。

(もっと読む)

発振回路

【課題】自励発振が起こらず、出力対称性を確保できるようにした発振回路を提供する。

【解決手段】コルピッツ型の水晶発振回路において、CMOSインバータINV1の出力側(ノードN1)と電源VDDとの間に、CMOSインバータINV1の帰還バイアス電圧を高くするためのトランジスタMP1と発振出力が無いときONするトランジスタMP2とを直列接続して、電源投入初期時にそのノードN1をVDD/2より高い電圧にプルアップし、正常発振が開始してノードN3の電圧が所定値に達すると、トランジスタMP2をOFFしてノードN1のプルアップを解除する。また、CMOSインバータINV1の出力を反転するCMOSインバータINV2を接続し、その出力側のノードN2にアンド回路AND1を接続し、正常発振が開始してノードN3の電圧が所定値に達したとき、それから遅延回路DL1の遅延の後に、アンド回路AND1のゲートを開いて、ノードN2の発振信号を出力端子OUTに出力する。

(もっと読む)

発振回路およびその制御方法

【課題】増幅手段の駆動電力を連続制御し、発振起動時間の短縮や動作の安定性を確保しながら定常時の消費電力を効率的に低減することのできる発振回路およびその制御方法を提供する。

【解決手段】発振回路が駆動する負荷容量への充放電電流に応じて発振回路の駆動電力を制御することとしたため、発振起動時間や発振の安定性を犠牲にすることなく定常時の消費電力を効果的に低減することが出来る。また本発明を採用したシステムにおいては、環境の変動に応じて最適な電力を発振回路に与えることが可能となり、システム全体での省エネルギー化、電池の長寿命化が実現出来る。

(もっと読む)

半導体集積回路

【課題】電源電圧の低下、温度上昇等の発振器の動作条件の変動によって、発振後の発振動作の停止、発振安定時間の延長、起動時の発振の失敗等の不具合を解消すること。

【解決手段】入出力端子間に振動子が接続可能な反転増幅器Inv_Ampは、PMOSMp1とNMOSMn1を含む。ディジタル入力信号に応答して出力インピーダンスが変化するよう抵抗とMOSスイッチとを含む複数のD/A変換器D/Ap_1…D/Ap_n、D/An_1…D/An_nを、Mp1のソースと電源電圧VccまたはMn1のソースと接地GNDの間に接続する。可変利得発振器VG_OSCの動作条件の変化をA/D変換ユニット102が検出して、複数のD/A変換器の合計の出力インピーダンスを徐々に変化させる。

(もっと読む)

高速始動付き低雑音基準発振器

速い始動時間及び定常状態での低い雑音を有する周波数源が提供される。周波数源は、発振器(102)と、発振器始動でのアナログAGCループと定常状態の動作でのデジタルAGCループとの間を切り替えるハイブリッド自動利得制御(AGC)ループとを含む。アナログAGCループは、発振器(102)に接続されたピーク検出器(104)と、ピーク検出器(104)出力と基準電圧との差を積分する誤差積分器(106)とを含む。デジタルAGCループは、ピーク検出器出力と高/低基準電圧とを比較する比較器(110)と、タイマ信号を与える発振器(102)カウンタと、デジタル・ワードを供給されるデジタル/アナログ変換器(DAC)(114)と、DAC(114)と発振器(102)との間のロー・パス・フィルタ(116)とを含む。タイマ信号は、マルチプレクサ(108)にアナログAGCループ又はデジタルAGCループのいずれかを選択させる。  (もっと読む)

(もっと読む)

始動制御装置を含む発振器

発振装置(1)には、発振器コア(2)と、制御可能な静電容量値を有する、発振器コア(2)に接続された容量性ローディングユニット(3、3a、3b)と、第1および第2のメモリユニット(5a、5b)を含む、容量性ローディングユニットに接続されたメモリ装置(4)と、が含まれる。第1のメモリユニット(5a)は、始動期間中に、静電容量値を制御するために容量性ローディングユニット(3、3a、3b)に供給される第1の値を格納するように構成される。第2のメモリユニット(5b)は、動作期間中に、静電容量値を制御するために容量性ローディングユニット(3、3a、3b)に供給される第2の値を格納するように構成される。発振装置(1)の始動方法によれば、発振信号の振幅が測定される。さらに、動作期間の開始時点が、発振信号が所定の閾値を超える時点として選択される。  (もっと読む)

(もっと読む)

圧電発振器

【課題】 解決しようとする課題は、あらゆる圧電発振器に対して起動時間の短縮化を実現すること。

【解決手段】圧電振動子を有する圧電発振回路と、該圧電発振回路の発振ループ回路と電源電圧ラインとを接続する為のスイッチ回路と、該スイッチ回路のON/OFF動作を制御する為の制御回路とを備えた圧電発振器であり、前記電源電圧印加した後、前記圧電振動子の励振信号の振幅レベルが極大値±0.1λの範囲内である時に前記スイッチ回路がON動作するものであることを特徴とする圧電発振器。

(もっと読む)

電圧制御発振回路用の印加電圧制御回路

【課題】LSIから制御可能な汎用ポートの“H”レベルのレベルが、トランスミッションゲートの“H”レベルを認識する最小許容値を満足しない可能性が発生し、水晶振動子の発振安定に時間かかる。

【解決手段】電源起動時はNPNトランジスタQN1を遮断状態にして、第1のトランスミッションゲートG1を導通状態に、第2のトランスミッションゲートG2を遮断状態にし、電源電圧VDDを第1のトランスミッションゲートG1を介して電圧制御発振回路100の制御入力端子n3に印加する。水晶振動子Xの発振安定後は汎用端子12への制御信号によりNPNトランジスタQN1を導通状態に切り替えることを通じて第1のトランスミッションゲートを遮断状態に、第2のトランスミッションゲートを導通状態に切り替え、電圧制御端子11の電圧を第2のトランスミッションゲートG2を介して電圧制御発振回路の制御入力端子に印加する。

(もっと読む)

発振器起動制御回路

【課題】起動時間を短縮するとともに、起動時間を安定して制御し、さらに発振回路の起動後、発振周波数を安定化することができる発振器起動制御回路を提供する。

【解決手段】発振回路(1)は、インバータ(14)の入力と出力を水晶振動子(15)の両端および抵抗(16)の両端に接続し、入力をMOS可変容量(10)のドレインに、出力をMOS可変容量(11)のドレインに接続し、MOS可変容量(10)のソースを固定容量(12)に接続し、MOS可変容量(11)のソースを固定容量(13)に接続し、固定容量(12、13)の他端をGNDに接続している水晶発振回路である。更にMOS可変容量(10)のゲートに抵抗(18)とスイッチ(7)を接続し、MOS可変容量(11)のゲートに抵抗(19)とスイッチ(8)を接続し、抵抗(18、19)の他端を互いに接続し、更に電圧制御回路(3)に接続している。

(もっと読む)

発振回路

【課題】発振ゲートの切り替えに伴うクロックパルス出力の欠損を防止しつつ、効率的な切り替えを行って低消費電流で且つ低電圧動作可能な発振回路を提供する。

【解決手段】発振開始当初は負荷回路2を第一の状態に、発振安定後は負荷回路2を第二の状態にする発振回路に、CMOS型発振ゲート1の出力端子からの発振パルス数に応じて負荷回路2を第一の状態から第二の状態に緩やかに遷移させる遷移手段を設けて、負荷回路2の等価インピーダンスを発振クロックパルス数によって緩やかに増大させる構成とした。

(もっと読む)

クロック生成回路及び方法

【課題】クロック生成回路の消費電力を低下させる。

【解決手段】クロック生成回路は、水晶振動子28と差動増幅器16とを備え、差動増幅器16は、水晶振動子28の第1ノードに接続された第1入力端子12と、バイアス信号が印加される第2入力端子20と、水晶振動子28の第2ノードに接続された出力端子24を有し、可変利得手段を備えている。差動増幅器16の出力端子に接続されたピーク検出器の出力により差動増幅器16の利得を可変し、起動時には利得を大きくし、通常動作時には利得を小さくする。これにより、消費電力を低下させる。

(もっと読む)

VCXOの起動時間を短縮するための方法と装置

無線端末(10)の所望の基準周波数を生成するための、低減された起動時間を有するVCXO(Voltage Controlled Crystal Oscillator)(100)のような電圧制御発振器(100)が本願明細書において記載されている。本発明によれば、VCXO(100)は、電圧コントローラ(110)によって発振器(120)に印加された可変電圧に基づいて、所望の基準周波数を生成する発振器(120)を含む。加えて、VCXO(100)は、発振器(120)に伴うキャパシタンスを低減するためバイアス電圧を発振器の入力ノードに印加し、VCXO(100)のDC電流消費または同調レンジに悪影響を与えること無く起動時間を低減する起動コントローラ(130)を含む。  (もっと読む)

(もっと読む)

1 - 18 / 18

[ Back to top ]