Fターム[5J079FB47]の内容

電気機械共振器を用いた発振回路 (23,106) | 回路要素 (2,263) | バッファアンプ、インピーダンス変換回路 (88)

Fターム[5J079FB47]に分類される特許

61 - 80 / 88

感知装置

【課題】水晶振動子とトランジスタ増幅回路で構成したコルピッツ発振回路で、十分な負性抵抗を確保して安定発振を得るとともに、振幅制御回路を不要にし、さらに温度変化に対する安定化も可能とする。

【解決手段】トランジスタのコレクタに設ける同調回路のインピーダンスが発振周波数において誘導性を呈する構成にする。トランジスタのベース・エミッタ間に接続されるコンデンサC2とエミッタ・GND間に接続されるコンデンサC3との発振周波数におけるインピーダンス比が3対1以上、かつベース・エミッタ間に接続される容量C2の発振周波数におけるインピーダンスが300Ω以上とする。トランジスタのコレクタ・ベース間に接続されるバイアス抵抗R1が3kΩ以下とする。トランジスタのベース・GND間に温度補償用ダイオードD1を直列に介挿する。

(もっと読む)

出力回路を備えた発振回路

【課題】電源電圧を低電圧化した場合においても、発振回路の最終出力波形のデューティー比を50%に調整し易く、且つ、種々の外乱要因によってもデューティー比の変動を少なく抑えることが可能な発振回路を提供する。

【解決手段】振動子、増幅回路及び出力回路を含む発振回路であって、前記増幅回路の入力端子に接続される側の前記振動子の端子と、前記出力回路の入力端子とが接続され、振動子の前記端子と、増幅回路の前記入力端子とが容量を介して接続され、さらに、振動子の前記端子側に、所定の電位をバイアスするためのバイアス回路が接続されている。

(もっと読む)

システム回路及びその設定方法

【課題】誤動作を生じさせ得る外乱や雑音により、不測の動作を行うおそれがあった。

【解決手段】前段回路と、前段回路の後段かつ被制御装置の前段に位置に設けられた後段回路とを含み、被制御装置に動作を許可する第1の工程と、被制御装置に動作を維持させる第2の工程と、被制御装置に動作を引き続き維持させる第3の工程と、被制御装置に動作を禁止させる第4の工程とを、前段回路と後段回路とが協動して行う。

(もっと読む)

発振回路、電子回路、これらを備えた半導体装置、時計及び電子機器

【課題】入出力端子を介して外部から侵入するサージ電圧から前記主要回路部分を保護することができ、しかも発振回路の電源電圧の変動の影響を受けることなく、安定した周波数で発振することができる発振回路、電子回路、これらを備えた半導体装置、時計及び電子機器を提供すること。

【解決手段】主電源の電源電圧の変動の影響を受けることなく、安定した周波数で発振することができる発振回路を提供すること。

発振回路40に設けられた静電保護回路200は、信号路と前記定電圧Vreg側との間に接続され、信号路に侵入する第1の極性の静電圧をダイオード72を介してバイパス用定電圧Vreg側へバイパスさせる第1の静電保護回路部210と、前記信号路とアース側との間に接続され、信号路に侵入する第2の極性の静電圧をダイオード74を介してアース側へバイパスさせる第2の静電保護回路部220とを含む。

(もっと読む)

発振回路

【課題】発振増幅器の出力側におけるノイズ成分の影響を抑制すると共に、所望の信号成分を得るための発振回路を提供する。

【解決手段】圧電振動子と増幅器を接続して、発振閉ループを形成してなる発振回路であって、増幅器の入力と、圧電振動子との接続点から、発振信号成分を取り出す。

(もっと読む)

水晶発振器

【課題】1つのICで効率良く、搭載されるセットの仕様や周波数に対応できる水晶発振器を提供する。

【解決手段】発振器1の出力側を、出力側が第1の抵抗7に接続されたインバータ2の入力側と第2の抵抗8の一端とに接続し、第1の抵抗7の他端を第1の容量9の一端と第1のトランジスタ3の入力側とに接続し、第1の容量9の他端を第1のスイッチ11の一端に接続し、第1のスイッチ11の他端を接地し、前記第2の抵抗8の他端を第2の容量10の一端と第2のトランジスタ4の入力側とに接続し、第2の容量10の他端を第2のスイッチ12の一端に接続し、第2のスイッチ12の他端を接地し、第1のトランジスタ3の出力側と第2のトランジスタ4の出力側とを発振出力端子5に接続し、第1のスイッチ11と第2のスイッチ12とを記憶装置13にて制御する。

(もっと読む)

逓倍発振回路及びECL出力圧電発振回路

【課題】小型化で異常発振の発生を抑制できる逓倍発振回路を提供する。

【解決手段】水晶振動子Y1を有し所定の周波数で発振する水晶発振回路11と、水晶発

振回路11の発振出力に含まれる所定の高調波出力に同調する同調回路13と、増幅用ト

ランジスタQ2とこの増幅用トランジスタQ2コレクタ−ベース間に接続され自己バイア

ス機能とデカップリング機能を有する抵抗R4と、増幅用トランジスタQ2コレクタに接

続され、増幅用トランジスタQ2から出力される所定の高調波出力に同調する同調回路1

5と、同調回路13と同調回路15との間を結合する結合コンデンサC6とを備えるよう

にした。

(もっと読む)

移動通信基地局装置の恒温槽付水晶発振器のウォームアップ方法及び移動通信基地局装置

【課題】充放電回路を利用したウォームアップ方法は、電源断時間によっては、ウォームアップ時間を最適な時間に短縮することができない。また、温度上昇速度の恒温槽付水晶発振器の個体差分のウォームアップ時間を短縮することができない。

【解決手段】CPU102は、上位装置150からの現在時刻を一定時間毎に更新してFーROM103に更新記憶している。装置電源の瞬断が発生した場合、CPU102は、電源復旧時にF−ROM103に更新記憶されていた時刻を電源断時刻とし、また、電源が復旧したときに上位装置150から取得した現在時刻とから電源断時間を算出し、その電源断時間と、FーROM103から読み出した、予め恒温槽付水晶発振器104の出力クロックから算出された電源断時間対ウォームアップ時間の傾き値とを用いて、恒温槽付水晶発振器104の個体差の影響のない、最短のウォームアップ時間を算出する。

(もっと読む)

発振装置

【課題】発振信号の発振周波数が高いほど、当該発振信号の波形がより鈍っていた。

【解決手段】発振信号を生成する発振回路と、前記生成された発振信号を増幅する増幅回路と、相互に並列接続された複数のCMOSバッファ回路であって、当該複数のCMOSバッファ回路の入力端が一つに接続されており、当該複数のCMOSバッファ回路の出力端が一つに接続されており、各CMOSバッファ回路が前記増幅された発振信号をバッファリングする前記複数のCMOSバッファ回路と、を含む。

(もっと読む)

コルピッツ型発振回路

【課題】比較的安価なトランジスタを使用して、高周波域で高い負性抵抗が得られ、しかも高い発振出力も得られる。

【解決手段】回路ブロックAは、トランジスタQ1と水晶振動子X等によってコルピッツ型発振回路に構成する。回路ブロックBは、ベース接地形増幅回路に構成されたトランジスタQ2でトランジスタQ1のエミッタ出力を増幅し、このコレクタ出力をベース回路(またはコレクタ)に同相で正帰還させる。回路ブロックCはトランジスタQ2の出力を発振出力として取り出す。トランジスタQ2のコレクタに発振周波数も同調させた同調回路を設けた構成、または発振周波数に同調させた同調回路を正帰還の回路に介挿させた構成も含む。

(もっと読む)

弾性表面波発振器

【課題】発振周波数の調整を容易にしたインダクタを有する弾性表面波発振器を提供する。

【解決手段】発振用増幅器と帰還回路とから発振閉ループを形成し、前記帰還回路には少なくとも弾性表面波フィルタと、発振周波数を変化させるインダクタと有する弾性表面波発振器において、前記インダクタは少なくともトリミングパターンを有し、前記トリミングパターンの両端子間に最下段が接続した2段以上の第1梯子状パターンと、前記第1梯子状パターンに並列方向に接続した少なくとも第2梯子状パターンを有することを構成とする。

(もっと読む)

高周波コルピッツ発振回路

【課題】

高周波帯域で使用できると共に低ドライブレベルでの発振が可能な高周波コルピッツ発振回路を提供すること。

【解決手段】

コルピッツ発振回路とコレクタ接地増幅回路とを備え、前記コルピッツ発振回路の出力端子を前記コレクタ接地増幅回路の入力端子とを接続し、前記コレクタ接地増幅回路の出力を前記コルピッツ発振回路に帰還接続するよう構成を有することを特徴とする高周波コルピッツ発振回路。

(もっと読む)

発振回路

【課題】本発明は発振回路部の発振出力をバッファするバッファアンプを有する発振回路に関し、安定した発振出力を高速に出力することが可能な発振回路を提供することを目的とする。

【解決手段】本発明は、発振回路部と、発振回路部の発振出力を出力する出力アンプとを有する発振回路において、発振回路部の起動電圧と出力アンプの起動電圧との異なる電圧とし、発振回路部が起動した後に出力アンプが起動するようにしたことを特徴とする。

(もっと読む)

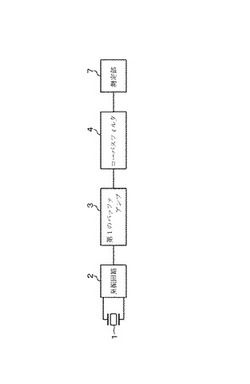

マイクロ波発生装置およびこれを用いた機器

【課題】小型化および軽量化がなされるとともに、不要輻射が生じないマイクロ波発生装置およびこれを用いた機器を提供する。

【解決手段】マイクロ波発生装置10は、高周波信号を出力するダイヤモンドSAW発振器20と、このダイヤモンドSAW発振器20から入力した前記高周波信号を増幅して出力する第1増幅器16と、前記ダイヤモンドSAW発振器20および前記第1増幅器16に電力を供給する電源18とを備えた高周波電源部12と、前記高周波電源部12から入力した前記高周波信号をマイクロ波として放射する導波手段14とを備えた構成である。

(もっと読む)

発振回路

【課題】 システムLSI13に高速クロックを供給する手段を少ない回路及び回路素子で構成し、回路規模を増大させず、環境に配慮し、低消費電力を達成できる発振回路を提供する。

【解決手段】 共振回路14またはLSIテスタが外部接続される第1及び第2接続端子9、10、システムLSI13に接続される接続端子11、第1及び第2接続端子9、10間に接続された第1転送回路4と第1インバータ2の第1直列接続回路、第1直列接続回路に並列接続された負帰還抵抗3、第1インバータ2の出力端と接続端子11間に接続された第2転送回路6と第2インバー5の第2直列接続回路、第1接続端子9と接続端子11間に接続された第3転送回路8と第3インバータ7の第3直列接続回路を備え、第1〜第3転送回路2、5、7は、ゲートに相補TE信号が供給される相補MOSトランジスタの並列回路からなり、第1及び第2転送回路2、5に供給される相補TE信号の極性と第3転送回路7に供給される相補TE信号の極性とが逆極性になる。

(もっと読む)

集積回路

【課題】従来の発振器用集積回路では、低振幅の出力波形を要求された場合に、出力増幅回路トランジスタ対のゲート・ソース間電圧が十分に確保できず、大きな負荷を駆動できないという問題があった。

【解決手段】 出力増幅回路112のPチャネルトランジスタ110およびNチャネルトランジスタ111のゲートを、コンデンサ106および107により発振回路104の出力に交流的に結合するとともに、抵抗108および109を介してPチャネルトランジスタ110のゲートはGND電位に、Nチャネルトランジスタ111のゲートは電源電位にバイアスされていることにより、これらのトランジスタのゲート・ソース間電圧が充分に確保され、大きな負荷を駆動できるようにしたことを特徴とする集積回路。

(もっと読む)

コルピッツ型発振器

【課題】主振動(Cモード)での安定発振を得ながら、不要振動(Bモード)を確実に抑圧した発振を得る。

【解決手段】圧電振動子X1とトランジスタQ1および分割容量成分C1,C2を含むコルピッツ型発振器において、容量成分C1と容量成分C2との接続中点とトランジスタのエミッタとの間に容量成分C3とインダクタL1の直列接続から成る帰還回路を挿入し、容量成分C2と並列にインダクタL2を挿入し、容量成分C2とインダクタL2の並列共振周波数を当該発振器の発振周波数近傍に設定することにより、圧電振動子から見た回路側の負性抵抗となる周波数帯域を、所望する周波数のみを含む狭帯域に設定して当該発振器の不要振動を抑圧する。

(もっと読む)

圧電発振回路

【課題】 広い電源電圧範囲で安定した発振特性を得ると共に、発振出力の振幅を調整することができる圧電発振回路を提供すること。

【解決手段】 直流電源VDDから供給される直流電圧の電圧変動を安定化する安定化電源6と、水晶振動子X1を振動源とする発振回路部1と、この発振回路部1の出力信号を入力とし、インバータ回路を複数段直列に連結し、その最終段のインバータ回路にデプレッション型MOSトランジスタが接続されたバッファ回路部2、3、4と、バッファ回路4の出力を増幅する出力増幅回路5とを備えた圧電発振回路において、メモリ回路11に保持されたデータに基づいて複数のMOSスイッチMsw1〜Msw3により選択される抵抗素子RD1〜RD3により、出力増幅回路5を構成するNch−トランジスタM9のゲート電圧を可変して出力レベルを調整する機能を備える。

(もっと読む)

発振バッファ回路

【課題】 外部端子を新たに設ける必要がなく、追加回路部分を最小限に留め、内部クロック信号の発振及び発振停止が行える発振バッファ回路を提供する。

【解決手段】 第1接続端子TX1と第2接続端子TX2を備え、インバータ3の入出力端子間に抵抗4が接続され、インバータ3の入力端子が第1接続端子TX1に、インバータ3の出力端子が第2接続端子TX2に接続された発振回路9と、第1接続端子TX1と第2接続端子TX2間に接続された発振周波数設定素子5を含む発振周波数設定回路10と、第1接続端子TX1と回路基板上のノード間に接続されたダイオード2とを備え、ノードは、回路基板上の構成部品が通常動作時またはスタンバイ時に設定されたとき、高レベル電位または低レベル電位が選択的に印加され、それによりノードの電位によって発振回路9が発振状態または発振停止状態に切替えられる。

(もっと読む)

圧電発振器

【課題】 高速起動回路を備えた水晶発振回路をIC化する際の小型化する手段を得る。

【解決手段】 圧電振動子と、増幅回路と、高速起動回路とを備えた圧電発振器であって、高速起動回路は第1のPNP型Tr(トランジスタ)と、第2のNPN型Trと、第3のPNP型Trとを備え、第1のTrのエミッタと電源との間に第1の抵抗を接続すると共にコレクタを接地し、第2のTrのコレクタを電源に接続すると共にベースとエミッタとを接続し、エミッタ−接地間に容量を接続し、第2のTrのエミッタと第1のTrのベースを接続し、第2のTrのエミッタと第3のTrのベースとを接続し、第3のTrのコレクタを圧電振動子の一端子に接続して構成される。

(もっと読む)

61 - 80 / 88

[ Back to top ]