Fターム[5J081CC33]の内容

LC分布定数、CR発振器 (9,854) | 目的、効果 (1,425) | 動作の改善 (284) | 起動停止の動作 (27) | 起動時の安定化 (17)

Fターム[5J081CC33]に分類される特許

1 - 17 / 17

発振回路、発振器、電子機器及び発振回路の起動方法

【課題】起動時の異常発振を抑えるとともに負荷の大きさによらず電源電圧の低電圧化が可能な発振回路、発振器、電子機器及び発振回路の起動方法を提供すること。

【解決手段】発振回路1は、共振子(水晶振動子10)と、共振子の一端から他端への帰還経路を有する増幅回路20と、電圧供給回路30と、を含む。電圧供給回路30は、電源電圧Vccが入力される時定数回路(抵抗32とコンデンサー34によるRC積分回路)を有し、電源電圧Vccが入力されてから時定数回路の時定数に応じて立ち上がるとともに増幅回路20の負荷によらず一定電圧となる駆動電圧VAを発生させ、駆動電圧VAを増幅回路20に供給する。

(もっと読む)

発振回路、発振器、電子機器及び発振回路の起動方法

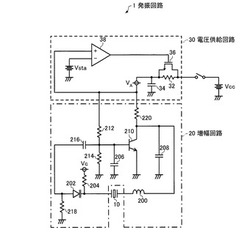

【課題】インダクタンス素子に起因して発生する起動時の異常発振を効率的に抑えることが可能な発振回路、発振器、電子機器及び発振回路の起動方法を提供すること。

【解決手段】発振回路1は、共振子(SAW共振子10)と、増幅回路20と、スイッチング素子(NMOSスイッチ30)と、を含む。増幅回路20は、共振子の一端から他端への帰還経路、当該帰還経路に設けられている第1のインダクタンス素子(伸長コイル200)、当該帰還経路に設けられ、第1のインダクタンス素子と直列に設けられている可変容量素子(可変容量ダイオード202)、を有している。スイッチング素子は、第1のインダクタンス素子と可変容量素子とを含む回路部に対して並列に設けられている。

(もっと読む)

発振回路

【課題】コンパレータの消費電力を抑えつつ、高周波の発振出力の振幅を検出できる、発振回路を提供すること。

【解決手段】水晶振動子1を共振器として使用して発振出力Vxを生成する発振出力生成回路11と、発振出力Vxの振幅を検出する振幅検出回路15と、振幅検出回路15の出力Vsに応じて発振出力Vxをブーストするブースト回路16とを有する発振回路であって、振幅検出回路15は、発振出力Vxが入力される絶対値回路12と、絶対値回路12の出力を入力とするローパスフィルタ13と、ローパスフィルタ13の出力を入力とするコンパレータ14とを備えることを特徴とする、発振回路。

(もっと読む)

圧電発振器

【課題】ピアース型圧電発振器で高い周波数出力を可能にする。

【解決手段】圧電振動子10の一方の端子と接地電位線GNDとの間に接続された第1の容量素子C1と、圧電振動子10の他方の端子と接地電位線GNDとの間に接続された第2の容量素子C2と、コレクタ端子が圧電振動子10の一方の端子に接続されベース端子が圧電振動子10の他方の端子と電流源20とに接続されエミッタ端子が接地電位線GNDに接続された発振用トランジスタQ1と、ベース端子が発振用トランジスタQ1のコレクタ端子に第1の抵抗Rbを介して接続されコレクタ端子が発振用トランジスタQ1のコレクタ端子に第2の抵抗Rcを介して接続されエミッタ端子が発振用トランジスタQ1のベース端子に接続された発振補助用トランジスタQ2と、を含んで構成される発振回路101と、発振用トランジスタQ1のコレクタ端子に接続されたバッファ回路BUFと、を含む圧電発振器1。

(もっと読む)

帰還型発振装置

【課題】発振開始時の立ち上がりを迅速に行うとともに、増幅素子に流れるバイアス電流を適正化すること。

【解決手段】準ミリ波帯域またはミリ波帯域を発振周波数帯域とする帰還型発振装置1において、入力端子から入力された信号を出力端子から出力する増幅素子(HEMT10)と、増幅素子の出力端子から入力端子に信号を帰還するための帰還回路(帰還回路40)と、増幅素子の出力端子と電源の間に挿入され、持続発振時に増幅素子に流れるバイアス電流を制限する抵抗素子(抵抗素子35)と、を有する。

(もっと読む)

圧電発振器

【課題】水晶発振器などの圧電発振器において、出荷時あるいは受け入れ時の調整や検査に際して発振器特性の計測に要する時間を短縮でき、かつ、電子機器への搭載後においても一時的な電源断に対応できるようにする。

【解決手段】水晶振動子12などの圧電振動子と発振回路16とを収容した容器10内に、二次電池11と、二次電池11に対する充放電を制御する充放電制御回路14と、電源端子に外部電源電圧Vccが印加されているときには電源端子を選択し、それ以外の場合に充放電制御回路14を選択して電力を発振回路16に供給する切替回路15と、を設ける。

(もっと読む)

発振装置および角速度検出装置

【課題】振動子の起動を確実にし、安定して振動を維持する装置を提供する。

【解決手段】振動子12と、振動状態を検出する検出アンプ13と、振動情報を2値化してコンパレータ出力信号を出力する振幅比較器14と、制御発振器入力信号に応じて周波数が変化する電圧制御発振器151と、コンパレータ出力信号と比較信号との位相差信号を出力する位相比較器153と、位相差信号の低域成分を出力するループフィルタ154と、比較信号に対して予め定める位相差を有する位相シフト信号を出力する位相シフト器22と、位相シフト信号を入力する駆動アンプ11と、操作信号を出力する操作信号発生器21と、制御発振器入力信号として操作信号を選択し、制御発振器出力信号の周波数がキャプチャレンジの範囲となったときに、制御発振器入力信号として位相差情報信号を選択する操作切換器20と、を備える。

(もっと読む)

発振装置

【課題】発振周波数を決定する容量値の変化に伴う発振周波数の変動を抑え、且つ、位相雑音を低減することのできる発振装置を提供する。

【解決手段】発振装置は、ドレイン接地回路からなる第1増幅回路10と、第1増幅回路10の出力を増幅する、ゲート接地回路からなる第2増幅回路20と、第2増幅回路20の出力を第1増幅回路の入力に帰還させるコンデンサC1と、第1増幅回路10の入力側に設けられた共振器2と、共振器2及び第1増幅回路10内のトランジスタQ1に動作用のバイアス電圧を印加するバイアス回路12と、第2増幅回路20内のトランジスタQ2に動作用のバイアス電圧を印加するバイアス回路22とから構成される。この結果、位相雑音の発生を、単一のトランジスタからなるコルピッツ発振回路と同程度に抑えつつ、容量変化によって発振を起動できなくなったり、発振周波数が変動するのを防止できる。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

発振制御回路

【課題】発振開始時からデューティが50%に安定する発振制御回路を提供する。

【解決手段】作動制御回路3が、発振信号の発振電位がCMOSインバータIV1の反転電位よりも低い第1基準電位よりも低くなるまでMOSトランジスタT11及びT12をオフ状態、MOSトランジスタT2をオン状態に保持する。作動制御回路3が、発振信号の発振電位が第1基準電位よりも低くなったとき出力が反転するCMOSインバータIV31と、CMOSインバータ31の後段に設けた抵抗R31とコンデンサC31とからなるローパスフィルタ31と、ローパスフィルタ31の出力が閾値を越えると出力が反転するCMOSインバータ33と、を有している。

(もっと読む)

発振回路

【課題】従来の発振回路は、発振信号を増幅させる電流等の影響で発振周波数の高速化が制限されるという問題があった。

【解決手段】本発明にかかる差動発振回路は、帰還ループ回路を備えた差動型の発振回路であって、帰還ループ回路上に縦続接続され、入力された一対の差動入力信号を遅延させて一対の差動出力信号として出力する遅延回路2〜5と、発振回路が発振起動状態か安定状態のいずれかにあるかを検出し、検出結果を示す検出信号VSTPを出力する発振起動検出回路7と、を備える。さらに遅延回路2〜5は、発振起動検出回路7から出力された検出信号VSTPに基づいて、差動出力信号の出力電流値を制御する。このような回路構成により、発振周波数の高速化が可能である。

(もっと読む)

電圧制御型可変周波数発振回路および信号処理回路

【課題】可変容量素子の容量可変域に応じた広い周波数可変域を確保することができる電圧制御型可変周波数発振回路を提供する。

【解決手段】コイルL1,L2および可変容量素子111,112を有する共振回路101と、負性抵抗回路102とを含む発振回路部103を備える電圧制御型可変周波数発振回路である。発振回路部103と電源電位VDDとの間に第1の抵抗301を設ける。また、発振回路部と接地電位端との間には第2の抵抗302を接続するとよい。

(もっと読む)

発振器

【課題】発振周波数変更機能を備えた発振器において、不揮発性メモリからデータを読み出す際に発振周波数が変更されることなく安定的に読み出すことができる。

【解決手段】LSIの外部に設けられた不揮発性メモリ15に、発振回路13から発振されるクロック信号の周波数を変更するための周波数設定値が記憶されており、その周波数設定値が、発振回路13から発振される初期設定された周波数のクロック信号によって読み出されると、ダミーレジスタ11に格納される。不揮発性メモリ15からデータが全て読み出されてロード動作完了信号が出力されると、ダミーレジスタ11から記憶レジスタ12へ周波数設定値が格納され、発振回路13の発振周波数が周波数設定値とされる。

(もっと読む)

超低電力RC発振器

【課題】超低電力RC発振器を提供する。

【解決手段】超低電力RC発振器は、電流源311と、所定の割合で組み合わせて構成された可変抵抗とを含み、前記可変抵抗により電流の大きさを調節する電流発生部310と、前記電流発生部が安定に電流を発生させ得るように一定のバイアス動作点に固定させるスタートアップ回路部340と、可変キャパシタと複数のトランジスタとを含み、前記電流発生部に発生した電流及び前記複数のトランジスタを利用して、前記可変キャパシタを充放電させる充放電回路部320と、複数のインバータを含み、前記可変抵抗の抵抗値及び前記可変キャパシタのキャパシタンス値により周波数が決定される発振信号を出力する発振信号出力部330と、前記電流発生部からの電流をミラーリングした電流を前記複数のインバータの駆動電源として提供するインバータ駆動電源部350とを含む。

(もっと読む)

電圧制御発振器

【課題】 高速起動性、低位相雑音性および低消費電力特性のすべてを充足できる電圧制御発振器を提供する。

【解決手段】 バイアス部は、電流源と、電流源に直列形態に接続される第1トランジスタと、第1トランジスタにカレントミラー接続され、制御電圧に応じて所望の周波数の発振信号を生成する本体部にバイアス電流を供給する第2トランジスタと、第1および第2トランジスタの制御端子間に接続され、抵抗素子として機能するスイッチ回路と、第2トランジスタの制御端子に接続される容量素子とを備えて構成される。電流源は、電圧制御発振器の起動状態時に第1トランジスタに対する電流供給動作を実施し、電圧制御発振器の定常状態時に第1トランジスタに対する電流供給動作を停止する。スイッチ回路は、電圧制御発振器の起動状態時にオンし、電圧制御発振器の定常状態時にオフする。

(もっと読む)

発振回路

【課題】 負性抵抗の減少を抑制することを目的とし、また、発振周波数付近で負性抵抗を選択的に増大させること。

【解決手段】 増幅器の出力から入力への帰還によって発振を行う発振回路において、発振回路が通常備える発振のための第1の帰還とは別に、振幅及び位相推移を行う第2の帰還の2重帰還を行うことによって、発振回路の負性抵抗を所望の周波数で増加させると共に、等価リアクタンス成分を調整する。発振回路は、コルピッツ発振回路が備える負性抵抗を生成する第1の帰還回路と、コルピッツ発振回路の発振段トランジスタのエミッタ端子からベース端子に電流帰還する第2の帰還回路とによって構成することができる。エミッタ端子からベース端子への電流帰還は帰還容量を介して行う。

(もっと読む)

発振回路

【課題】 VCO発振周波数の調整を容易にする。

【解決手段】 VCO用共振回路が接続されるボンディングパッド5下のエピタキシャル層2Aの電位を、従来のフローティング状態から抵抗6を介して所定(Vcc)電位に固定することで、エピタキシャル層2Aの電位変化を速くして、寄生容量値が速やかに安定することから、電源ON時のドリフトが改善する。

(もっと読む)

1 - 17 / 17

[ Back to top ]