Fターム[5J081CC44]の内容

LC分布定数、CR発振器 (9,854) | 目的、効果 (1,425) | 小型・軽量・簡易化 (291) | 省電力化 (66)

Fターム[5J081CC44]に分類される特許

1 - 20 / 66

発振装置

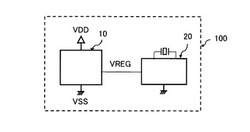

【課題】低消費電流を実現できる定電圧回路及びそれを用いた水晶発振回路を提供する。

【解決手段】定電圧回路10に温度特性調整素子を備えることにより、定電圧の温度変化に対して負となる傾きと、水晶発振回路20における発振可能な最低動作電圧の温度変化に対して負となる傾きとの差を極小にできるので、水晶発振回路20の消費電流を小さくでき、さらに定電圧回路10で生成する定電流を小さくすることにより、定電圧回路10の消費電流を小さくでき、発振装置100全体の消費電流を小さくできる。

(もっと読む)

回路装置及び電子機器

【課題】無駄な電力消費やノイズの悪影響等を抑制できる回路装置及び電子機器等の提供。

【解決手段】回路装置は発振回路10とバッファー回路20を含む。バッファー回路20は、プリバッファーPBFと第1、第2の出力バッファーQBF1、QBF2を含む。第1のモードでは、第1の出力バッファーQBF1が動作イネーブル状態に設定され、第2の出力バッファーQBF2が動作ディスエーブル状態に設定される。第2のモードでは、第1の出力バッファーQBF1及び第2の出力バッファーQBF2が動作イネーブル状態に設定される。第1のモードでは、プリバッファーPBFの駆動能力が、第2のモードに比べて低い駆動能力に設定される。

(もっと読む)

圧電発振器及びその動作方法

【課題】各種の電子機器の回路基板に搭載されて搭載後は外部電源からの導体接続での電力供給によって動作する水晶発振器などの圧電発振器であって、調整や検査の作業効率を向上させることができるものを提供する。

【解決手段】水晶振動子12などの圧電振動子と発振回路16とを収容した容器10内に二次電池21を設け、容器10には非接触給電による電力供給を受ける受電部13を設ける。受電部13で受電した電力によって二次電池21を充電し、電源端子に外部電源電圧Vccが印加されていないときには、二次電池21に充電された電力で発振回路16等を動作させる。

(もっと読む)

発振回路及び発振回路を搭載した電子機器

【課題】本発明の目的は、水晶発振回路の駆動電流が100nA以下と非常に小さくなり、水晶発振回路の出力が0.1Vpp以下と小さくなっても、水晶発振回路の出力に接続する次段の種々の回路が正常に動作する出力信号を出発振回路、及びそれを搭載した電子機器を提供する。

【解決手段】水晶発振回路の出力を増幅する増幅回路を水晶発振回路の出力側に接続し、水晶発振回路の出力電圧と水晶発振回路のCMOSインバータの入力電圧との差を増幅させる。たとえば、差動アンプを水晶発振回路の出力側に接続し、水晶発振回路の出力電圧とCMOSインバータの入力電圧とを差動アンプの入力とする。あるいは、3つのオペアンプから構成されるインスツルメンテーションアンプを水晶発振回路の出力側に接続し、水晶発振回路の出力電圧信号と水晶発振回路のCMOSインバータの入力電圧信号との差を増幅させる。

(もっと読む)

発振器

【課題】発振器の発振周波数、又は負荷の大小によるバッファー回路の出力レベル変動を抑制して、バッファー回路の消費電力を低減する発振器を提供する。

【解決手段】この発振器100は、発振回路18と、発振回路18の発振信号を増幅するプリバッファー回路19と、最終段のバッファー回路11と、バッファー回路11の出力電圧レベルを検出するレベル検出回路8と、レベル設定2に応じてレベル検出回路8のレベルを増幅する増幅回路1と、増幅回路1から出力したレベル検出回路8の検出レベルに基づいて出力信号(OUT)の電圧、又は電流を制御してバッファー回路11の出力レベルを調整するレベル調整回路5と、を備えて構成されている。

(もっと読む)

電圧制御発振器およびそれを用いた情報機器

【課題】周波数変換利得の変動が少ない発振器のためのLC共振回路、それを用いた発振器及び情報機器を提供する。

【解決手段】発振器のLC共振回路が、インダクタL1、第1の微調容量と第1の容量バンクからなる並列回路と、第2の微調容量と第2の容量バンクの直列容量とを含む。発振器の周波数変換利得は、第1の容量バンクの容量値が大きくなるに従い低下する第1の微調容量による発振器の周波数変換利得と、第2の容量バンクの容量値が大きくなるに従い増大する第2の微調容量による周波数変換利得の和となる。

(もっと読む)

磁気同調デバイス駆動回路及びそれを備えた測定装置並びに磁気同調デバイス駆動方法

【課題】小型化及び低消費電力化を図ることができる磁気同調デバイス駆動回路及びそれを備えた測定装置並びに磁気同調デバイス駆動方法を提供する。

【解決手段】磁気同調デバイス駆動回路10は、固定電圧を出力する電源に接続され、印加された出力電圧制御信号に応じた電圧を出力するスイッチング電源回路11と、スイッチング電源回路11の出力電圧を所望の同調周波数に応じた電流に変換して同調コイル51に供給する定電流回路12と、同調コイル51の電圧の絶対値を所定値だけ大きくするシフト電圧を供給するシフト電圧供給部13と、電流が供給された同調コイル51の電圧とシフト電圧とを加算し、加算後の電圧を出力電圧制御信号としてスイッチング電源回路11に出力する加算回路14と、を備える。

(もっと読む)

発振器、および発振を開始する方法

【課題】休止期間は消費電力を削減すると共に起動特性のよい発振器を提供する。

【解決手段】発振信号がコールドスタートからの規定の定常状態条件に達する時を早める回路を含んでいる発振信号を生成するための装置。装置は、発振信号を生成するための発振回路412と、前記発振回路に第1の電流を供給する第1の制御可能電流源404と、発振回路に第2の電流を供給する第2の制御可能電流源408と、を含み、第1および第2の電流は、発振信号が規定の定常状態条件に達するための時間分を縮小するのに適している。装置は、1以上の通信チャネルを確立するために低い負荷サイクルパルス変調を用いる通信システムに有益であるかもしれず、それによって装置はパルスのほぼ始めで発振信号を生成し始め、パルスのほぼ終わりに発振信号を終了する。

(もっと読む)

発振装置

【課題】水晶発振回路の消費電力の低減を図りつつ後段回路を作動させることができる発振装置を提供する。

【解決手段】第1電源V1が、振幅検出回路3に対して第1電源電圧(3V)を供給する。第2電源V2が、水晶振動回路2に対して第1電源電圧(3V)よりも小さい第2電源電圧(1V)を供給する。振幅検出回路3は、CMOSインバータIV1の出力端子から出力される発振信号と、第2電源電圧(1V)を分圧して得た基準電圧Vrefと、それぞれのベースに接続される一対のトランジスタが設けられたコンパレータ31を備えている。

(もっと読む)

発振器

【課題】少ない電流で必要な負性抵抗が得られることにより、安定に動作することのできる発振器を提供する。

【解決手段】互いに並列に配設された容量素子134,234およびインダクタ133,233を有する共振回路13,23と、共振回路13,23の損失を打ち消す負性抵抗が生じるように配設された複数のトランジスタを有する負性抵抗発生器14,24と、第1バイアス端子15,25と、第2バイアス端子16,26と、を備えた複数の発振部10,20と、各共振回路13,23が互いに等価的に並列に接続されるように、複数の発振部10,20を電気的に結合する結合部30Aと、を備え、複数の発振部10,20は、それぞれの第1バイアス端子25および第2バイアス端子16において互いに直列に接続され、複数の発振部10,20における複数のトランジスタ143,144,243,244は、互いに同じ導電型で構成されている。

(もっと読む)

発振回路

【課題】小型かつノイズ抑制に優れる発振回路を提供すること。

【解決手段】本発明にかかる発振回路100は、インバータ1及び2、タンク回路3を有する。タンク回路3は、出力ノードOUTTと出力ノードOUTBとの間に並列に接続される。インバータ1は、ドレインが出力ノードOUTBに接続されたn型MISトランジスタM1及びp型MISトランジスタM3を有する。インバータ2は、ドレインが出力ノードOUTTに接続されたn型MISトランジスタM2及びp型MISトランジスタM4を有する。p型MISトランジスタM3及びM4のゲート端子は、それぞれ出力ノードOUTT及びOUTBと直接的に接続される。n型MISトランジスタM1及びM2のゲート端子は、それぞれ結合容量CG1及びCG2を介して出力ノードOUTT及びOUTBと接続され、抵抗CG1及びCG2を介してバイアス電圧VBIASが印加される。

(もっと読む)

二重正帰還電圧制御発振器

【課題】低供給電圧の性能でのマイクロ波帯域における電圧制御発振器の効率を向上させるための二重正帰還電圧制御発振器を提供する。

【解決手段】2つのコルピッツ回路20、21は第1正帰還ループを提供し、第1負抵抗と等価である。NMOS交差結合ペア回路30は、第2正帰還ループを提供し第2負抵抗と等価である。2つのコルピッツ回路20、21及びNMOS交差結合ペア回路30によって生成される2つの各負抵抗は、LCタンクの寄生抵抗に対して並列に接続されている。この為2つの各負抵抗は、LCタンクの寄生抵抗をオフセットする。2つの各負抵抗が生成されるので、低電圧の稼動時において、及び、直流電流の共有において、高い負抵抗が二重正帰還電圧制御発振器10によって生成される。この為、二重正帰還電圧制御発振器10は、より低い電力下で発振可能である。

(もっと読む)

MEMSデバイス、電子機器

【課題】実装面積やコストを抑え、起動時間を短縮し、周波数精度の高いクロックも出力できるMEMSデバイス等を提供する。

【解決手段】 第1のクロック信号400と第2のクロック信号402の少なくとも一方を出力するMEMSデバイス100であって、同一の基板上に設けられた第1のMEMS共振子302を有する第1のMEMS発振器300と第2のMEMS共振子322を有する第2のMEMS発振器320とを含み、第1のMEMS発振器の共振周波数である第1の共振周波数と、第2のMEMS発振器の共振周波数である第2の共振周波数とは略一致し、第1のMEMS共振子のQ値と第2のMEMS共振子のQ値とは異なり、第1のMEMS発振器は、第1の共振周波数を周波数とする第1のクロック信号を出力し、第2のMEMS発振器は、第2の共振周波数を周波数とする第2のクロック信号を出力する。

(もっと読む)

周波数逓倍回路

【課題】入力振幅の大きさに依存することなく適切な発振振幅を得ることができる、消費電流が少なく、かつ簡略化された周波数逓倍回路を提供する。

【解決手段】CMOSインバータのPMOSFET21、NMOSFET22の少なくともどちらか一方に流れる発振電流を個々に制御する電流制御用素子23、24と、発振電流の交流成分のみを通過させる容量10、11と、容量10、11を通過した交流信号を加算処理して逓倍信号を出力する加算手段とから成り、加算手段は、電流制御用素子23、24とともに基準電圧によりオフセットされているため、CMOSインバータの各FETに流れる電流を任意に制限することができ、入力振幅の大きさに依存しない適切な発振振幅を得られる。

(もっと読む)

低位相ノイズ電圧制御発振器

本発明の形態は、消費電力を低減し位相ノイズ性能を向上させるために、電流再使用技術を用いた低位相ノイズ発振器回路を含み、発振器回路は、第2のVCOに結合されている第1のVCOを備え、第1及び第2のVCOの出力は、コンデンサ等の受動素子に結合されている。第1及び第2のVCO両方の全体の消費電力は、単一のVCOの消費電力と略同じである。また、位相ノイズは、約3dBほど低減される。このため、発振器回路の消費電力を増加させることなしに、位相ノイズ性能が向上される。 (もっと読む)

高電圧振幅状態の下での電圧制御発振器(VCO)バッファに対するデバイス信頼性の向上

電圧制御発振器(VCO)バッファのための回路が説明される。回路は、VCOコアと接続されるVCOバッファの入力と接続された第1のキャパシタを含む。回路は、また、VCOバッファの入力と、p型金属酸化膜半導体電界効果(PMOS)トランジスタのゲートとに接続された第2のキャパシタを含む。回路は、さらに、第1のキャパシタと、PMOSトランジスタのゲートとに接続された第1のスイッチを含む。回路は、また、VCOバッファの入力と接続された第3のキャパシタを含む。回路は、さらに、VCOバッファの入力と、n型金属酸化膜半導体電界効果(NMOS)トランジスタのゲートとに接続された第4のキャパシタを含む。回路は、また、第3のキャパシタとNMOSトランジスタのゲートとに接続された第2のスイッチを含む。 (もっと読む)

増幅器および発振器

【課題】MOSトランジスタの高周波領域におけるトランスコンダクタンスの劣化を招くことなく、低消費電力化を図ることが可能な増幅器などの提供。

【解決手段】この発明は、MOSトランジスタQ1などを含む増幅器である。MOSトランジスタQ1のゲートには第1の入力信号が入力され、MOSトランジスタQ1のバルクには第2の入力信号が入力され、MOSトランジスタQ1のソースから出力信号が出力される。そして、第1の入力信号と第2の入力信号とは同相の信号である。

(もっと読む)

発振回路

【課題】コンデンサへの充放電及び差動対を使用した発振回路において、回路規模や消費電力の増大を抑制しつつ安定した発振を可能とする。

【解決手段】トランジスタM10は、トランジスタM1,M2からなる差動対に定電流i1を供給する。M1には直列に抵抗R1が接続され、M1とR1との接続点の電位VBがM2のゲートに印加される。一方、M1のゲートには、定電流i2を生じるトランジスタM4と抵抗R2及びコンデンサC1の並列接続体との接続点の電位VAが印加される。M4は、M2のオフ期間に定電流i2を供給し、オン期間に定電流の供給を停止する。抵抗R2,R1それぞれの抵抗値をr2,r1として、(r1・i1)=(r2・i2)を満たすように設定する。

(もっと読む)

電圧制御発振器

【課題】低電源電圧の条件下にあっても、安定した発振の起動及び持続を保証しつつ低位相雑音化を達成することができる電圧制御発振器を提供する。

【解決手段】制御入力電圧に応じてインピーダンスが変化するLC並列共振回路と、該LC並列共振回路に負性抵抗を導入する負性抵抗回路と、を含む電圧制御発振器において、該負性抵抗回路が、該LC並列共振回路に並列に設けられ、キャパシタを介してクロスカップリングされた第一のトランジスタ対を有し、該第一のトランジスタ対の各トランジスタのゲートが第一のバイアス電圧にバイアスされて、C級増幅動作をする第一の増幅回路と、同様の回路構成を有し、各トランジスタのゲートが該第一のバイアス電圧と異なる第二のバイアス電圧にバイアスされて、C級増幅動作をする第二の増幅回路と、を少なくとも含む。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

1 - 20 / 66

[ Back to top ]