Fターム[5J081DD09]の内容

LC分布定数、CR発振器 (9,854) | 発振用能動素子とその接続 (1,031) | 複数素子の組合せ (353)

Fターム[5J081DD09]の下位に属するFターム

エミッタ・ソース・カソード共通接続 (234)

ベース・ゲート・グリッド共通接続 (3)

コレクタ・ドレイン・プレート共通接続 (3)

相補型 (18)

縦続接続 (32)

並列・直列 (29)

Fターム[5J081DD09]に分類される特許

1 - 20 / 34

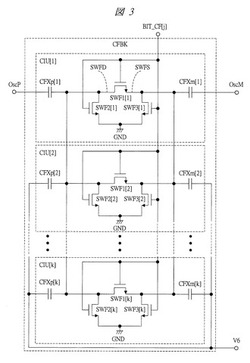

ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

(もっと読む)

発振回路

【課題】コンパレータの消費電力を抑えつつ、高周波の発振出力の振幅を検出できる、発振回路を提供すること。

【解決手段】水晶振動子1を共振器として使用して発振出力Vxを生成する発振出力生成回路11と、発振出力Vxの振幅を検出する振幅検出回路15と、振幅検出回路15の出力Vsに応じて発振出力Vxをブーストするブースト回路16とを有する発振回路であって、振幅検出回路15は、発振出力Vxが入力される絶対値回路12と、絶対値回路12の出力を入力とするローパスフィルタ13と、ローパスフィルタ13の出力を入力とするコンパレータ14とを備えることを特徴とする、発振回路。

(もっと読む)

発振回路及び発振回路を搭載した電子機器

【課題】本発明の目的は、水晶発振回路の駆動電流が100nA以下と非常に小さくなり、水晶発振回路の出力が0.1Vpp以下と小さくなっても、水晶発振回路の出力に接続する次段の種々の回路が正常に動作する出力信号を出発振回路、及びそれを搭載した電子機器を提供する。

【解決手段】水晶発振回路の出力を増幅する増幅回路を水晶発振回路の出力側に接続し、水晶発振回路の出力電圧と水晶発振回路のCMOSインバータの入力電圧との差を増幅させる。たとえば、差動アンプを水晶発振回路の出力側に接続し、水晶発振回路の出力電圧とCMOSインバータの入力電圧とを差動アンプの入力とする。あるいは、3つのオペアンプから構成されるインスツルメンテーションアンプを水晶発振回路の出力側に接続し、水晶発振回路の出力電圧信号と水晶発振回路のCMOSインバータの入力電圧信号との差を増幅させる。

(もっと読む)

アナログ回路

【課題】高い歩留りを得ながらゲートスロープを抑制することができるアナログ回路を提供する。

【解決手段】アナログ回路には、発振トランジスタ27と、発振トランジスタ27に対する負性抵抗を変更する負性抵抗変更回路と、が設けられている。負性抵抗変更回路には、可変抵抗回路及び可変容量回路が含まれている。可変抵抗回路には、抵抗体29、抵抗体31及びトランジスタ(スイッチ)35が含まれ、可変容量回路には、キャパシタ30及び可変容量ダイオード36が含まれている。

(もっと読む)

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

発振器

【課題】負荷容量に応じて最適な波形を出力可能な発振器を提供する。

【解決手段】発振回路12からの出力を、出力バッファ(前段出力バッファ14、出力バッファ22)を介して負荷回路に出力する発振器10であって、発振器10は、出力バッファ22の駆動能力を出力バッファから流れる電流に応じて調整可能なバッファ制御回路48を有する。ここで出力バッファ22は、発振回路12の後段に複数並列に接続されるとともに、バッファ制御回路48は、出力バッファから流れる電流に応じて出力バッファ22の稼動数を調整する信号を出力バッファ22に出力することにより出力バッファ22の駆動能力を調整している。

(もっと読む)

発振制御回路

【課題】発振開始時からデューティが50%に安定する発振制御回路を提供する。

【解決手段】作動制御回路3が、発振信号の発振電位がCMOSインバータIV1の反転電位よりも低い第1基準電位よりも低くなるまでMOSトランジスタT11及びT12をオフ状態、MOSトランジスタT2をオン状態に保持する。作動制御回路3が、発振信号の発振電位が第1基準電位よりも低くなったとき出力が反転するCMOSインバータIV31と、CMOSインバータ31の後段に設けた抵抗R31とコンデンサC31とからなるローパスフィルタ31と、ローパスフィルタ31の出力が閾値を越えると出力が反転するCMOSインバータ33と、を有している。

(もっと読む)

発振器及びそれを用いた周波数生成回路並びに無線通信システム

【課題】LC型発振器において、高調波歪みによる位相雑音の劣化が小さく、かつ発振振幅の増大化を図り、これにより良好な低位相雑音特性を有する発振器及びそれを用いた通信システムを提供する。

【解決手段】トランジスタからなる少なくとも1つ以上の電圧-電流変換部と、1対の容量性素子と誘導性素子からなるLCタンクを2つ有している共振器とを具備して成り、前記の電圧-電流変換部の出力端子は、前記の共振器に接続され電流-電圧変換されたのちに、前記電圧-電流変換部の入力端子に接続されることにより、帰還ループが構成されて成り、前記共振器を構成している2つのLCタンクを構成する誘導性素子が相互誘導結合されており、前記相互結合係数がおおよそ-0.6であることを特徴とする。

(もっと読む)

集積電圧制御発振器回路

改善した位相ノイズ性能と、より低い電力消費とを有する電圧制御発振器を提供する技術である。例示的な実施形態では、電圧制御発振器(VCO)は、混合器に、または、2分周器のような周波数分周器に結合されている。VCOは、磁気的にクロス結合されているインダクタを有するトランジスタ対と、トランジスタ対のゲートに結合されている可変キャパシタンスとを備える。例示的な実施形態では、周波数分周器は、トランジスタ対を通って流れる差動電流の周波数を分周して、LO出力を発生させるように構成されている。代替的で例示的な実施形態では、混合器は、トランジスタ対を通って流れる差動電流を別の信号と混合するように構成されている。VCOと、混合器または周波数分周器は、通常バイアス電流を共有し、したがって、電力消費を減少させる。これらの技術を利用するさまざまな例示的な装置および方法を開示する。 (もっと読む)

電子回路

【課題】電子回路(例えば、マイクロコンピュータ)の動作モードに応じて、低周波数の発振器について適切な電源インピーダンスを設定することにより、前記発振器の誤動作を防止しながら、消費電力を適切に低減することができる。

【解決手段】システムクロックのクロック源として、高速発振器11、中速発振器12、低速発振器13が設けられる。また、時計用クロックを発生する水晶発振器30が設けられる。そして、高速発振器11が動作している時は、水晶発振器30の電源インピーダンスを低くして、耐ノイズ性を高める。一方、高速発振器11、中速発振器12、低速発振器13がすべて停止している待機時には、水晶発振器30の電源インピーダンスを高くして消費電力を抑える。

(もっと読む)

電圧制御発振回路

【課題】製造コストの追加なく一般的に用いられる可変容量素子を利用し、位相雑音特性に優れたRTW形式の電圧制御発振回路を実現できるようにする。

【解決手段】電圧制御発振回路は、ループ状の伝送線路15と、信号線路と接続されたアクティブ回路17と、信号線路と接続され複数の可変容量ユニット23を有する可変容量部21とを備えている。各可変容量ユニット23は、可変容量素子31と、可変容量素子31に制御電位を印加する制御端子41と、可変容量素子31に基準電位を印加する基準電位端子43とを有している。少なくとも2つの可変容量ユニット23は、基準電位が互いに異なっている。

(もっと読む)

発振回路

【課題】特にLC発振回路において、インダクタをトランス構造とし、1次側の発振による交流信号を2次側より効率的に取り出し、整流した後に、発振回路の電源に帰還させ、省電力化及び電源を供給しない発振継続を可能とする発振回路を提供する。

【解決手段】所定の飽和時の共振条件を満たし、逆流防止回路を通して直流電源に接続され、第一のインダクタL1とトランス構造を構成する第二のインダクタL2と、第一のインダクタL1と直列に接続された第一のコンデンサC1と、第二のインダクタL2と直列に接続された第二のコンデンサC2と、を備え、第二のインダクタL2から出力された交流電流を整流し発振回路の電源に帰還させ省電力化及び発振継続を可能とする発振増幅器を提供する。これにより、LC発振回路において、電源を切断した後の発振回路の発振継続、あるいは発振回路の低消費電力化、あるいは外部への電力供給が可能となる。

(もっと読む)

電圧制御発振器

【課題】VCO利得の変動を抑圧した簡易な構成のVCOの提供。

【解決手段】二つの周波数可変手段を具備することでマルチバンド動作を行なう電圧制御発振器(VCO)において、可変容量素子11iaと12ia及び11ibと12ib(i=1、2、3)をそれぞれ互いに極性が逆になる向きに並列接続可能とし、可変容量素子対を形成する。一般に、可変容量素子11iaと12ia、11ibと12ib(i=1、2、3)の容量値は異なる値に設定される。これらの可変容量素子対は、ループコントロール端子3に印加されるコントロール電圧VCNTにより制御されると同時に、帯域設定信号VSW1、VSW2、VSW3によってオンオフされるスイッチ素子であるトランジスタ101a、102a、103a、101b、102b、103bの切替により、VCO本体に電気的に分離・接続される。

(もっと読む)

電圧制御型可変周波数発振回路および信号処理回路

【課題】可変容量素子の容量可変域に応じた広い周波数可変域を確保することができる電圧制御型可変周波数発振回路を提供する。

【解決手段】コイルL1,L2および可変容量素子111,112を有する共振回路101と、負性抵抗回路102とを含む発振回路部103を備える電圧制御型可変周波数発振回路である。発振回路部103と電源電位VDDとの間に第1の抵抗301を設ける。また、発振回路部と接地電位端との間には第2の抵抗302を接続するとよい。

(もっと読む)

発振回路

【課題】温度補償回路に発振部の出力がノイズとして入力しない発振回路を提供する。

【課題の解決手段】周囲温度に応じた制御信号によって出力周波数が制御される発振部1と、この発振部1に制御信号を供給する温度補償回路2と、発振部1の発振出力と温度補償回路2の温度センサ出力のいずれかを出力するようオンオフ制御される出力バッファ4と温度センサ出力スイッチ3からなる切換スイッチ回路とを備え、温度センサ出力スイッチ3は、トランスファーゲートスイッチ301,302を2段直列に接続し、この接続点に固定電位に接続した第3のスイッチ303を介在させてなり、発振出力を出力する時はトランスファーゲートスイッチ301,302をオフとして、第3のスイッチ303をオンとし、温度センサ出力を出力する時はトランスファーゲートスイッチ301,302をオンとして、第3のスイッチ303をオフとする。

(もっと読む)

発振周波数制御方法及び発振器

【課題】温度によって変化する発振周波数を、応答性良く、正確に、所定の周波数に調整することができる発振周波数の制御方法及び発振器を提供する。

【解決手段】本発明の発振周波数制御方法は、発振周波数及び出力信号の振幅が温度に依存して変化し、所定の発振周波数制御信号を用いて発振周波数の変更が可能な発振器の発振周波数制御方法であって、振幅を測定する工程と、振幅に基づき発振周波数制御信号を制御し、発振周波数を変更する工程を備える。また、本発明の発振器は、発振周波数及び出力信号の振幅が温度に依存して変化し、所定の発振周波数制御信号を用いて発振周波数の変更が可能な発振器であって、振幅を測定する振幅測定部と、振幅に基づき発振周波数制御信号を制御し、発振周波数を変更する温度補償部を備える。

(もっと読む)

電圧制御発振器、PLL回路

【課題】 低周波の発振信号であっても安定して出力することが可能な電圧制御発振器及びPLL回路を提供する。

【解決手段】 本発明に係る電圧制御発振器1は、インダクタ4及び可変キャパシタ5を有するLC共振回路2と、複数の負性抵抗回路NR1、NR2、…、NRnを備える。各負性抵抗回路NR1、NR2、…、NRnは、定電流源CG1、CG2、…、CGnを介して夫々接地線と接続される構成であり、各定電流源は、夫々個別に導通状態(一定電流を流す状態)と非導通状態(開放された状態)との間で切換制御が可能に構成されており、本発明に係る電圧制御発振器1は、これらの各定電流源の導通制御を行うための制御手段7を備える構成である。

(もっと読む)

出力回路を備えた発振回路

【課題】電源電圧を低電圧化した場合においても、発振回路の最終出力波形のデューティー比を50%に調整し易く、且つ、種々の外乱要因によってもデューティー比の変動を少なく抑えることが可能な発振回路を提供する。

【解決手段】振動子、増幅回路及び出力回路を含む発振回路であって、前記増幅回路の入力端子に接続される側の前記振動子の端子と、前記出力回路の入力端子とが接続され、振動子の前記端子と、増幅回路の前記入力端子とが容量を介して接続され、さらに、振動子の前記端子側に、所定の電位をバイアスするためのバイアス回路が接続されている。

(もっと読む)

雑音除去を有するループフィルタ

【解決手段】 ループフィルタは、第1及び第2の信号経路720,730、演算増幅器(オペアンプ)736及び雑音除去経路740を含む。第1の信号経路720は、第1の信号に第1の伝達関数を供給する。第2の信号経路730は、第2の信号に第2の伝達関数を供給する。第2の信号は、第1の信号のスケール化バージョンである。キャパシタ734は、因子アルファだけ小さくスケールされる。オペアンプは、第1及び第2の信号経路に結合され、オペアンプ雑音を有する制御信号VCTRLを生成するために第1及び第2の信号経路からの信号を合計することを容易にするように形成される。雑音除去経路740は、オペアンプに結合され、制御信号中のオペアンプ雑音を相殺するのに使用される雑音除去信号VCTRLを生成する。制御信号VCTRL及び雑音消去信号VNは、電圧制御発振器(VCO)内に含まれるバリキャップ750の各ノードに適用される。 (もっと読む)

1 - 20 / 34

[ Back to top ]