Fターム[5J081DD29]の内容

LC分布定数、CR発振器 (9,854) | 発振用能動素子とその接続 (1,031) | 副次的素子・回路(発振用回路) (46) | 負性抵抗 (45)

Fターム[5J081DD29]に分類される特許

1 - 20 / 45

ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

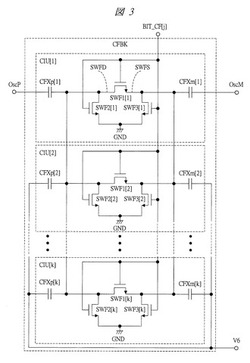

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

(もっと読む)

発振回路

【課題】簡易な方法で、特性の劣化を抑制し発振周波数を調整することが可能な発振回路を提供すること。

【解決手段】一対の負性抵抗回路と、前記一対の負性抵抗回路にそれぞれ接続された一対の伝送線路14a、14bと、前記一対の伝送線路にそれぞれ対称に設けられ、前記一対の伝送線路の間をボンディングワイヤによって互いに接続可能な一対のパッド40a、40bと、前記一対の負性抵抗回路の出力信号を合成する合成回路と、を有する発振回路。

(もっと読む)

電圧制御発振器

【課題】良好な位相雑音特性を有し、かつ広帯域な発振周波数範囲を有する電圧制御発振器を提供することを目的とする。

【解決手段】本発明に係る電圧制御発振器1は、電源と、少なくとも3つのポート10a〜10dを備えるインダクタ11と、少なくとも3つのポートから選択される異なるポート対にそれぞれ接続される少なくとも2つの負性抵抗回路12及び14と、を有し、インダクタは、少なくとも2つの負性抵抗回路に接続されるポート対の間でそれぞれインダクタとして動作可能であることを特徴とする。

(もっと読む)

電圧制御発振器

【課題】増幅用のトランジスタに帰還容量成分C1及び結合容量成分C2の直列回路を接続したコルピッツ発振回路を用いた電圧制御発振器において、部品点数の削減に寄与できる技術を提供すること。

【解決手段】トランジスタ21のベースに接続された第1の伝送線路41とトランジスタ21のエミッタとアースとの間に接続された第2の伝送線路42と、を備え、第1の伝送線路41及び第2の伝送線路42を互いに接近させて両者の間に線路間容量成分を形成する。この線路間容量成分を前記帰還容量成分C1として利用すると共に第2の伝送線路42とアースとの間に形成される寄生容量成分を前記結合容量成分C2として利用する

(もっと読む)

電圧制御発振器およびそれを用いた情報機器

【課題】周波数変換利得の変動が少ない発振器のためのLC共振回路、それを用いた発振器及び情報機器を提供する。

【解決手段】発振器のLC共振回路が、インダクタL1、第1の微調容量と第1の容量バンクからなる並列回路と、第2の微調容量と第2の容量バンクの直列容量とを含む。発振器の周波数変換利得は、第1の容量バンクの容量値が大きくなるに従い低下する第1の微調容量による発振器の周波数変換利得と、第2の容量バンクの容量値が大きくなるに従い増大する第2の微調容量による周波数変換利得の和となる。

(もっと読む)

アナログ回路

【課題】高い歩留りを得ながらゲートスロープを抑制することができるアナログ回路を提供する。

【解決手段】アナログ回路には、発振トランジスタ27と、発振トランジスタ27に対する負性抵抗を変更する負性抵抗変更回路と、が設けられている。負性抵抗変更回路には、可変抵抗回路及び可変容量回路が含まれている。可変抵抗回路には、抵抗体29、抵抗体31及びトランジスタ(スイッチ)35が含まれ、可変容量回路には、キャパシタ30及び可変容量ダイオード36が含まれている。

(もっと読む)

2出力直交ローカル信号発振器

【課題】90°の位相差を持つ2つのローカル信号を発生するローカル信号源として使用可能な2出力直交ローカル信号発振器の提供。

【解決手段】第1及び第2のトランジスター14及び15を有し、共振器20を共有することにより、基本発振周波数にてプッシュ−プッシュ発振動作を行い、第1及び第2のトランジスターの一方から第1のローカル信号を出力する第1のプッシュ−プッシュ型発振器18と、第3及び第4のトランジスター16及び17を有し、共振器20を共有することにより、前記基本発振周波数にてプッシュ−プッシュ発振動作を行い、第3及び前記第4のトランジスターの一方から第2のローカル信号を出力する第2のプッシュ−プッシュ型発振器19とを有し、第1及び第2のプッシュ−プッシュ型発振器は、共振器の直交共振モードによって直交発振動作を行い、90°の位相差のある直交ローカル信号を出力することを特徴とする2出力直交ローカル信号発振器。

(もっと読む)

電子回路

【課題】負性抵抗回路において反射特性を向上させること。

【解決手段】制御端子、第1端子および第2端子を有する第1トランジスタとQ1、前記第1トランジスタの前記第2端子に接続された制御端子、第1端子およびDC電源が接続される第2端子を有する第2トランジスタQ2と、前記第1トランジスタの前記第1端子と前記第2トランジスタの前記第1端子との信号を前記第1トランジスタの制御端子に共通に帰還させる正帰還回路22と、前記第2トランジスタの前記第1端子と前記正帰還回路との間に接続された第1キャパシタC1と、前記第1トランジスタの前記第2端子と前記第2トランジスタの前記制御端子との間の第1ノードN1と、前記第2トランジスタの前記第1端子と前記第1キャパシタとの間の第2ノードN2と、をDC的に接続する経路12と、を具備する電子回路。

(もっと読む)

電圧制御発振回路

【課題】電圧制御発振回路の回路規模の増大を抑制する。

【解決手段】電圧制御発振回路は、発振信号を増幅する発振アンプ部32と、発振信号の発振周波数を制御するLC共振部33と、負性抵抗成分を有する負性抵抗部34と、を備える。LC共振部33は、ループ状に接続されたgmセル25,26と、ループ上のノードに一端が接続された容量28〜31と、を有し、gmセル25,26と容量28,29とに基づくインダクタンス値と、容量30,31の容量値と、に基づいて発振周波数を制御する。

(もっと読む)

電圧制御発振回路

【課題】簡単な回路構成で応答性をよくし、切り替えられる発振信号の各周波数で同一電圧振幅を得られる電圧制御発振回路を提供する。

【解決手段】LCタンク回路1に第1及び第2のキャパシタ群11,12を備える、第1及び第2のキャパシタ群11,12はそれぞれ2つのキャパシタC1,C2を備える。負性コンダクタンス部2により、LCタンク回路1の共振信号をフィードバックして相互180°の位相差を有する2つの発振信号を生成し、2つの出力端out1,out2から出力する。電流源31,32からなる電流源3から負性コンダクタンス部2を介してLCタンク回路1に電流を供給する。制御信号を、CMOSスイッチからなる電流源スイッチ4,第1キャパシタスイッチ5及び第2キャパシタスイッチ6に与え、電流源群3から供給する電流とLCタンク回路1のキャパシタンスを切り替える。

(もっと読む)

キャパシタスイッチング回路

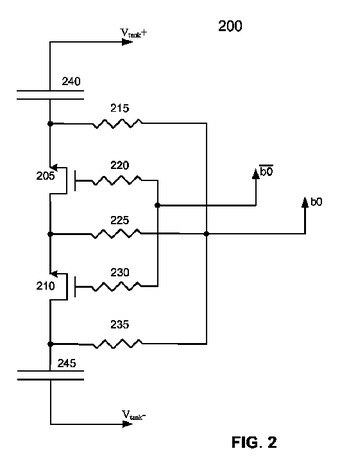

キャパシタンススイッチング素子(200)が、トランジスタ(205、210)によって直列に接続された、第1のキャパシタ(240)と第2のキャパシタ(245)とを含む。トランジスタのゲートは、一組の抵抗器(220、230)を介して第1の信号(b0/)によってバイアスをかけられ、ソースおよびドレインは、第2の組の抵抗器(215、225、235)を介して第2の信号(b0)によってバイアスをかけられる。信号はレベルシフトされており、相補的であってよい。素子をオンにするためには、第1の信号(b0/)をVDDに設定することができ、第2の信号(b0)をゼロに設定することができる。素子をオフにするためには、第1の信号(b0/)をVDD/2の倍数に設定することができ、第2の信号(b0)をVDD/2の倍数プラス1(the multiple plus one)に設定することができる。素子が発振器同調回路で使用されるとき、トランジスタの圧力ストレスが低減され、トランジスタを薄酸化物で製作することができる。発振器は、セルラアクセス端末のトランシーバにおいて使用されてもよい。  (もっと読む)

(もっと読む)

発振回路

【課題】高周波発振であっても安定した発振を行なえる。

【解決手段】発振回路1は、圧電振動子を所定の周波数で励振させる発振回路部を備え、発振回路部の等価回路ECは、負性抵抗RLと容量性リアクタンスCLが直接接続された直列モデルで構成されている。発振回路部の一方の端子ECAにコイルLSの一方の端子が直列接続され、発振回路部の他方の端子ECBとコイルLSの他方の端子との間に抵抗RPが並列接続されている。コイルLSの他方の端子と抵抗RPの一方の端子との接続点が、圧電振動子との接続を行う一方の圧電振動子接続用端子Aとされ、抵抗RPの他方の端子と発振回路部の他方の端子ECBとの接続点が、圧電振動子との接続を行う他方の圧電振動子接続用端子Bとされている。また、抵抗RPの絶対値は、負性抵抗RLの絶対値よりも大きい。

(もっと読む)

可変インダクタ及び電圧制御発振器

【課題】LCの並列共振による電圧制御発振器を構成するための可変インダクタであって、小型かつQ値の劣化を抑制した、複数周波数発振可能な可変インダクタを提供すること。

【解決手段】可変インダクタ100は、線対称軸Y−Y’を有し、Y−Y’上の点Bを通るY−Y’に関して線対称なインダクタ部Ind1及びInd2を備える。インダクタ部Ind2は、点B以外でインダクタ部Ind1と交わらず、インダクタ部Ind1及びInd2は共に曲線のみで構成される。インダクタ部Ind1の線路長はInd2の線路長よりも短い。Ind1は、Y−Y’上の点Z1を中心点とした円周上の円弧で構成され、端子D’から点Bを通って端子D’とY−Y’に関して線対称な端子D’’まで延在する。Ind2は、Y−Y’上の点Z2を中心点とした円周上の円弧で構成され端子E’から点Bを通って端子E’とY−Y’に関して線対称な端子E’’まで延在する。

(もっと読む)

位相同期発振器アレイ及びアレイアンテナ装置

【課題】分配器を用いることなく、位相同期した多数の発振信号を供給すること。

【解決手段】発振信号の位相差が90度である4位相の同一周波数の発振信号を出力する位相同期発振器アレイである。複数の閉線路21〜23から成る複数のリング共振器と、閉線路の全長を1/4分割した位置に設けられた4つのポート21a〜21dのうち隣接する2つのポート21b、21cと、この閉線路21に隣接する閉線路22の隣接する2つのポート22a、22d間を、それぞれ、負性抵抗として、接続する差動発振器31a、31bと、少なくとも何れか1方の端部に配置される閉線路21において、その閉線路の4つのポートのうち、差動発振器が接続されていない2つのポート21a、21dに対して、90度の位相差を有した信号を励振する励振装置30とを有する。

(もっと読む)

電圧制御発振器

【課題】VCO利得の変動を抑圧した簡易な構成のVCOの提供。

【解決手段】二つの周波数可変手段を具備することでマルチバンド動作を行なう電圧制御発振器(VCO)において、可変容量素子11iaと12ia及び11ibと12ib(i=1、2、3)をそれぞれ互いに極性が逆になる向きに並列接続可能とし、可変容量素子対を形成する。一般に、可変容量素子11iaと12ia、11ibと12ib(i=1、2、3)の容量値は異なる値に設定される。これらの可変容量素子対は、ループコントロール端子3に印加されるコントロール電圧VCNTにより制御されると同時に、帯域設定信号VSW1、VSW2、VSW3によってオンオフされるスイッチ素子であるトランジスタ101a、102a、103a、101b、102b、103bの切替により、VCO本体に電気的に分離・接続される。

(もっと読む)

電圧制御型可変周波数発振回路および信号処理回路

【課題】可変容量素子の容量可変域に応じた広い周波数可変域を確保することができる電圧制御型可変周波数発振回路を提供する。

【解決手段】コイルL1,L2および可変容量素子111,112を有する共振回路101と、負性抵抗回路102とを含む発振回路部103を備える電圧制御型可変周波数発振回路である。発振回路部103と電源電位VDDとの間に第1の抵抗301を設ける。また、発振回路部と接地電位端との間には第2の抵抗302を接続するとよい。

(もっと読む)

電圧制御発振器

【課題】定電流源が有する雑音、電流の増幅及び折り返しのために使用するカレントミラー回路で発生するトランジスタのショット雑音並びにフリッカー雑音の影響を排除することができる共振型の電圧制御発振器を得る。

【解決手段】可変抵抗制御回路12の第1制御回路部21で生成された第1制御信号SR[n−1:0]を可変抵抗7に出力すると共に、可変抵抗制御回路12の第2制御回路部22で生成された第2制御信号DR[m−1:0]を可変抵抗8に出力することにより、発振回路11は、定電流源を有することなく消費電流が一定になり、所望の動作点を得ることができ、定電流源が有する雑音、電流の増幅及び折り返しのために使用するカレントミラー回路で発生するトランジスタのショット雑音並びにフリッカー雑音の影響を排除することができるようにした。

(もっと読む)

電圧制御発振器、電圧並びにバイアス設定方法

【課題】位相雑音とDCバイアス電流特性上第1領域にて動作させることで安定した位相雑音特性を有する電圧制御発振器を得る。

【解決手段】インダクタL1、L2と可変容量素子M1、M2からなるLCタンク回路と負性抵抗を発生するバイポーラトランジスタQ1、Q2とを備える電圧制御発振器にあって、バイポーラトランジスタQ1、Q2のコレクターエミッタ間電圧VcEは、発振動作中バイポーラトランジスタのベースーエミッタ間電圧VBE以上であり、しかもバイポーラトランジスQ1、Q2タのトランジスタ耐圧BVCEO以下とするようにした。

(もっと読む)

LC発振器

【課題】発振信号の対称性などの制約が要求される場合においても、その制約を制御する自由度を向上させることができるLC発振器を提供する。

【解決手段】LC発振器は、並列に接続された第1のインダクタおよびキャパシタからなるLCタンク、ならびに、寄生抵抗の影響を打ち消す第1の負性抵抗回路を含む1次側のLC発振器と、相互インダクタンスを発生する相互誘導作用によって第1のインダクタと結合された第2のインダクタおよび第2の負性抵抗回路を含む2次側のLC発振器とを備える。ここで、第1および第2の負性抵抗回路の抵抗値の合計は、寄生抵抗の抵抗値以上であり、逆極性である。

(もっと読む)

発振器の製造方法、及び発振器

【課題】共振状態における電磁波損失が低減され、出力を向上させることが可能な発振器の製造方法、及びその発振器を提供することである。

【解決手段】発振器の製造方法により、発振電磁波に対して利得を有する利得媒質202と電磁波を共振させるための共振器構造を備え、共振器構造が電磁波の伝播方向と垂直な方向を閉じ込めるための導波管構造を有する発振器が製造される。第1の基板200に、利得媒質202を含む半導体多層膜をエピタキシャル成長する。第1の基板200、または第1の基板とは別の第2の基板209に、当該溝205の断面形状で規定されるカットオフ周波数が電磁波の周波数より小さくなる様な形状の溝205を形成する。第1の基板200と第2の基板209によって溝205が挟まれて導波管構造を構成する様に第1の基板と第2の基板を貼り合わせる。

(もっと読む)

1 - 20 / 45

[ Back to top ]