Fターム[5J081EE04]の内容

LC分布定数、CR発振器 (9,854) | 周波数決定素子 (1,325) | 集中定数 (802) | R (43)

Fターム[5J081EE04]に分類される特許

1 - 20 / 43

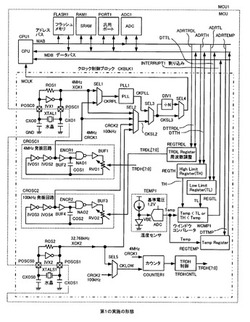

発振回路を有するマイクロコントローラ

【課題】複雑なバイアス回路を使用せず,抵抗の温度依存性を補償可能なMCU搭載に適したCR発振回路またはLC発振回路を提供する。

【解決手段】マイクロコントローラは,CPUと,CPUに供給するクロックを生成しクロックの周波数が周波数調整信号に応じて可変制御される発振回路と,温度を検知する温度センサと,温度センサにより検知される温度が所定温度変動したことに応答してCPUにより実行される周波数調整プログラムと,周波数調整信号と発振回路の発振周波数との関係を示す調整信号対周波数関係データと,温度と前記発振回路の発振周波数との関係を示す温度対周波数関係データとを格納するメモリとを有する。そして,周波数調整プログラムがCPUにより実行されることで,CPUが,温度対周波数関係データと調整信号対周波数関係データとに基づいて,温度センサにより検知される現在温度に応じて,発振回路の発振周波数を目標の周波数に制御する周波数調整信号を演算し,演算した周波数調整信号が発振回路に設定される。

(もっと読む)

CR発振回路およびその周波数補正方法

【課題】基準周波数信号を用いることなく、温度変動、電源電圧変動および回路定数のばらつきにかかわらず高精度な発振周波数を得る。

【解決手段】出荷検査時において、発振動作の環境温度と電源電圧を変化させながら発振周波数が目標周波数に一致するのに必要な抵抗5の抵抗値を順次求め、環境温度と電源電圧に対して当該抵抗値を対応付けたデータテーブルをメモリ18に記憶する。CR発振回路の実際の使用状態では、制御回路17は、所定の制御周期ごとに温度検出回路15と電源電圧検出回路16から電圧Va、Vbを入力しA/D変換する。メモリ18に予め記憶されたデータテーブルから電圧Va、Vbに対応した抵抗5の抵抗値を読み出し、抵抗5の抵抗値Rが当該読み出した指定値に等しくなるようにスイッチ7a〜7cを切り替える。

(もっと読む)

周波数自動調整機能付自励発振回路およびそれを用いた半導体集積回路

【課題】自励発振回路周辺の状態変化による発振周波数の変化を抑えることができる周波数自動調整機能付自励発振回路およびそれを用いた半導体集積回路を提供する。

【解決手段】周波数自動調整機能付自励発振回路は、基準信号を生成する基準信号生成回路101bと、基準信号の周波数を調整する発振周波数調整回路101aとを有する自励発振回路101と、互いに特性の異なる1組の抵抗素子を含み、1組の抵抗素子の抵抗値の変化の違いにより自励発振回路101の周辺状態を検出し、検出された周辺状態を示す信号を出力する特性変動検出回路102_1と、特性変動検出回路102_1の出力信号に基づいて発振周波数調整回路101aによる周波数調整を制御する制御部103とを備える。

(もっと読む)

改良された帯域幅を備える電圧制御発振器を有する位相同期ループ回路

【課題】改良された電圧制御発振器を提供する。

【解決手段】電圧制御発振器(16)は複数の直列に接続された合成利得段(42、44、46)を含む。合成利得段はトランスコンダクタンス段(48)及びトランスインピーダンス段(50)を含む。トランスコンダクタンス段は第1電源電圧端子から第2電源電圧端子への第1電流経路(52、56、64)及び第2電流経路(54、58、66)を有する。第1可変抵抗(62)は第1電流経路と第2電流経路との間に接続される。トランスインピーダンス段は、第1電流経路の出力に接続された入力端子と、出力端子とを有する第1インバータ(68、72)及び第2電流経路の出力に接続された入力端子と、出力端子とを有する第2インバータ(70、74)を有する。第2可変抵抗(76)は第1インバータの入力端子と出力端子との間に、第3可変抵抗(78)は第2インバータの入力端子と出力端子との間に接続される。

(もっと読む)

発振周波数補正装置

【課題】同期信号の検出が困難なときにも正確な発振周波数のクロック信号を生成できるようにした発振周波数補正装置を提供する。

【解決手段】電源投入時の劣化検出タイミングにおいて、定電流源23から抵抗器22に通電して得られたA/D変換器6のAD変換値(抵抗器22の端子電圧VR)に基づいて、CPU2が逓倍数設定値FMULRを補正する。この場合、定電流源20を用いることなく定電流源23が作動して抵抗器22に通電する。CPU2は、抵抗器22の端子電圧を測定することでCR発振器14内の抵抗器R1の抵抗値の経年変化を反映し、この変化に基づいてCR発振回路8のクロック信号CLKの逓倍数設定値FMULRを補正する。

(もっと読む)

圧電発振器

【課題】安定駆動に達するまでの時間を短縮した圧電発振器を提供する。

【解決手段】本発明の水晶発振器(圧電発振器)50は、水晶振動子(圧電振動子)1と、水晶振動子1に接続されて発振ループを形成して発振信号を出力する水晶発振部(圧電発振部)24、及び水晶発振部24の起動時に自励発振する自励発振部25により構成された発振回路と、を備え、自励発振部25の周波数が水晶発振部24の周波数よりも高く設定されている。尚、自励発振部25は、複数のコンデンサー(容量素子)C、インバーター5及び抵抗素子4により構成され、複数のコンデンサーCの合成容量の値を調整するために、調整手段6を備えている。

(もっと読む)

発振周波数補正信号発生回路

【課題】発振周波数とは別の周波数を生成するための回路を別途設けることなく、発振周波数を補正することができるようにする発振周波数補正信号発生回路を提供する。

【解決手段】発振信号を互いに異なる遅延時間にて遅延させて複数の遅延信号を生成し、当該遅延信号の各々に基づくタイミングにて当該発振信号を1周期単位でサンプリングして周期毎のサンプル値群を生成し、互いに異なる時点の2つの測定対象周期における当該サンプル値群の一連のサンプル値を比較してその比較結果に応じて前記補正信号を生成する。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

可変容量素子

【課題】従来の可変容量素子は、容量値の精度が低い問題があった。

【解決手段】本発明の可変容量素子は、第1の電源端子と出力端子CTOPとの間に接続される第1の容量素子C1と、容量切替信号CSELに応じて導通状態が切り替えられる容量選択スイッチN1と、第1の容量素子C1と並列に接続され、かつ、容量選択スイッチN1と直列に接続される第2の容量素子C2と、容量選択スイッチN1が遮断状態とされる状態において、出力端子CTOPをリセット電圧にリセットする電荷リセット信号INITBに応じて、第2の容量素子C2と容量選択スイッチN1とを接続する容量切替ノードNDaの電圧と出力端子CTOPの電圧とを実質的に同じ電圧に設定する誤差補正回路10と、を有する。

(もっと読む)

発振器

【課題】後段にフィルタを挿入しなくても、低歪みの発振波形を得ることが可能な発振器を提供する。

【解決手段】発振器100は、MOSFETである第1トランジスタM1および第2トランジスタM2を有するクロスカップルドインバータ10を備える。この発振器100は、発振動作中に、第1トランジスタM1、第2トランジスタM2それぞれのゲートソース間電圧Vgs1、Vgs2、ドレインソース間電圧Vds1、Vds2、ゲートソース間しきい値電圧Vth1、Vth2の間に、

Vds1≧Vgs1−Vth1

Vds2≧Vgs2−Vth2

なる関係が成り立つよう構成される。

(もっと読む)

通信装置

【課題】情報通信の安定化を図りうる通信装置を提供する。

【解決手段】通信装置は、送信機1と受信機2を含む。送信機1は、送信すべき情報INを変調して出力する変調回路3と、この変調回路3からの送信出力信号を放射する送信アンテナ電極4と、を有する。受信機2は 送信アンテナ電極4と対をなし、送信アンテナ電極4から放射された送信出力を受信する受信アンテナ電極5と、この受信アンテナ電極5と送信アンテナ電極4との間に存在する準静電界の静電容量Cを回路要素として発振動作を行う発振回路6と、この発振回路6からの出力信号を復調する復調回路7と、を有する。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

発振装置

【課題】発振周波数の変動を防止することができる発振装置を提供する。

【解決手段】トランジスタのゲート電圧に応じて入力端子の信号を出力端子から出力するトランスファゲートPM5,NM5と、トランスファゲートの出力端子の信号を入力し、入力した信号の論理反転信号を出力する第1のインバータIV1と、第1のインバータの出力端子の信号を入力し、入力した信号の論理反転信号を出力する第2のインバータPM6,NM6と、第1のインバータの出力信号の論理反転信号を入力し、入力した信号の論理反転信号をトランスファゲートの入力端子に出力する第3のインバータPM4,NM4と、トランスファゲートの出力端子及び第2のインバータの出力端子間に接続される第1の容量C1と、トランスファゲートの出力端子及び基準電位ノード間に接続される第2の容量C2とを有する発振装置。

(もっと読む)

MOSFETのソースバルク電圧を用いた信号処理ASIC用の温度補償RC発振器

温度補償CMOS RC発振回路は、抵抗と温度相関バイアス電流とを用いてソースバルク電圧を変化させて、温度に対するMOSFETの閾値電圧の変動を安定させる。この温度層間バイアス電流はまた、抵抗を流れる。温度が上昇すると、バイアス電流も増え、MOSFETのソースバルク電圧を上昇させる。上昇したソースバルク電圧は、高い温度にてMOSFETの閾値電圧を安定させるのを補助する。この発振器には省電力ロジックも組み込まれており、低い電力消費で高い周波数が得られる。本発明では、得られる発振器が低出力設計となってしまう高利得オペアンプや高速比較器はなく、他のシステムとともにシングルチップに組み込むことができる。 (もっと読む)

発振回路

【課題】コンデンサへの充放電及び差動対を使用した発振回路において、回路規模や消費電力の増大を抑制しつつ安定した発振を可能とする。

【解決手段】トランジスタM10は、トランジスタM1,M2からなる差動対に定電流i1を供給する。M1には直列に抵抗R1が接続され、M1とR1との接続点の電位VBがM2のゲートに印加される。一方、M1のゲートには、定電流i2を生じるトランジスタM4と抵抗R2及びコンデンサC1の並列接続体との接続点の電位VAが印加される。M4は、M2のオフ期間に定電流i2を供給し、オン期間に定電流の供給を停止する。抵抗R2,R1それぞれの抵抗値をr2,r1として、(r1・i1)=(r2・i2)を満たすように設定する。

(もっと読む)

温特補正機能付き発振回路およびその製造方法

【課題】 発振周波数を補正するためのメモリなどが不要な温特補正機能付き発振回路およびその製造方法を実現する。

【解決手段】 温特補正機能付き発振回路10は、第1の発振回路21と、第2の発振回路22と、第1の発振回路21が発生する発振周波数を理想の発振周波数に近い発振周波数に補正するための補正回路50とを備える。補正回路50は、第1の発振回路21の発振周波数f1と、第2の発振回路22の発振周波数f2との差分(f1−f2)を検出し、その検出した差分に補正係数αを乗じ(α・(f1−f2))、その補正された差分を第1の発振回路21の発振周波数に加算し(f1+α・(f1−f2))、それを出力する動作を行う。

(もっと読む)

ウイーンブリッジ発振回路の自動利得制御回路

【課題】ウイーンブリッジ発振回路の自動利得制御回路を、低コストで実現する。

【解決手段】ウイーンブリッジ発振回路を構成するオペアンプの出力を、抵抗3により電流に変換してNPN型バイポーラトランジスタ1のベースに入力し、NPN型バイポーラトランジスタ1のコレクタとエミッタ間の抵抗値を増減することにより、抵抗2と抵抗4とNPN型バイポーラトランジスタ1による合成抵抗を増減し、オペアンプの利得を増減する。

(もっと読む)

自動調整発振器

【課題】チャージポンプを用いずに、出力周波数の精度を高くすることのできる自動調整発振器を提供する。

【解決手段】発振器10は、発振回路11、第1電圧供給回路13、第2電圧供給回路14及び調整値生成回路16を備えている。第1電圧供給回路13は、基準時間で第1電圧V1が基準電圧Vrefに到達するような時定数となる抵抗値の抵抗器R1とキャパシタン

スのキャパシタC1とを備える。第2電圧供給回路14は、発振回路11の周波数に応じたパルス信号S1,S2によってスイッチングを行なう第1及び第2スイッチング手段SW1,SW2によって第2電圧V2を上昇させる。調整値生成回路16は、第2電圧V2が第1電圧V1よりも先に基準電圧Vrefになった場合には、周波数を低くする調整値を

発振回路11に供給し、第2電圧V2が第1電圧V1よりも遅れて基準電圧Vrefになっ

た場合には、周波数を高くする調整値を発振回路11に供給する。

(もっと読む)

電子回路

【課題】電子回路(例えば、マイクロコンピュータ)の動作モードに応じて、低周波数の発振器について適切な電源インピーダンスを設定することにより、前記発振器の誤動作を防止しながら、消費電力を適切に低減することができる。

【解決手段】システムクロックのクロック源として、高速発振器11、中速発振器12、低速発振器13が設けられる。また、時計用クロックを発生する水晶発振器30が設けられる。そして、高速発振器11が動作している時は、水晶発振器30の電源インピーダンスを低くして、耐ノイズ性を高める。一方、高速発振器11、中速発振器12、低速発振器13がすべて停止している待機時には、水晶発振器30の電源インピーダンスを高くして消費電力を抑える。

(もっと読む)

発振回路、集積回路装置及び電子機器

【課題】複数の周波数のうちから所望の周波数を選択してクロック信号を生成できる発振回路、集積回路装置及び電子機器を提供すること。

【解決手段】発振回路は、キャパシター10の一端、第1の抵抗素子20の一端及び第2の抵抗素子30の一端がその入力に接続される第1の反転回路と、キャパシター10の他端がその出力に接続される第n(nは2以上の偶数)の反転回路とを有する第1〜第nの反転回路INV1〜INVnと、第nの反転回路INVnの出力が入力され、第1の抵抗素子20の他端を駆動する第1の駆動用反転回路DR1と、第nの反転回路INVnの出力が入力され、第2の抵抗素子30の他端を駆動する第2の駆動用反転回路DR2とを含む。

(もっと読む)

1 - 20 / 43

[ Back to top ]