Fターム[5J081GG05]の内容

LC分布定数、CR発振器 (9,854) | 出力構成 (309) | 出力回路 (223) | 増幅器・バッファ回路 (86)

Fターム[5J081GG05]に分類される特許

1 - 20 / 86

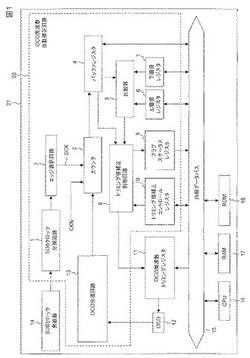

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

発振回路、発振器、電子機器及び発振回路の起動方法

【課題】インダクタンス素子に起因して発生する起動時の異常発振を効率的に抑えることが可能な発振回路、発振器、電子機器及び発振回路の起動方法を提供すること。

【解決手段】発振回路1は、共振子(SAW共振子10)と、増幅回路20と、スイッチング素子(NMOSスイッチ30)と、を含む。増幅回路20は、共振子の一端から他端への帰還経路、当該帰還経路に設けられている第1のインダクタンス素子(伸長コイル200)、当該帰還経路に設けられ、第1のインダクタンス素子と直列に設けられている可変容量素子(可変容量ダイオード202)、を有している。スイッチング素子は、第1のインダクタンス素子と可変容量素子とを含む回路部に対して並列に設けられている。

(もっと読む)

発振器、半導体部品及び電子機器

【課題】複数の端子のうち一部の端子が使用されない場合においても好適に動作可能な発振器を提供する。

【解決手段】発振器1は、振動素子14と、振動素子14に電圧を印加して発振信号Outを生成する発振回路27と、発振回路27の出力部27aに接続されることにより発振信号Outを出力可能な端子5(Out1)及び端子5(Out2)と、出力部27aと外部機器(回路基板53を含む)との端子5(Out2)を介した導通状態の変化に応じた発振回路27の周波数の変化を補償する接続補償回路37とを有する。

(もっと読む)

カスケード接続されたエミッタフォロワバッファ段を有する電圧制御発振器

【課題】負荷条件の変化に対しても安定に動作するVCOを提供する。

【解決手段】第1のトランジスタ40aを含む第1のバッファ段と、第2のトランジスタ40bを含む第2のバッファ段とを備え、カスケード接続されたエミッタフォロワバッファ回路として配置されている。トランジスタ40aおよび40bは、VCOコア21を出力から隔離する共通のエミッタ/ソースフォロワ回路に設けられている。したがって結合バッファ段42の両方のバッファ段すなわちトランジスタ40aおよび40bは、同一の電流を分担する。また、これらバッファ段はVCOコア21にACカップリング、逆隔離は直列結合された2つの固有のベース/エミッタ接合キャパシタンスによって決定されるため、キャパシタンスが半分に減少し、これによって、トランジスタ40aおよび40bのサイズが等しければ、2倍の逆隔離が得られる。

(もっと読む)

発振回路

【課題】コンパレータの消費電力を抑えつつ、高周波の発振出力の振幅を検出できる、発振回路を提供すること。

【解決手段】水晶振動子1を共振器として使用して発振出力Vxを生成する発振出力生成回路11と、発振出力Vxの振幅を検出する振幅検出回路15と、振幅検出回路15の出力Vsに応じて発振出力Vxをブーストするブースト回路16とを有する発振回路であって、振幅検出回路15は、発振出力Vxが入力される絶対値回路12と、絶対値回路12の出力を入力とするローパスフィルタ13と、ローパスフィルタ13の出力を入力とするコンパレータ14とを備えることを特徴とする、発振回路。

(もっと読む)

圧電発振器

【課題】ピアース型圧電発振器で高い周波数出力を可能にする。

【解決手段】圧電振動子10の一方の端子と接地電位線GNDとの間に接続された第1の容量素子C1と、圧電振動子10の他方の端子と接地電位線GNDとの間に接続された第2の容量素子C2と、コレクタ端子が圧電振動子10の一方の端子に接続されベース端子が圧電振動子10の他方の端子と電流源20とに接続されエミッタ端子が接地電位線GNDに接続された発振用トランジスタQ1と、ベース端子が発振用トランジスタQ1のコレクタ端子に第1の抵抗Rbを介して接続されコレクタ端子が発振用トランジスタQ1のコレクタ端子に第2の抵抗Rcを介して接続されエミッタ端子が発振用トランジスタQ1のベース端子に接続された発振補助用トランジスタQ2と、を含んで構成される発振回路101と、発振用トランジスタQ1のコレクタ端子に接続されたバッファ回路BUFと、を含む圧電発振器1。

(もっと読む)

高周波発振器

【課題】安定発振、コンパクトなパッケージを実現したSHF帯に好適な高周波発振器を提供する。

【解決手段】低誘電率、低損失の基板材料として水晶板等の耐熱材を最小限の厚さとした基板を主基板2とし、一次実装する能動素子7とIDT3やデスクリート部品8などを主基板2の表裏にそれぞれ配置し、貫通電極6で両面側の間を接続することで配線長を最短とした。LTCCなどの従来の本体基板に代えて薄い水晶等を要部構成部品を実装する主基板とすることにより、薄型化と小型化を実現した。外力・応力に対する脆弱性を、主面側の保護カバーに加えて裏面にも補強カバーを設け、あるいはモールド構造とすることで補強した。

(もっと読む)

電圧制御発振器

【課題】5GHz以上の周波数帯域で出力周波数を調整するコルピッツ回路を用いた電圧制御発振器において、出力周波数の可変幅(調整幅)の劣化(低下)を抑えると共に、位相雑音の良好な特性を持つ電圧制御発振器を提供すること。

【解決手段】可変周波数帯域内における周波数fに対応する波長をλとすると、共振部1のバリキャップダイオード13とトランジスタ21のベース端子との間に直列となるように、線路長Dがλ/4で且つ特性インピーダンスが10Ω以下の伝送線路6を配置して、トランジスタ21のベース端子からバリキャップダイオード13側を見た時に、当該バリキャップダイオード13と伝送線路6とがいわば可変インダクタンス素子Lと等価になるようにする。

(もっと読む)

電圧制御発振器

【課題】増幅用のトランジスタに帰還容量成分C1及び結合容量成分C2の直列回路を接続したコルピッツ発振回路を用いた電圧制御発振器において、部品点数の削減に寄与できる技術を提供すること。

【解決手段】トランジスタ21のベースに接続された第1の伝送線路41とトランジスタ21のエミッタとアースとの間に接続された第2の伝送線路42と、を備え、第1の伝送線路41及び第2の伝送線路42を互いに接近させて両者の間に線路間容量成分を形成する。この線路間容量成分を前記帰還容量成分C1として利用すると共に第2の伝送線路42とアースとの間に形成される寄生容量成分を前記結合容量成分C2として利用する

(もっと読む)

回路装置及び電子機器

【課題】無駄な電力消費やノイズの悪影響等を抑制できる回路装置及び電子機器等の提供。

【解決手段】回路装置は発振回路10とバッファー回路20を含む。バッファー回路20は、プリバッファーPBFと第1、第2の出力バッファーQBF1、QBF2を含む。第1のモードでは、第1の出力バッファーQBF1が動作イネーブル状態に設定され、第2の出力バッファーQBF2が動作ディスエーブル状態に設定される。第2のモードでは、第1の出力バッファーQBF1及び第2の出力バッファーQBF2が動作イネーブル状態に設定される。第1のモードでは、プリバッファーPBFの駆動能力が、第2のモードに比べて低い駆動能力に設定される。

(もっと読む)

発振回路及び発振回路を搭載した電子機器

【課題】本発明の目的は、水晶発振回路の駆動電流が100nA以下と非常に小さくなり、水晶発振回路の出力が0.1Vpp以下と小さくなっても、水晶発振回路の出力に接続する次段の種々の回路が正常に動作する出力信号を出発振回路、及びそれを搭載した電子機器を提供する。

【解決手段】水晶発振回路の出力を増幅する増幅回路を水晶発振回路の出力側に接続し、水晶発振回路の出力電圧と水晶発振回路のCMOSインバータの入力電圧との差を増幅させる。たとえば、差動アンプを水晶発振回路の出力側に接続し、水晶発振回路の出力電圧とCMOSインバータの入力電圧とを差動アンプの入力とする。あるいは、3つのオペアンプから構成されるインスツルメンテーションアンプを水晶発振回路の出力側に接続し、水晶発振回路の出力電圧信号と水晶発振回路のCMOSインバータの入力電圧信号との差を増幅させる。

(もっと読む)

発振器

【課題】発振器の発振周波数、又は負荷の大小によるバッファー回路の出力レベル変動を抑制して、バッファー回路の消費電力を低減する発振器を提供する。

【解決手段】この発振器100は、発振回路18と、発振回路18の発振信号を増幅するプリバッファー回路19と、最終段のバッファー回路11と、バッファー回路11の出力電圧レベルを検出するレベル検出回路8と、レベル設定2に応じてレベル検出回路8のレベルを増幅する増幅回路1と、増幅回路1から出力したレベル検出回路8の検出レベルに基づいて出力信号(OUT)の電圧、又は電流を制御してバッファー回路11の出力レベルを調整するレベル調整回路5と、を備えて構成されている。

(もっと読む)

発振装置

【課題】水晶発振回路の消費電力の低減を図りつつ後段回路を作動させることができる発振装置を提供する。

【解決手段】第1電源V1が、振幅検出回路3に対して第1電源電圧(3V)を供給する。第2電源V2が、水晶振動回路2に対して第1電源電圧(3V)よりも小さい第2電源電圧(1V)を供給する。振幅検出回路3は、CMOSインバータIV1の出力端子から出力される発振信号と、第2電源電圧(1V)を分圧して得た基準電圧Vrefと、それぞれのベースに接続される一対のトランジスタが設けられたコンパレータ31を備えている。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

電圧制御発振器

【課題】小型で周波数特性の良好な電圧制御発振器を提供する。

【解決手段】電圧制御発振器(VCO)の共振部1は、共振周波数の調整を行うために静電容量が変化する可変容量素子13、14と、インダクタンス素子11と、を含み、エミッタ接地型のトランジスタ21はこの共振部1からベース端子T1に入力された周波数信号を増幅する。帰還部2は帰還用の容量素子22、23を含み、前記トランジスタ21のエミッタ端子T2から出力された周波数信号を、前記ベース端子T1を介してトランジスタ21に帰還させる。そして前記ベース端子T1に印加されるバイアス電圧を調整するためのベース・ブリーダ抵抗R2、R3及びトランジスタ21が共通の集積回路3内に形成され、トランジスタ21の動作点を調整するためにエミッタ抵抗R1はこの集積回路3外に別体の抵抗素子として設けられる。

(もっと読む)

発振装置

【課題】発振周波数を決定する容量値の変化に伴う発振周波数の変動を抑え、且つ、位相雑音を低減することのできる発振装置を提供する。

【解決手段】発振装置は、ドレイン接地回路からなる第1増幅回路10と、第1増幅回路10の出力を増幅する、ゲート接地回路からなる第2増幅回路20と、第2増幅回路20の出力を第1増幅回路の入力に帰還させるコンデンサC1と、第1増幅回路10の入力側に設けられた共振器2と、共振器2及び第1増幅回路10内のトランジスタQ1に動作用のバイアス電圧を印加するバイアス回路12と、第2増幅回路20内のトランジスタQ2に動作用のバイアス電圧を印加するバイアス回路22とから構成される。この結果、位相雑音の発生を、単一のトランジスタからなるコルピッツ発振回路と同程度に抑えつつ、容量変化によって発振を起動できなくなったり、発振周波数が変動するのを防止できる。

(もっと読む)

水晶発振器

【課題】水晶発振器の出力振幅の調整機能を簡易な構成で実現する。

【解決手段】水晶発振器は、電源に接続される電源端子(VCC)と、接地電位に維持される接地端子(GND)と、電源端子と接地端子とに接続され、電源端子と接地端子との間に印加された電源電圧に基づく振幅レベルの発振信号(V0)を出力する水晶発振回路(6)と、イネーブル信号(VEN1、VEN2)が入力されるイネーブル端子(EN1、EN2)と、イネーブル端子と接地端子とに接続され、水晶発振回路から入力される発振信号を波形整形してイネーブル端子と接地端子との間のイネーブル信号の電圧に応じた振幅レベルの基準クロック信号(CLK1、CLK2)を出力するバッファ回路(2a、2b)と、バッファ回路から出力される基準クロック信号が出力される出力端子(OUT1、OUT2)と、を備える。

(もっと読む)

半導体装置

【課題】VCOに含まれるスパイラルインダクタとMOSバラクタを接続する配線に付加される寄生インダクタ、および/または寄生容量を低減することができる半導体装置を提供する。

【解決手段】LCタンクVCOは、第1および第2のスパイラルインダクタL1,L2と、第1および第2のMOSバラクタC1,C2とを備える。第1および第2のMOSバラクタC1,C2は、半導体基板に垂直な方向から見たときに、第1のスパイラルインダクタL1と第2のスパイラルインダクタL2の間の領域に配置される。

(もっと読む)

電圧制御発振器

【課題】コルピッツ回路を用いた電圧制御発振器において、帰還部の2つのコンデンサ間とトランジスタのエミッタとを接続する導電線路におけるインダクタンス成分の影響による出力周波数の可変幅(調整幅)の劣化(低下)を抑えることのできる電圧制御発振器を提供すること。

【解決手段】コルピッツ回路を用いたVCOにおいて、帰還部2のコンデンサ22、23について、トランジスタ21のベースから伸びる端子部8(T1)及び前記トランジスタ21のエミッタから伸びる端子部8(T2)が夫々装着されるベース基板5上のベース用端子(接続部7)とエミッタ用端子とを直結するように第1の帰還容量素子(コンデンサ)22を配置すると共に、上記エミッタ用端子とアース用端子(接地電極51)とを直結するように第2の帰還容量素子(コンデンサ)23を配置する。

(もっと読む)

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

1 - 20 / 86

[ Back to top ]