Fターム[5J081LL05]の内容

LC分布定数、CR発振器 (9,854) | 改善手段(発明内容) (679) | 回路の追加・削除・変更 (351)

Fターム[5J081LL05]に分類される特許

41 - 60 / 351

発振器及び半導体集積回路装置

【課題】発振器の出力端子間に直接寄生する容量Cparaの大きさが無視できない場合でも温度特性を補償する発振器及び発振器を内蔵する半導体集積回路装置を提供する。

【解決手段】インダクタンス素子Lと、容量素子Cと、増幅器30と、をそれぞれ第1の端子と第2の端子との間に並列に接続し、インダクタンス素子と容量素子とによって生じる共振を増幅器によって増幅し、第1の端子と第2の端子とから出力する発振器であって、第1の端子と第2の端子との間にインダクタンス素子の寄生抵抗RLより抵抗値の大きな第1の抵抗素子Rcが第1の端子と第2の端子との間に容量素子と直列に接続されている。

(もっと読む)

磁気同調デバイス駆動回路及びそれを備えた測定装置並びに磁気同調デバイス駆動方法

【課題】小型化及び低消費電力化を図ることができる磁気同調デバイス駆動回路及びそれを備えた測定装置並びに磁気同調デバイス駆動方法を提供する。

【解決手段】磁気同調デバイス駆動回路10は、固定電圧を出力する電源に接続され、印加された出力電圧制御信号に応じた電圧を出力するスイッチング電源回路11と、スイッチング電源回路11の出力電圧を所望の同調周波数に応じた電流に変換して同調コイル51に供給する定電流回路12と、同調コイル51の電圧の絶対値を所定値だけ大きくするシフト電圧を供給するシフト電圧供給部13と、電流が供給された同調コイル51の電圧とシフト電圧とを加算し、加算後の電圧を出力電圧制御信号としてスイッチング電源回路11に出力する加算回路14と、を備える。

(もっと読む)

高周波発振器

【課題】小型に構成され、高調波と基本波との電力比を増加可能な高周波発振器を得る。

【解決手段】印加された電源電圧に基づいて、発振周波数の基本波で発振動作を行い、発振周波数の2倍波を出力する2倍波取り出し型発振器10と、2倍波取り出し型発振器10の出力端子に接続され、発振周波数の2倍波を通過帯域とする出力回路20とを備え、出力回路20は、2倍波取り出し型発振器10に電源電圧を供給する電源端子21と、2倍波取り出し型発振器10と電源端子21との間に直列に接続され、発振周波数の2倍波に対してほぼ1/4波長の長さを有する結合線路22と、2倍波取り出し型発振器10と電源端子21との間に直列に接続され、発振周波数の2倍波に対してほぼ1/4波長の長さを有する伝送線路23と、結合線路22の結合量に応じた出力電力を得る第1負荷抵抗24と、電源端子21に対して並列に接続されたキャパシタ25とを有する。

(もっと読む)

発振装置

【課題】水晶発振回路の消費電力の低減を図りつつ後段回路を作動させることができる発振装置を提供する。

【解決手段】第1電源V1が、振幅検出回路3に対して第1電源電圧(3V)を供給する。第2電源V2が、水晶振動回路2に対して第1電源電圧(3V)よりも小さい第2電源電圧(1V)を供給する。振幅検出回路3は、CMOSインバータIV1の出力端子から出力される発振信号と、第2電源電圧(1V)を分圧して得た基準電圧Vrefと、それぞれのベースに接続される一対のトランジスタが設けられたコンパレータ31を備えている。

(もっと読む)

発振器

【課題】少ない電流で必要な負性抵抗が得られることにより、安定に動作することのできる発振器を提供する。

【解決手段】互いに並列に配設された容量素子134,234およびインダクタ133,233を有する共振回路13,23と、共振回路13,23の損失を打ち消す負性抵抗が生じるように配設された複数のトランジスタを有する負性抵抗発生器14,24と、第1バイアス端子15,25と、第2バイアス端子16,26と、を備えた複数の発振部10,20と、各共振回路13,23が互いに等価的に並列に接続されるように、複数の発振部10,20を電気的に結合する結合部30Aと、を備え、複数の発振部10,20は、それぞれの第1バイアス端子25および第2バイアス端子16において互いに直列に接続され、複数の発振部10,20における複数のトランジスタ143,144,243,244は、互いに同じ導電型で構成されている。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

発振回路

【課題】、数百メガヘルツの発振周波数を有する発振信号を出力する場合において、半導体集積回路内に設けられた他の回路の特性劣化を抑制することができる発振回路を提供する。

【解決手段】半導体集積回路の内部に設けられた内部キャパシタと、半導体集積回路の外部に設けられた外部キャパシタ及び外部インダクタとからなる共振回路と、共振回路に入力端及び出力端が接続された増幅回路と、を有し、共振回路は、内部キャパシタ、外部インダクタ、並びに内部キャパシタ及び外部インダクタを接続する配線からなる第1閉回路と、外部キャパシタ、外部インダクタ、並びに外部キャパシタ及び外部インダクタを接続する配線からなり、第1閉回路の配線抵抗よりも小なる配線抵抗を有する第2閉回路と、を有することを特徴とする発振回路。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

車両制御システムおよび車載器

【課題】携帯機と車載器との間で無線通信を行うに際し、車載器に使用される振動子の発振周波数の温度ばらつきを軽減する。

【解決手段】受信IC22には車載器20の温度を測定する第2温度センサ27が内蔵されている。そして、補正部23は、携帯機10の第1振動子11および車載器20の第2振動子21の周波数温度特性のデータマップがそれぞれ記憶されており、受信IC22から携帯機10の温度を示す送信側温度情報を入力すると共に第2温度センサ27から車載器20の温度を示す受信側温度情報を入力し、送信側温度情報、受信側温度情報、およびデータマップに基づいて取得したオフセット値を第2振動子21に付加することで、第2振動子21の第2周波数を第1振動子11の第1周波数に近づける補正を行う。

(もっと読む)

プッシュプッシュ発振器及び位相ずれ監視方法

【課題】位相ずれを確認する技術を提供する。

【解決手段】プッシュ・プッシュ発振回路100は、相互に逆位相で動作する、2つの発振器1、2と、2つの発振器1、2から出力された第1出力信号を合成する合成器101と、合成器101から出力された第2出力信号に含まれる第1出力信号の基本波を監視するための基本波監視回路102と、を備えている。即ち、基本波監視回路102を用いることで、合成器101から出力された第2出力信号に含まれる第1出力信号の基本波を確認することができる。第1出力信号の基本波を確認することで、合成器101に入力された2つの第1出力信号が逆位相であったか確認することができる。

(もっと読む)

センサのモニタリング装置

【課題】高温環境下でも正常に動作してセンサの測定値を正確に求めることができるようにする。

【解決手段】本発明のモニタリング装置1は、センサ2と、このセンサ2が接続され且つワイドバンドギャップ半導体を使用した発振器を備えたインタフェース3と、インターフェース3とは別に配置され且つインターフェース3から出力された発振信号を処理する演算装置4とを備えている。発振器は、基準となる発振信号を出力する第1発振器6aと、センサ2の出力に基づいて発振信号を出力する第2発振器6bとから構成されている。第演算装置4は、第1発振器6aからの発振信号と第2発振器6bからの発振信号とに基づいてセンサ2で測定した測定値を算出する演算部15とを備えている。

(もっと読む)

アナログ回路

【課題】高い歩留りを得ながらゲートスロープを抑制することができるアナログ回路を提供する。

【解決手段】アナログ回路には、発振トランジスタ27と、発振トランジスタ27に対する負性抵抗を変更する負性抵抗変更回路と、が設けられている。負性抵抗変更回路には、可変抵抗回路及び可変容量回路が含まれている。可変抵抗回路には、抵抗体29、抵抗体31及びトランジスタ(スイッチ)35が含まれ、可変容量回路には、キャパシタ30及び可変容量ダイオード36が含まれている。

(もっと読む)

発振装置および角速度検出装置

【課題】振動子の起動を確実にし、安定して振動を維持する装置を提供する。

【解決手段】振動子12と、振動状態を検出する検出アンプ13と、振動情報を2値化してコンパレータ出力信号を出力する振幅比較器14と、制御発振器入力信号に応じて周波数が変化する電圧制御発振器151と、コンパレータ出力信号と比較信号との位相差信号を出力する位相比較器153と、位相差信号の低域成分を出力するループフィルタ154と、比較信号に対して予め定める位相差を有する位相シフト信号を出力する位相シフト器22と、位相シフト信号を入力する駆動アンプ11と、操作信号を出力する操作信号発生器21と、制御発振器入力信号として操作信号を選択し、制御発振器出力信号の周波数がキャプチャレンジの範囲となったときに、制御発振器入力信号として位相差情報信号を選択する操作切換器20と、を備える。

(もっと読む)

静磁波発振装置

【課題】外部磁界からの影響を防止しつつ、小型化及び軽量化を図ると共に、耐振動及び耐衝撃性を向上させた静磁波発振装置を提供する。

【解決手段】静磁波素子を用いて所望の発振周波数を得る静磁波発振装置1であって、静磁波発振装置本体2の周囲に強磁性体33a,33bと振動を吸収可能な非磁性体32a,32b,32cとを交互に積層させると共に、該非磁性体32a,32b,32cが吸収可能な振動周波数を層によって相違させる。

(もっと読む)

発振装置

【課題】発振周波数を決定する容量値の変化に伴う発振周波数の変動を抑え、且つ、位相雑音を低減することのできる発振装置を提供する。

【解決手段】発振装置は、ドレイン接地回路からなる第1増幅回路10と、第1増幅回路10の出力を増幅する、ゲート接地回路からなる第2増幅回路20と、第2増幅回路20の出力を第1増幅回路の入力に帰還させるコンデンサC1と、第1増幅回路10の入力側に設けられた共振器2と、共振器2及び第1増幅回路10内のトランジスタQ1に動作用のバイアス電圧を印加するバイアス回路12と、第2増幅回路20内のトランジスタQ2に動作用のバイアス電圧を印加するバイアス回路22とから構成される。この結果、位相雑音の発生を、単一のトランジスタからなるコルピッツ発振回路と同程度に抑えつつ、容量変化によって発振を起動できなくなったり、発振周波数が変動するのを防止できる。

(もっと読む)

可変容量素子

【課題】従来の可変容量素子は、容量値の精度が低い問題があった。

【解決手段】本発明の可変容量素子は、第1の電源端子と出力端子CTOPとの間に接続される第1の容量素子C1と、容量切替信号CSELに応じて導通状態が切り替えられる容量選択スイッチN1と、第1の容量素子C1と並列に接続され、かつ、容量選択スイッチN1と直列に接続される第2の容量素子C2と、容量選択スイッチN1が遮断状態とされる状態において、出力端子CTOPをリセット電圧にリセットする電荷リセット信号INITBに応じて、第2の容量素子C2と容量選択スイッチN1とを接続する容量切替ノードNDaの電圧と出力端子CTOPの電圧とを実質的に同じ電圧に設定する誤差補正回路10と、を有する。

(もっと読む)

発振回路及び電子機器

【課題】発振周波数が安定するまでに要する時間の短い発振回路及び電子機器を提供する。

【解決手段】周波数補正回路を有する共振回路と、前記共振回路の両端の間に接続された増幅回路とを備えた発振回路が提供される。前記周波数補正回路は、第1のコンデンサと、両端の電位が変動可能に前記第1のコンデンサと直列的に接続された第1のトランジスタと、を有することを特徴とする。

(もっと読む)

電圧電流変換回路及び電圧制御発振器

【課題】入力電圧に対する出力電流の動作範囲の拡大できる電圧電流変換回路を提供する。

【解決手段】入力電圧INがトランジスターM4の閾値電圧以下の場合には、トランジスターM4はオフである。一方、トランジスターM9によって入力電圧INがレベルシフトされる。そのレベルシフト後の印加電圧VAによってトランジスターM10がオンし、M10に流れるI10が、トランジスターM1に流れるI1となる。また、入力電圧INがM4の閾値電圧を超える場合には、M4がオンし、M4に流れるI4と、M10に流れるI10との和が、M1に流れるI1となる。そして、M1,M2,M3によって形成されるカレントミラー回路によって、M1に流れるI1に応じた電流が、負荷回路10,12に供給される。

(もっと読む)

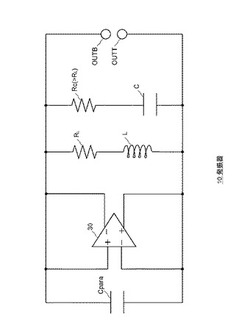

発振回路

【課題】小型かつノイズ抑制に優れる発振回路を提供すること。

【解決手段】本発明にかかる発振回路100は、インバータ1及び2、タンク回路3を有する。タンク回路3は、出力ノードOUTTと出力ノードOUTBとの間に並列に接続される。インバータ1は、ドレインが出力ノードOUTBに接続されたn型MISトランジスタM1及びp型MISトランジスタM3を有する。インバータ2は、ドレインが出力ノードOUTTに接続されたn型MISトランジスタM2及びp型MISトランジスタM4を有する。p型MISトランジスタM3及びM4のゲート端子は、それぞれ出力ノードOUTT及びOUTBと直接的に接続される。n型MISトランジスタM1及びM2のゲート端子は、それぞれ結合容量CG1及びCG2を介して出力ノードOUTT及びOUTBと接続され、抵抗CG1及びCG2を介してバイアス電圧VBIASが印加される。

(もっと読む)

水晶発振器

【課題】水晶発振器の出力振幅の調整機能を簡易な構成で実現する。

【解決手段】水晶発振器は、電源に接続される電源端子(VCC)と、接地電位に維持される接地端子(GND)と、電源端子と接地端子とに接続され、電源端子と接地端子との間に印加された電源電圧に基づく振幅レベルの発振信号(V0)を出力する水晶発振回路(6)と、イネーブル信号(VEN1、VEN2)が入力されるイネーブル端子(EN1、EN2)と、イネーブル端子と接地端子とに接続され、水晶発振回路から入力される発振信号を波形整形してイネーブル端子と接地端子との間のイネーブル信号の電圧に応じた振幅レベルの基準クロック信号(CLK1、CLK2)を出力するバッファ回路(2a、2b)と、バッファ回路から出力される基準クロック信号が出力される出力端子(OUT1、OUT2)と、を備える。

(もっと読む)

41 - 60 / 351

[ Back to top ]