Fターム[5J081LL05]の内容

LC分布定数、CR発振器 (9,854) | 改善手段(発明内容) (679) | 回路の追加・削除・変更 (351)

Fターム[5J081LL05]に分類される特許

101 - 120 / 351

多重補間LC電圧制御発振器

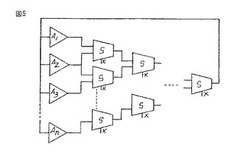

【課題】周波数が、中心周波数近辺の同調範囲内の周波数で制御される発振信号を形成するLC電圧制御発振器の提供。

【解決手段】位相補間電圧制御発振器は、複数のn個の位相シフトセルA及びn−1レベルの加算セルSを内含する。位相シフトセルAは、共通の入力信号を受理し、各々は、その他の位相シフトセルAとは異なる量だけ入力信号を位相シフトさせる。第1レベルの加算セルSは、少なくとも2つの位相シフトセルAの出力を受信し加算し、残りの加算セルレベルの各々は、加算セルSの先行レベルの出力を受理する。最後のレベルは、位相シフトセルAの共通の入力信号としてフィードバックされる出力信号を生成する単一の加算セルSを含む。

(もっと読む)

位相同期発振器アレイ

【課題】小型でIC化が可能な位相同期発振器を実現すること。

【解決手段】 位相同期した複数の発振信号を得る位相同期発振器アレイにおいて、位相が180度異なる2つの信号を入力する第1入力端子と第2入力端子とを有したn個の第1差動増幅器から第n差動増幅器と、1≦k<nの全ての自然数kに対して、第k差動増幅器の第2入力端子と第k+1差動増幅器の第1入力端子との間の全て、及び、第n差動増幅器の第2入力端子と第1差動増幅器の第1入力端子との間を、それぞれ、逆相で結合するn個のフィルタFと、を設けたことを特徴とする位相同期発振器アレイ。フィルタFは、一方の差動増幅器1の第2入力端子B12と接地間に配設された第2インダクタL12と、他方の差動増幅器2の第1入力端子B21と接地間に配設された第1インダクタとL21、一方の差動増幅器1の第2入力端子と他方の差動増幅器2の第1入力端子との間を接続する第3容量C15と第3インダクタL23との直列接続回路とを有する。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

自動調整発振器

【課題】チャージポンプを用いずに、出力周波数の精度を高くすることのできる自動調整発振器を提供する。

【解決手段】発振器10は、発振回路11、第1電圧供給回路13、第2電圧供給回路14及び調整値生成回路16を備えている。第1電圧供給回路13は、基準時間で第1電圧V1が基準電圧Vrefに到達するような時定数となる抵抗値の抵抗器R1とキャパシタン

スのキャパシタC1とを備える。第2電圧供給回路14は、発振回路11の周波数に応じたパルス信号S1,S2によってスイッチングを行なう第1及び第2スイッチング手段SW1,SW2によって第2電圧V2を上昇させる。調整値生成回路16は、第2電圧V2が第1電圧V1よりも先に基準電圧Vrefになった場合には、周波数を低くする調整値を

発振回路11に供給し、第2電圧V2が第1電圧V1よりも遅れて基準電圧Vrefになっ

た場合には、周波数を高くする調整値を発振回路11に供給する。

(もっと読む)

VCO周波数チューニングのための、オーバーラップする2セグメントキャパシタバンク

【解決手段】(例えばFM受信機中の)VCOは、LC共振タンクを含む。LC共振タンクは、粗同調キャパシタバンクおよび微同調キャパシタバンクを含む。粗同調キャパシタバンクは複数のデジタル制御粗同調キャパシタエレメントを含み、アクティブな際に各々は第1キャパシタンス値を供給する。微同調キャパシタバンクは複数のデジタル制御微同調キャパシタエレメントを含み、アクティブな際に各々は第2キャパシタンス値を供給する。キャパシタミスマッチの現実的な問題に対処するため、VCOチューニング範囲の全体にわたるキャパシタンスオーバーラップが、微キャパシタバンクのデジタル制御微同調キャパシタエレメントの全てがアクティブな場合に、微キャパシタバンクのキャパシタンス値が第1キャパシタンス値より大きくなるように第1及び第2キャパシタンス値を選択することによって生成される。 (もっと読む)

発振回路

【課題】高周波発振であっても安定した発振を行なえる。

【解決手段】発振回路1は、圧電振動子を所定の周波数で励振させる発振回路部を備え、発振回路部の等価回路ECは、負性抵抗RLと容量性リアクタンスCLが直接接続された直列モデルで構成されている。発振回路部の一方の端子ECAにコイルLSの一方の端子が直列接続され、発振回路部の他方の端子ECBとコイルLSの他方の端子との間に抵抗RPが並列接続されている。コイルLSの他方の端子と抵抗RPの一方の端子との接続点が、圧電振動子との接続を行う一方の圧電振動子接続用端子Aとされ、抵抗RPの他方の端子と発振回路部の他方の端子ECBとの接続点が、圧電振動子との接続を行う他方の圧電振動子接続用端子Bとされている。また、抵抗RPの絶対値は、負性抵抗RLの絶対値よりも大きい。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

発振器

【課題】負荷容量に応じて最適な波形を出力可能な発振器を提供する。

【解決手段】発振回路12からの出力を、出力バッファ(前段出力バッファ14、出力バッファ22)を介して負荷回路に出力する発振器10であって、発振器10は、出力バッファ22の駆動能力を出力バッファから流れる電流に応じて調整可能なバッファ制御回路48を有する。ここで出力バッファ22は、発振回路12の後段に複数並列に接続されるとともに、バッファ制御回路48は、出力バッファから流れる電流に応じて出力バッファ22の稼動数を調整する信号を出力バッファ22に出力することにより出力バッファ22の駆動能力を調整している。

(もっと読む)

発振制御回路

【課題】発振開始時からデューティが50%に安定する発振制御回路を提供する。

【解決手段】作動制御回路3が、発振信号の発振電位がCMOSインバータIV1の反転電位よりも低い第1基準電位よりも低くなるまでMOSトランジスタT11及びT12をオフ状態、MOSトランジスタT2をオン状態に保持する。作動制御回路3が、発振信号の発振電位が第1基準電位よりも低くなったとき出力が反転するCMOSインバータIV31と、CMOSインバータ31の後段に設けた抵抗R31とコンデンサC31とからなるローパスフィルタ31と、ローパスフィルタ31の出力が閾値を越えると出力が反転するCMOSインバータ33と、を有している。

(もっと読む)

スプリット遅延ライン発振器における装置、システム及び方法

【課題】安全なデータ伝送を行うスプリット遅延ライン発振器における装置、システム及び方法を提供すること。

【解決手段】安全なデータ伝送を行うスプリット遅延ライン発振器における本装置は、第1装置における第1の変調/復調ブロックを有し、その第1の変調/復調ブロックは、第1の可変遅延を設定し、第1の変調/復調ブロックを通過する共有キャリア信号の周波数を変調し、第2装置における第2の変調/復調ブロックは、第2の可変遅延を設定し、第2の変調/復調ブロックを通過する共有キャリア信号の周波数を変調し、第1及び第2装置は、周波数変調された共有キャリア信号にデータを与えることで、共有する秘密情報を作成する。

(もっと読む)

発振器及びそれを用いた周波数生成回路並びに無線通信システム

【課題】LC型発振器において、高調波歪みによる位相雑音の劣化が小さく、かつ発振振幅の増大化を図り、これにより良好な低位相雑音特性を有する発振器及びそれを用いた通信システムを提供する。

【解決手段】トランジスタからなる少なくとも1つ以上の電圧-電流変換部と、1対の容量性素子と誘導性素子からなるLCタンクを2つ有している共振器とを具備して成り、前記の電圧-電流変換部の出力端子は、前記の共振器に接続され電流-電圧変換されたのちに、前記電圧-電流変換部の入力端子に接続されることにより、帰還ループが構成されて成り、前記共振器を構成している2つのLCタンクを構成する誘導性素子が相互誘導結合されており、前記相互結合係数がおおよそ-0.6であることを特徴とする。

(もっと読む)

電圧制御発振器、並びにそれを用いた無線通信システム及び位相同期回路。

【課題】 位相雑音特性の良好な電圧制御発振器、並びにそれを用いた無線通信システム及び位相同期回路を提供することを目的とする。

【解決手段】

電圧制御発振器10は、共振器Resと、共振器Resに入力側が接続された増幅器AMP1と、増幅器AMP1の出力側と共振器Resとの間に接続されたキャパシタC1aと、増幅器AMP1の入力側と出力側の間に、互いに直列になるように接続されたキャパシタC1bとインダクタL1を備える。さらに、共振器Resに入力側が接続された増幅器AMP2と、増幅器AMP2の出力側と共振器Resとの間に接続されたキャパシタC2aと、増幅器AMP2の入力側と出力側の間に、互いに直列になるように接続されたキャパシタC2bとインダクタL2とを備える。

(もっと読む)

発振回路及び、その発振回路を用いた無線機

【課題】 信号振幅が大きい高調波信号を提供することができる発振器を提供する。

【解決手段】 一導電型又は逆導電型の第1のMOSトランジスタ20と、第1のMOSトランジスタ20のドレイン端子に接続された負荷素子30と、第1のMOSトランジスタ20のソース端子に接続され、高調波信号を出力する基本発振器40とを備え、第1のMOSトランジスタ20のドレイン端子から、基本発振器40から出力される高調波信号の増幅信号を出力することを特徴とする発振回路。

(もっと読む)

バイアス生成回路及び電圧制御発振器

【課題】小さい面積で低ノイズのバイアスを生成する。

【解決手段】 元バイアス電圧を発生するバイアス発生部と、前記元バイアス電圧と比較電圧とを比較し、比較結果を出力する比較部と、可変抵抗部を含む抵抗回路によって構成されて前記比較電圧を発生する抵抗分割部と、前記比較部の比較結果に基づいて、前記比較電圧を前記元バイアス電圧に近づけるように前記可変抵抗部の抵抗値を制御するためのバイアス決定データを求めるバイアス決定制御部と、前記バイアス決定データを保持して前記可変抵抗部の抵抗値を制御することにより前記比較電圧をバイアス電圧として出力させる記憶部とを具備したことを特徴とする。

(もっと読む)

変圧器をベースとしたCMOS発振器

【解決手段】低電圧源で動作可能な変圧器に基づいたCMOS発振器を提供するための技術である。LCタンクは、トランジスタペアのドレインに設けられ、LCタンクのインダクタンスは、トランジスタペアのゲート間のインダクタンスに相互磁気結合される。分離相補型トランジスタペアはLCタンクにも結合される。典型的な実施形態によって、タンク間の3方向結合、トランジスタペアのゲート間のインダクタンス、及び相補型トランジスタペアのゲート間のインダクタンスだけでなくトランジスタペアのゲートにLCタンクが更に供給される。 (もっと読む)

水晶発振器

【課題】実装スペースとコストの更なる低減のため、電子機器内の水晶部品を1つに集約するためには、消費電流や周波数精度の問題があった。

【解決手段】本発明の水晶発振器は、音叉型水晶振動体と、この振動体の温度による発振周波数の変化を、時間領域で連続的に補正するための温度補償回路を含んだ発振回路とを備え、この発振回路の出力を源振として高周波クロック信号を出力する、複数のPLL(フェイズロックループ)回路を備える。このような構成にすることにより、電子機器内で必要とされる全てのクロック信号を、精度良く提供することができる。

(もっと読む)

可変インダクタ及び電圧制御発振器

【課題】LCの並列共振による電圧制御発振器を構成するための可変インダクタであって、小型かつQ値の劣化を抑制した、複数周波数発振可能な可変インダクタを提供すること。

【解決手段】可変インダクタ100は、線対称軸Y−Y’を有し、Y−Y’上の点Bを通るY−Y’に関して線対称なインダクタ部Ind1及びInd2を備える。インダクタ部Ind2は、点B以外でインダクタ部Ind1と交わらず、インダクタ部Ind1及びInd2は共に曲線のみで構成される。インダクタ部Ind1の線路長はInd2の線路長よりも短い。Ind1は、Y−Y’上の点Z1を中心点とした円周上の円弧で構成され、端子D’から点Bを通って端子D’とY−Y’に関して線対称な端子D’’まで延在する。Ind2は、Y−Y’上の点Z2を中心点とした円周上の円弧で構成され端子E’から点Bを通って端子E’とY−Y’に関して線対称な端子E’’まで延在する。

(もっと読む)

半導体発振回路および携帯電話

【課題】基準周波数生成回路は、ロジック回路の電源ノイズの影響を受けて、周波数偏差やピリオドジッターの悪化を引き起こしていた。

【解決手段】CPUや周辺回路などのロジック回路12の電源はレギュレータ13より供給し、基準周波数生成回路11の電源には電源の高周波ノイズを10dB以上の減衰量を持つローパスフィルター10を介してから供給する。これによりロジック回路12で発生する高周波ノイズ起因での周波数偏差やジッターの悪化を抑えることができ、この基準周波数をUARTシリアル回路に接続して通信ができる。

(もっと読む)

基準周波数制御回路

【課題】 基準周波数を生成する発振回路の発振周波数の変化を抑制可能な基準周波数制御回路を提供する。

【解決手段】 入力信号のレベルに応じた周波数で発振する発振回路からの発振信号が入力され、前記発振信号の周波数に応じた出力電圧を出力する周波数電圧変換回路と、前記出力電圧が所定レベルとなるよう前記入力信号のレベルを制御する制御回路と、を備えることを特徴とする基準周波数制御回路。

(もっと読む)

101 - 120 / 351

[ Back to top ]