Fターム[5J106AA04]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583) | PLL(位相同期ループ回路) (1,412)

Fターム[5J106AA04]の下位に属するFターム

デジタルPLL (213)

Fターム[5J106AA04]に分類される特許

201 - 220 / 1,199

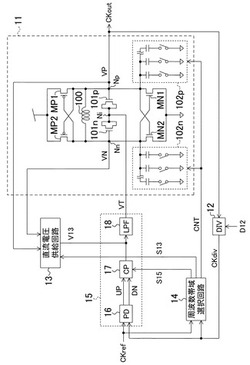

PLL周波数シンセサイザ

【課題】電圧制御発振器のゲイン特性の変動を抑制する。

【解決手段】電圧制御発振器11は、インダクタ100と、微調整コンデンサ101pと、粗調整コンデンサ102pとを含み、発振クロックCKoutを生成する。分周器12は、発振クロックCKoutを分周して分周クロックCKdivを生成する。直流電圧供給回路13は、粗調整モードにおいて、直流電圧V13を制御ノードNiに供給するとともに発振電圧VPの直流値に応じて直流電圧V13の電圧値を変化させる。周波数帯域選択回路14は、粗調整モードにおいて、電圧制御発振器11の発振周波数帯域が目標周波数に対応する発振周波数帯域に設定されるように、基準クロックと分周クロックとの周波数差に基づいて粗調整コンデンサ102pの容量値を切り替える。発振制御回路15は、微調整モードにおいて、基準クロックと分周クロックとの位相差に応じて制御電圧VTを増減させる。

(もっと読む)

PLL回路

【課題】基準周波数信号がPLL回路に入力されなくなった場合に、チャージポンプ回路にループフィルタから電流が流れ続けることを防止する。

【解決手段】PLL回路1は、入力された電圧に応じた周波数のVCO信号を出力するVCO20と、入力された電流に応じた電圧をVCO20に与えるループフィルタ18と、第一入力信号と第二入力信号との位相差に応じた幅の位相差パルスを出力する位相比較器14と、位相差パルスを受けて、ループフィルタ18への電流入力を行うチャージポンプ回路16と、REF信号(基準周波数信号)が入力されていない無入力状態において、チャージポンプ回路16への位相差パルスの入力を停止させる位相差パルス停止部30とを備える。なお、第一入力信号は、REF信号自身又はそれを分周した信号であり、第二入力信号は、VCO信号自身又はそれを分周した信号である。

(もっと読む)

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

高電圧振幅状態の下での電圧制御発振器(VCO)バッファに対するデバイス信頼性の向上

電圧制御発振器(VCO)バッファのための回路が説明される。回路は、VCOコアと接続されるVCOバッファの入力と接続された第1のキャパシタを含む。回路は、また、VCOバッファの入力と、p型金属酸化膜半導体電界効果(PMOS)トランジスタのゲートとに接続された第2のキャパシタを含む。回路は、さらに、第1のキャパシタと、PMOSトランジスタのゲートとに接続された第1のスイッチを含む。回路は、また、VCOバッファの入力と接続された第3のキャパシタを含む。回路は、さらに、VCOバッファの入力と、n型金属酸化膜半導体電界効果(NMOS)トランジスタのゲートとに接続された第4のキャパシタを含む。回路は、また、第3のキャパシタとNMOSトランジスタのゲートとに接続された第2のスイッチを含む。 (もっと読む)

クロック供給装置

【課題】入力クロックの周波数がジッタやワンダ等により時間的に変動する場合においても、入力クロックの不具合の状態を的確に判定することができようにし、適切な保守が可能となる、クロック供給装置を提供する。

【解決手段】本発明のクロック供給装置においては、N系クロック受信部22とN系MTIE計測部31との間に設置されるワンダ・ジッタ除去フィルタ41と、E系クロック受信部23とE系MTIE計測部32との間に設置されるワンダ除去フィルタ42と、を有して構成される。そして、発振器部26が有するローパスフィルタ特性のカットオフ周波数と、ワンダ除去フィルタ41,42の有するローパスフィルタ特性のカットオフ周波数とが一致あるいは略等しいように構成される。

(もっと読む)

遅延同期ループ回路およびインターフェース回路

【課題】外部クロック信号に対して所定の位相差を有する遅延クロック信号を精度良く生成することができるDLL回路を提供する。

【解決手段】DLL回路1は、制御部10と、第1および第2のノードND(0),ND(n)間に直列接続されたn個(nは2以上の整数)の遅延部D(1)〜D(n)とを含む。第1のノードND(0)には外部クロック信号CLKINが入力される。制御部10は、n個の遅延部D(1)〜D(n)のうち所定の2個の遅延部D(4),D(n)の出力信号CLKA,CLKBの位相差に応じた制御電圧VCを出力する。各遅延部Dは互いに同一の構成を有し、入力された信号に対して制御電圧VCに応じた遅延時間だけ遅延した信号を出力する遅延バッファIと、遅延バッファIの出力を電源電圧の振幅を有する矩形波に整形して出力する整形バッファJとを含む。遅延部D(4)〜D(n)の出力信号が遅延クロック信号として用いられる。

(もっと読む)

クロックデータ再生回路

【課題】複数のVCO間の発振周波数のばらつきを補償し、低ジッタで大きな電源電圧・温度変動耐性を実現する。

【解決手段】第1の発振回路および第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第2の発振回路および第1の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第1〜第2の発振回路の回路間ばらつきによる発振周波数のずれを調整する回路間ばらつき調整信号Ca,Cbを入力する端子を備え、第1〜第2の発振回路はそれぞれ2つの制御端子を備え、それぞれの一方の制御端子に周波数制御信号Aを入力し、第1の発振回路の他方の制御端子に回路間ばらつき調整信号Caを入力し、第2の発振回路の他方の制御端子に回路間ばらつき調整信号Cbを入力する構成。

(もっと読む)

発振器

【課題】 位相雑音特性を劣化させることなく可変周波数帯域の広帯域化を図ることができる発振器を提供する。

【解決手段】 可変周波数帯域の異なる複数の電圧制御発振器(15a、15b)と、複数の電圧制御発振器からの出力のいずれかを選択出力する切替器16と、パラメータに基づいて発振器出力が所定の周波数となるよう制御するデジタルPLL回路13とを備え、制御部18が、各電圧制御発振器に対応して、良好な位相雑音特性が得られるループゲイン及びダンピングファクタを記憶しておき、外部から周波数の値が入力されると、入力された周波数の値に応じて電圧制御発振器を選択し、当該電圧制御発振器からの出力を選択出力するよう切替器16を切り替え、当該電圧制御発振器に対応して記憶されているループゲイン及びダンピングファクタをパラメータとしてデジタルPLL回路13に設定する発振器としている。

(もっと読む)

スペクトラム拡散クロック生成器及び半導体装置

【課題】回路規模の大きなDACやアナログ変調回路を用いずに理想的な周波数特性を得ることが可能なスペクトラム拡散クロック生成器及びスペクトラム拡散クロック生成器を備えた半導体装置を提供する。

【解決手段】動作クロックを生成する電圧制御発振器と、動作クロックの位相と基準クロックの位相とを比較し比較結果により電圧制御発振器の発振の基準となる電圧を生成する帰還制御部と、動作クロックの周波数に変動を与える成分をデルタシグマ変調したパルス信号として生成する変調パルス生成部と、パルス信号の振幅を設定するレベル設定部と、帰還制御部が生成した電圧とレベル設定部によって振幅が設定されたパルス信号とを加算する加算部と、加算部の出力信号を濾波して電圧制御発振器に与える制御電圧を生成する低域パスフィルタと、を備える。

(もっと読む)

クロック供給システム

【課題】基準クロックが異常であるのか、電圧制御発振器が異常であるのか故障原因を特定することが可能なクロック供給システムを提供する。

【解決手段】現用系のシステム200のVCXO203の制御値Xがα<X<βにあるかを監視し、その範囲から外れた時に異常を検出する。この異常検出時にVCXO203の制御値を予め決められた制御値γに設定し、現用系のシステムで運用する。また、この運用状態で予備系のシステム210のVCXO213の制御値X’がα’<X’<β’にあるかを判定し、その範囲内にある場合には基準クロック2aの異常と判定し、現用系のまま運用する。一方、その範囲内から外れている場合には現用系のVCXO203が異常と判定し、予備系のシステムに切り替えを行う。

(もっと読む)

クロックデータ再生回路

【課題】プロセスばらつきによる発信周波数ずれを調整する。

【解決手段】入力データと周波数および位相が同期した再生クロックを出力する発振回路と、発振回路が出力する再生クロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、発振回路のプロセスばらつきによる発振周波数のずれを調整するプロセスばらつき調整信号Bを入力する端子を備え、発振回路は2つの制御端子を備え、その一方の制御端子に周波数制御信号Aを入力し、他方の制御端子にプロセスばらつき調整信号Bを入力する構成である。

(もっと読む)

ローカル信号生成回路

【課題】

周波数ホッピングを用いた通信を行うためのローカル信号生成回路が従来技術に開示されているが、実際に周波数ホッピングを用いたワイヤレスUSBの通信システムにおいては、ローカル信号の出力を開始してから出力が安定するまでに時間がかかり通信における規格を満たすことができないという課題が存在していた。

【解決手段】

第1の周波数で所定のバイアス電圧を中心に振動する第1のローカル信号を出力する第1の発振部と、前記第1の周波数より高い周波数である第2の周波数で前記バイアス電圧を中心に振動する第2のローカル信号を出力する第2の発振部と、前記第1および第2のローカル信号を入力すると共に前記第1のローカル信号および前記第2のローカル信号のそれぞれを選択的に出力し、前記第1のローカル信号および前記第2のローカル信号のそれぞれを出力しない期間においては前記バイアス電圧を出力する選択回路と、を有する。

(もっと読む)

クロックを並列データに整列させるための回路

【課題】クロック信号を並列データに整列させるための方法を提供する。

【解決手段】クロックシフティング回路10は、入来クロック信号8を入来データ信号16に対してシフトし、データクロッキング回路20は、シフト済みクロック信号を使用して、入来データ信号16を再クロックする。クロックシフティング回路10は、位相ロックループ回路2に直列に接続されている複数のDフリップフロップ回路4,6を連結して備える。データクロッキング回路20は、それぞれの入来データビット16を受信し、ミキサ22に対するローカルオシレータとして働く真−補数ブロック50,58を備える。複数のシフト済みクロック信号62,54,64,56は、入来クロック信号16に対して90度、180度、及び270度シフトされたものなど、が生み出される。

(もっと読む)

クロック再生装置および電子機器

【課題】受信データ信号のエッジ位置変動が生じたとしても的確にエッジ検出を行うことが可能で、転送レートの高速化および低消費電力化を実現することが可能なクロック再生装置および電子機器を提供する。

【解決手段】ゲーティング信号生成部130Bは、位相判定部120Bの位相判定信号に応じて、エッジ検出部110の検出結果により立ち上がりエッジ検出を示す信号または立ち下がりエッジ検出を示す信号のいずれか一方の信号を第1のゲーティング信号として、他方の信号を受信データ信号の周期の半周期分を遅延させて上記第2のゲーティング信号として生成し、発振器140Bは、位相が第1のゲーティング信号SGT10および第2のゲーティング信号SGT11によって制御され、受信データ信号RDTに同期したクロック信号CLKを出力する。

(もっと読む)

PLL回路

【課題】高速にロックアップ出来ると共に、十分に位相が収束してからループフィルタの時定数を切り替えることができ、局部発振信号の位相精度及びスプリアス特性を改善できるPLL回路を提供すること。

【解決手段】このPLL回路は、水晶発振器101が基準信号を発振して位相比較器102に入力し、位相比較器102がフィードバックされた発振信号と基準信号との位相差より、制御パルス信号をチャージポンプ103に出力する。チャージポンプ103は、電圧制御信号をループフィルタ104を介して電圧制御発振器105へ与える。電圧制御発振器105は、発振信号を外部及びプログラマブル分周器106に出力し、発振信号は位相比較器102へフィードバックされる。位相比較器102では位相差が所定値に収束した時点でロック検出信号を出力し、ロック検出信号は遅延回路107を経由してループフィルタ104へ入力する。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機特性の固体差や時間変動に応じて適切なループゲインを設定することができるようにする。

【解決手段】周波数・位相同期回路においては、主PLL回路31−1によって同期検波を継続しながら、副PLL回路31−2によって、ループゲインを順次変化させて制御誤差値の計測が行われる。2系統のPLL回路である主PLL回路31−1と副PLL回路31−2は、同じ特性を有する部材を用い、同じ回路構成を有するようにして作成された回路である。また、主PLL回路31−1に設定しているループゲインよりも小さい制御誤差値を求めることができるループゲインが見つかる度に、主PLL回路31−1のループゲインを副PLL回路31−2のループゲインで置き換えていくことが行われる。本発明は、デジタルテレビジョン放送を受信するテレビジョン受像機、録画機器に適用することができる。

(もっと読む)

周波数シンセサイザ

【課題】バラツキ耐性を強くし、温度変動のときに、VCOの周波数変動を補償する周波数シンセサイザの提供。

【解決手段】VCO5と、VCOの発振出力を可変分周回路4で分周した信号22と基準発振回路1の基準信号21を位相比較する位相比較器2と、位相比較結果に基づきVCOへの制御電圧23を生成するループフィルタ3とがPLLを構成し、VCOは、複数の重み付けされた容量素子56〜58と制御信号に基づきオン・オフされる複数のスイッチを備えた容量バンクと、バラクタ54を備える。温度補償ブロック7は、バラクタの補正電位発生回路73と、容量バンクの寄生容量の補正電位発生回路71と、該補正電位発生回路の出力電位を制御信号に基づき重み付け処理するゲイン可変アンプと、バラクタの補正電位発生回路の出力電圧とゲイン可変アンプの出力電圧を加算する加算回路79とを備え、加算回路の出力25によりVCOのバラクタが制御される。

(もっと読む)

PLL周波数シンセサイザ

【課題】ループフィルタの容量素子の面積の増大を抑制しつつループフィルタの自然周波数ωnを小さくすることができるPLL周波数シンセサイザを提供する。

【解決手段】PLL周波数シンセサイザ1Aでは、位相比較部12,ゲート部13,チャージポンプ14,容量素子15,電位調整部16,電圧制御発振器18および帰還分周部19によりループが構成されている。このループにおいて、ゲート部13およびチャージポンプ14と電位調整部16とは並列的に設けられている。位相比較部12に入力される基準発振信号RCLKと帰還発振信号PCLKとの位相差が小さくなるように、チャージポンプ14から容量素子15へ充放電電流Icpが入力され、また、電位調整部16により容量素子15の第1端の電位が調整される。

(もっと読む)

電圧制御発振器

【課題】発振周波数のばらつきを抑えることができる電圧制御発振器を提供する。

【解決手段】本発明による電圧制御発振器は、直列に接続されたN(Nは2以上の整数)個の反転差動増幅器(9)を備えている。N個の反転差動増幅器(9)の各々は、所定の電圧値の定電圧(Vcn1)と制御電圧(Vcnt)とに応じて動作する。N個の反転差動増幅器(9)の各々の動作電流は、定電圧(Vcn1)に応じた電流と、制御電圧(Vcnt)に応じた電流とを加算した電流の値で直接定まる。

(もっと読む)

基準周波数発生装置

【課題】リファレンス信号が取得できなくなっても長時間にわたって高精度な基準周波数信号を出力可能で、使用温度範囲が広く、安価な基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置11は、GPS受信機21と、PLL回路31と、検出器28と、記憶部29と、制御部22と、を備える。PLL回路31は、GPS受信機21からのリファレンス信号に基づいて得られた同期制御信号に基づき、デジタル制御発振器26を制御する。記憶部29には、同期制御信号の制御値と、そのときの電圧値及び温度と、の対応関係が記憶されている。リファレンス信号が得られない場合、制御部22は、前記対応関係と、検出器28が検出した電圧及び温度と、に基づいて自走制御信号を決定し、デジタル制御発振器26を制御する。

(もっと読む)

201 - 220 / 1,199

[ Back to top ]