Fターム[5J106AA05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583) | PLL(位相同期ループ回路) (1,412) | デジタルPLL (213)

Fターム[5J106AA05]に分類される特許

201 - 213 / 213

クロックアンドデータリカバリ回路

【課題】

クロックアンドデータリカバリ回路において、シリアルデータの周波数および位相変動に追従し、良好なジッタ耐力特性となるクロックアンドデータリカバリ回路の提供。

【解決手段】

クロックアンドデータリカバリ回路を構成するフィードバック制御器107が、シリアルデータの周波数および位相変動に対する抽出クロックの追従速度を監視し、時々刻々と適応的に積分器102に対して、フィードバック制御を行なうことで、抽出クロックの追従速度の向上と、ジッタ耐力特性の向上を実現する。

(もっと読む)

周波数合成器

要約書なし。 (もっと読む)

位相同期回路および再生装置

【課題】多様化した仕様要求に応じることが可能なPLL回路および再生装置を提供する。

【解決手段】CPU17が、VCOのあらかじめ基準となる制御電圧CV3とその時の発振周波数を記憶しておく発振周波数記憶部171と、CPUインタフェース13の現在の制御電圧と発振周波数とを検出する発振周波数検出部で検出された現在の制御電圧と発振周波数の関係と、発振周波数記憶部171に記憶されている基準となる制御電圧と発振周波数の関係とを比較する比較部172とを有し、この比較部172での比較結果に基づいて同一条件下における要求周波数に一番近い周波数を出力するVCOセルを選択する。

(もっと読む)

位相同期ループ回路

【課題】 アナログ(特に能動型)ループフィルタのオフセットを自動的に補正して同期クロックまたは周波数の安定性および精度を向上させる。

【解決手段】 このPLL回路は、能動型ループフィルタ30を有する一般的なPLL回路の構成に加えて、周波数比較回路42、DAC制御回路44およびDAC(ディジタル−アナログ変換器)46を備える。オフセット計測モード中は、位相誤差信号生成部(12,14)および周波数誤差信号生成部(18,20)のそれぞれの出力を切り、オフセット計測同期ループ(42,44,46,30,40)において同期を確立させ、そのときのオフセット補正コードEDSを同定して保持する。定常モードでは、DAC制御回路44がオフセット補正コードEDSをDAC46に入力し、DAC46がオフセット補正信号EASをループフィルタ30に与える。

(もっと読む)

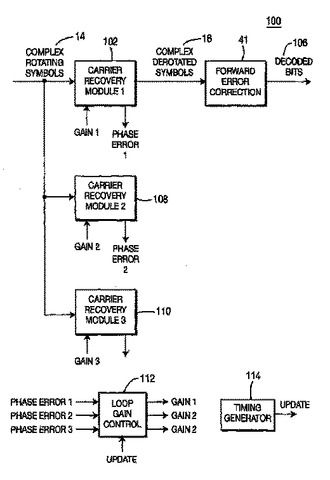

キャリア再生を向上させるシステム及び方法

キャリアを再生するシステム及び方法は、複数のキャリア再生モジュール(102、108、110)を含む。それぞれは、同じ入力シンボル(14)を処理し、それぞれは利得入力及びエラー出力を有する。ループ利得制御(112)は、キャリア再生モジュール(102、108、110)からエラーを受信し、キャリア再生モジュール(102、108、110)に利得を備える。現在の期間中のエラーに基づいて、ループ利得制御(112)は、最低のエラーをもたらしたモジュールを判定し、そのモジュールに関連した利得を最良の利得として選択する。この利得は、次の期間中に復号化するためのシンボル(16)を出力するモジュールに施される。  (もっと読む)

(もっと読む)

位相同期ループ回路

【課題】 ディジタル信号伝送においてキャリア引き込み特性の改善を図り、それを実現する位相同期ループ回路の構成を提供すること。

【解決手段】 位相同期ループ回路が複素乗算器71、位相比較器73、ループフィルタ74、数値制御発振器75等を備え、位相比較器73において、複素数信号の実数部及び虚数部から逆タンジェント特性を得て位相を算出する検出位相算出部76と、位相が異なる2つの直交ディジタル位相変調の信号点配置パターンにおける近傍引き込み点の位相と、上記で算出した受信信号の検出位相とのそれぞれの位相誤差を求める位相誤差計算部77とを備え、各ブロックにおけるパターン毎の位相誤差の2乗から尤度を求めて尤度の高い位相誤差の積分値を位相誤差として出力する。

(もっと読む)

スプレッドスペクトラムクロック生成器及びその変調方法

【課題】製造バラツキ、電源電圧、使用温度、使用周波数が変化しても所望の変調度の周波数変調クロックを供給可能とするスプレッドスペクトラムクロック生成回路を提供する。

【解決手段】制御信号に応じて制御周期間隔で発振周期を可変に制御する第1の遅延制御型発振回路104と、第1の遅延制御型発振回路の出力を分周したクロック信号fo1と、位相比較結果に基づき周波数制御信号Cを出力する制御回路103と、変調最大値Aを決定する変調最大値決定回路106と、変調最大値A内で変調制御信号αを生成する変調信号発生回路107と、出力クロック信号の発振周期を制御信号に応じ制御周期間隔に可変に制御する第2の遅延制御型発振回路108を備えている。

(もっと読む)

遅延同期ループ回路の良否検査方法及び遅延同期ループ回路の良否検査回路

【課題】

ディジタルデータをもとに良否判定可能な比較的安価な検査装置を用いて遅延同期ループ回路の良否検査を行うことができる遅延同期ループ回路の良否検査方法及び、遅延同期ループ回路の良否検査回路を提供する。

【解決手段】

基準信号を所定時間ずつ遅延させたN個のタップ信号を出力する遅延同期ループ回路の良否検査回路及びこの良否検査回路により行う良否検査方法において、各タップ信号をクロック信号とするN個のフリップフロップといずれかのタップ信号をクロック信号とするフリップフロップとを直列接続することによってシフトレジスタを形成し、このシフトレジスタを基準信号の1周期分動作させて、N個目のフリップフロップの出力信号とN+1個目のフリップフロップの出力信号とに基づいて遅延同期ループ回路の良否を判定することとした。

(もっと読む)

アイドル時間ループスタビライザを備えた電荷ポンプPLLに基づいたバーストモード受信器

【課題】

【解決手段】バーストモード受信器は、入来信号を受信するデジタル位相検出器を含む。前記受信器はまた、前記デジタル位相検出器からのパルス信号を受信して、前記入来クロック位相と前記ローカル生成ロック位相を比較して前記電荷ポンプを制御する電荷ポンプと、前記電荷ポンプからの電荷値を受信し、制御信号を生成するループフィルタと、前記制御信号を受信し、回復されたクロックを生成し、前記回復されたクロックをデジタル位相検出器に供給するローカルクロック生成器とを含む。

(もっと読む)

PLL回路

【課題】再生データから得られた抽出クロックを元に再生データの周波数引き込みを行う際に、再生周波数の検出から抽出クロックの自走周波数設定までの処理をデジタル処理により実行する場合でも、確実に周波数引き込みを完了させることができるPLL回路を提供する。

【解決手段】再生データの周波数引き込みを行う際に、再生データの周波数引き込みが完了しない場合には、引き込み状態判定回路11により、周波数引き込み動作の条件を切り替えて、周波数引き込み状態を判定する。

(もっと読む)

タイムスレービング装置

本発明はパケットデータ伝送ネットワークにおけるタイムスレービングのための装置に関する。各データパケットはタイムラベルを有しており、前記装置はネットワークから受信したパケットを受け取ることを目的とした一時記憶手段を有している。

本発明によれば、前記装置は、

一時記憶手段が、ネットワークの特性に依存した所定の時間(IPDV)の間に受信したデータを記録することのできる記憶容量を有している

ように構成されており、

前記装置はさらに、

入来パケットのタイムラベルに応じてローカル受信クロックを再生する手段と、

前記所定の時間(IPDV)と再生されたローカル受信クロックとに依存するある時点において一時記憶手段内のデータを読み取る手段

を有している。

(もっと読む)

サブμ技術に適したデジタル位相同期回路

本発明は、デジタル制御発振器(4)と、位相検出器(11、12、13)と、デジタルループフィルタ(14)とを含む、デジタル位相同期回路に関するものである。上記デジタル制御発振器(4)は、出力周波数を生成するためのものである。上記の位相検出器(11、12、13)は、基準周波数と発振器(4)の出力周波数との位相差を検出するためのものであり、デルタシグマ周波数決定器(11)を含んでいる。上記デジタルループフィルタは、位相検出器の下流に接続されており、デジタル制御発振器(4)を駆動するためのものである。  (もっと読む)

(もっと読む)

データ、特に音声、TV(television)および/または画像データをロックオンおよび/または処理するための回路装置および方法

位相情報が、特に少なくとも1つのアナログ入力信号(50,50’)の少なくとも1つの立ち上がりエッジおよび/または立ち下がりエッジの到着に続いて、少なくとも1つの位相検出器(44)によって検出され、少なくとも1つの増分値(24)が、位相検出器(44)によって出力された出力信号(56)が供給される少なくとも1つのループフィルタ(30)によって決定され、少なくとも1つのランプ発振器(46)に、ループフィルタ(30)によって出力された増分値(24)が供給され、特に、回路装置(100,102,104,106)およびその動作方法が、様々な要求に容易に適合され得るように、回路装置(100,102,104,106)およびデータ、特に音声、TV(television)および/または画像データを、少なくとも1つの位相ロックループ(40)によってロックオンおよび/または処理する方法を、さらに展開するために、位相ロックループ(40)が、本質的にデジタルであり、入力信号(50,50’)、特に入力信号(50,50’)の位相を、少なくとも1つのシステムクロック(52)が供給される、少なくとも1つの時間−デジタルコンバータ(42)によってデジタル化することができ、位相検出器(44)に、時間−デジタルコンバータ(42)の出力信号(54)、特に追加的な位相情報、およびランプ発振器(46)の少なくとも1つの第1の出力信号(62a)、特に少なくとも1つの状態信号が供給され、少なくとも1つの周波数検出器(48)が、ランプ発振器(46)の少なくとも1つの第2の出力信号(64)、特に少なくとも1つのオーバーフローパルスの供給を受け、周波数情報(58)をループフィルタ(30)に出力し、ループフィルタ(30)は、特に少なくとも1つの周波数ロックループ(10)にも割り当てられている、ことが提案される。  (もっと読む)

(もっと読む)

201 - 213 / 213

[ Back to top ]