Fターム[5J106AA05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583) | PLL(位相同期ループ回路) (1,412) | デジタルPLL (213)

Fターム[5J106AA05]に分類される特許

161 - 180 / 213

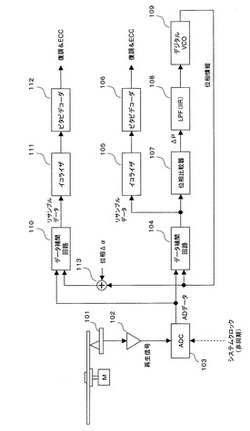

デジタルPLL回路およびデータ再生装置

【課題】回路規模の増大を抑制しながら、異なるPRMLに円滑に対応し得るデジタルPLL回路およびそれを採用するデータ再生装置を提供する。

【解決手段】PR(1,2,2,2,1)に従うデータ補間回路104の他にPR(1,2,2,1)に従うデータ補間回路110を配する。データ補間回路104には、デジタルVCO109によって生成されたPR(1,2,2,2,1)に従う位相情報が供給される。データ補間回路110には、デジタルVCO109によって生成された位相情報の位相を180°遅延させた位相情報が供給される。データ補間回路110に供給される位相情報は、位相調整回路113によって生成される。この構成によれば、デジタルVCO109からの位相情報をもとにデータ補間回路110のための位相情報が生成されるため、別途、データ補間回路110のためのPLL回路を配する必要がない。

(もっと読む)

クロック発生回路

【課題】クロック逓倍してクロック信号を発生するクロック発生回路のロックインタイムを短縮する。

【解決手段】ロックイン状態において、2つの数値データCi,C(i+1)を積和演算器が出力し、各数値データに従って発振器11の発振周期を設定して、その出力クロック信号のパルス数をカウントして第1および第2のカウント値を生成する。これらの2つの数値データと2つのカウント値と周期目標データとに従って、発振器の発振周期を設定する第3の数値データを生成して、発振器の発振周期を設定する。

(もっと読む)

オシレータのデジタル調節

【課題】オシレータの振動周波数の調節を可能とさせ、それにより効率的な態様で且つ顕著なダンピング無しで振動周波数の選択的変更を達成する。

【解決手段】オシレータの振動周波数の調節、特に回路装置によるPLLオシレータのデジタル粗調節に関するものである。回路装置は少なくとも一対のコンデンサ(C,C′)を有しており、その第一端子はオシレータと接続しており、且つ第二端子は、コンデンサ対(C,C′)をオシレータの振動回路内に組込むためにスイッチング装置によって第一基準電位(vss)と選択的に接続させることが可能である。尚、回路装置は、第一基準電位(vss)との該第二端子の選択的接続のための第一FETs(T1,T1′)、互いに第二端子を接続するための第二FET(T2)、及び第一基準電位(vss)とは異なる第二基準電位(vdd)との第二端子の夫々の接続のための第三FETs(T3,T3′)を有している。

(もっと読む)

DLL回路

【課題】ジッタを小さくすることが可能なDLL回路を提供する。

【解決手段】各遅延回路UDCM0〜UDCMn+1を、第1及び第2インバータ15a,15b、第1及び第2ナンド回路16a,16b、スイッチングトランジスタ17及びトランスファーゲート18で構成するとともに、その第2ナンド回路16bを介して前段の遅延回路と後段の遅延回路とを接続するようにした。つまり、各遅延回路にて、1つの第2ナンド回路16bを介して、後段の遅延回路からの出力クロック信号を反転させて前段の遅延回路に出力した。詳述すると、各遅延回路は、その第2ナンド回路16b中の1個のトランジスタを駆動させて後段の遅延回路からの出力クロック信号を反転させて前段の遅延回路に出力する。

(もっと読む)

PLL回路及びPLL回路を構成する可変ディレイラインの制御方法

【課題】 任意の幅で重なり合う発振レンジの設定を行い、PLL回路でのジッタの発生を抑制する。

【解決手段】 デジタルPLL回路10の発振制御回路2には、カウンタ制御回路11、第1のアップダウンカウンタ12、及び第2のアップダウンカウンタ13が設けられ、カウンタ制御回路11は、制御信号Scmが、ある値M=Xである状態からM=X+1である状態に変化するときに、制御信号Scnが段階的にアップカウントせずに、例えばスキップしてアップカウントが可能となる制御信号Smupと、制御信号Scmが、ある値M=X+1である状態からM=Xである状態に変化するときに、制御信号Scnが段階的にダウンカウントせずに、例えばスキップしてダウンカウントが可能となる制御信号Smdnとを入力する。このため、可変ディレイラインから出力されるディレイ信号は製造バラツキ、温度、及び電源電圧などの変動によらず任意の幅で重なり合う。

(もっと読む)

PLL回路、復調回路、ICカード及びICカード処理装置

【課題】本発明は、PLL回路、復調回路、ICカード及びICカード処理装置に関し、例えば非接触により種々のデータを入出力するICカードと、このICカードとデータ通信するICカード処理装置に適用して、簡易な構成で、入力信号が劣化した場合でも確実に入力信号を処理することができるようにする。

【解決手段】90度位相の異なる発振出力信号による位相比較結果の正負を基準にして制御方向を決定し、この制御方向に発振出力信号を制御する。

(もっと読む)

クロック遅延補正回路

【課題】クロック分配回路のクロック遅延を補正するクロック遅延補正回路で固定遅延手段を除き、設計時における設計検証を容易にする。

【解決手段】クロック遅延補正回路10は、分配クロックCLKの周期を示す周期データを生成する周期データ生成手段11と、可変遅延時間を持ち分配クロックCLKを遅延して出力クロックCOUT1を生成する可変遅延回路121と、出力クロックCOUT1の位相と基準クロックCREF1の位相とを比較する位相比較回路122と、位相比較回路122の比較結果に従ってカウントUPするカウンタ123とを有し、カウンタ123のカウント値で可変遅延回路121の遅延時間を制御する。

(もっと読む)

ディジタルPLL装置

【課題】入力信号の周波数が変動してもジッタを低減させることが可能なディジタルPLL装置を提供する。

【解決手段】本発明の一実施形態に係るディジタルPLL装置は、入力信号に対する再生クロックの位相遅れ、位相進みを検出する位相検出器と、位相検出器からの出力信号を積分し、積分値に応じて位相ずれ信号を発生するランダムウォークフィルタ部と、入力信号の周波数値に応じた値を有する周波数信号を生成する周波数検出器と、位相ずれ信号の値と周波数信号の値とを加算した値を有する制御信号を生成する加算器と、制御信号の値を分周比として、マスタークロックを分周した再生クロックを生成する制御分周部と、を備える。制御分周部における分周比の中心値N(Nは自然数)は、周波数信号の値によって定められることを特徴とする。

(もっと読む)

位相同期回路

【課題】入力クロック信号に位相同期化した出力クロック信号を得る為の位相同期回路に関し、特性の経年変化の影響を受けないようにする。

【解決手段】発振器17の出力のクロック信号CLK−CをDDS14により分周して出力クロック信号CLK−Eとし、この出力クロック信号又は出力信号を分周したクロック信号と入力クロック信号との位相を位相比較器12により比較し、位相比較出力信号によりDDS14を制御して、入力クロック信号CLK−Aに位相同期した出力クロック信号CLK−Eを出力する位相同期回路であって、位相比較器12の位相比較出力信号を、ループフィルタ13を介してDDS14に制御値として入力する制御値を所定期間経過毎に格納し、自走モード時に、格納してある制御値を読出して、DDS14に入力する不揮発性メモリ18を設けたものである。

(もっと読む)

遅延固定ループ装置

【課題】 1つのレプリカ遅延部を採用して外部クロックとデータまたは外部クロックと内部クロック間のスキューを補償する。

【解決手段】 遅延固定ループ装置は、レファレンスクロックをそれぞれ遅延させライジングクロックとフォーリングクロックとを生成し、レプリカディレイされたライジングクロックをレファレンスクロックに同期させ、フォーリングクロックをレファレンスクロックに同期されたライジングクロックに同期させる遅延手段と、レプリカディレイされたライジングクロックを提供するレプリカ遅延部と、ライジングクロックの同期を制御し、フォーリングクロックの同期を制御する制御手段と、遅延手段のライジングクロックをレプリカ遅延部へ伝達し、遅延手段で相互に同期された前記ライジングクロックとフォーリングクロックのパルス幅を調節して出力パルスを生成するDCC出力部とを含む。

(もっと読む)

ホールドオーバ機能付きDPLL回路

【課題】デジタル同期網に関し、特にホールドオーバ時において自走周波数制御のために温度補正を行った高精度な基準クロックを生成するホールドオーバ機能付きDPLL回路を提供する。

【解決手段】ホールドオーバ機能付きDPLL回路は、DDSを使用したDPLL回路のホールドオーバモードにおいて、ホールドオーバ検出時における固定のDDS制御値にスレーブ発振器の温度特性から算出した補正値を加算することで、前記DDS制御値を前記温度特性に応じて可変する。

(もっと読む)

マイクロコンピュータ

【課題】温度が変化する環境下において、CR発振回路を利用して生成されるクロック信号の発振周波数自体が一定となるように補正できるマイクロコンピュータを提供する。

【解決手段】マイクロコンピュータのEEPROMに、温度により変動するCR発振回路の発振周期データを記憶しておき、CPUは、温度検出回路によって検出される温度に応じてEEPROMに記憶されているデータを読み出し(ステップS2,S3)、決定した逓倍値をDPLL回路に設定することで(ステップS4,S5)逓倍クロック信号の発振周波数を補正する。

(もっと読む)

デジタルPLL回路及びそれを備えた光ディスク装置

【課題】動作周波数が低く、安価にIC化を行うことができ、設計が容易なデジタル回路を用いて時間分解能の高いクロック信号を生成することができるDPLL回路を備えた光ディスク装置を提供する。

【解決手段】デジタルPLL回路部は、エッジ検出回路部と、クロックデータ生成回路部と、位相差検出回路部とを備え、一周期毎に、デジタルクロックデータから、デジタルクロック信号の立ち上がりエッジ又は立ち下がりエッジの有無を時間分解能単位で示した書き込みタイミング信号を生成して出力する。

(もっと読む)

クロック生成回路

【課題】逓倍回路から正確な逓倍クロックが出力されず、温度等の変動に対する補正能力が低下し、ロックが困難になるという課題があった。

【解決手段】互いに直列に接続された複数個の遅延素子から構成されるデジタルディレイライン56,69,71を有し、デジタルディレイライン56,69,71に対応したカウンタ52,65から出力されるカウント値に応じて複数の遅延素子のいずれかの遅延を選択し、選択した遅延素子およびこれに隣接する1つの遅延素子によって遅延時間を設定制御する。

(もっと読む)

情報再生処理装置

【課題】イコライザやPLL等の回路をデジタル化し、比較的低い周波数の動作クロックを使用しながら高い位相時間分解能を有するデータ再生、クロック再生回路を提供する。

【解決手段】N本のクロックを生成する多層クロック生成手段8と、2値化手段6と、2値化信号をN本の多層クロックのそれぞれでサンプリングするサンプリング手段10と、N本のサンプリング信号を周期T1毎にNビットのデータとして出力するシリアル−パラレル変換手段11と、波形等価処理を行う等価処理手段5と、前記Nビットの等価データを1ビットシリアルの等価信号に変換するパラレル−シリアル変換手段12と、前記Nビットの等価データからNビットの再生クロックデータを出力するデジタルPLL手段13と、前記Nビットの再生クロックデータを1ビットシリアルの再生クロック信号に変換するパラレル−シリアル変換手段14とから構成される。

(もっと読む)

クロック信号発生装置、クロック信号発生方法及びプログラム

【課題】位相の変化に迅速に追従しつつ、クロックスリップが起こり難い(安定した)クロック信号を再生するクロック信号発生装置等を提供することである。

【解決手段】位相比較器1Aは、データ信号と、デジタルVCO1Cの再生クロック信号を基準としたデータ信号の位相の遅れ及び進みを検出する。ランダムウォークフィルタ1Bは、この遅れ進みの回数差を計測して、回数差の絶対値が所定値に達すると、差を打ち消す方向に再生クロック信号の位相を変化させるようデジタルVCO1Cを制御し、計測結果をリセットして計測を再開する。再生位相比較器3は、デジタルVCO1C及び2Cの各再生クロック信号の位相差を検出してランダムウォークフィルタ1Bに通知する。ランダムウォークフィルタ1Bは、通知された位相差が所定量に達している間は、計測結果のリセットやデジタルVCO1Cの再生クロック信号の位相の変更を行わない。

(もっと読む)

デジタルとアナログ制御を用いた電圧制御遅延ラインの遅延セル

【課題】デジタル制御方法とアナログ制御方法を混合して動作範囲を極大化する、デジタルとアナログ制御を用いた電圧制御遅延ラインの遅延セル回路を提供する。

【解決手段】本発明は、差動入力クロック信号が印加される差動入力トランジスタと、電源供給端に一方端が接続され、アナログ制御電圧に応答してファイン遅延量を調節するためのアナログ制御トランジスタ部と、前記アナログ制御トランジスタ部と前記差動入力トランジスタとの間に接続され、デジタルコードに応答してコース遅延量を調節するためのデジタル制御トランジスタ部とを備える。

(もっと読む)

PLL回路およびICチップ

【課題】非接触ICチップに設けられる発振器の周波数を上げることなく、通信の転送レートを上げることができるようにする。

【解決手段】外部からの制御信号に従ってφの値が変更され、cosφで表される発振出力信号と、sinφで表される発振出力信号が可変型発振器71から出力される。可変型発振器71から出力された信号の掛け算、加算等が行われ、信号sin(ωt+φ)と、それを基準としてπ/2だけ位相がずれた信号である信号cos(ωt+φ)が出力される。この出力に基づいて、いまの、クロック信号との位相差などが判断され、位相差に応じた制御信号が可変型発振器71に供給されてくる。本発明は、非接触ICチップに搭載されるPLLに適用することができる。

(もっと読む)

デジタルPLL回路およびその同期制御方法

【課題】瞬時に位相同期を確立し高精度で周波数変動が少ないDPLL回路を実現する。【解決手段】位相差積算部11は,入力基準信号と位相同期ループの帰還信号との位相差をM回分(M≧2)積算する。位相収束点設定部12は,積算した位相差をもとに,測定された位相差を仮の位相収束点として設定することにより,高速に位相を引込む。その位相収束点のもとでの周波数同期完了を確認した後,位相収束点変更部16によって収束点の補正値を更新し,位相差をあらかじめ設定された目的とする最終位相収束点に徐々に近づける。 (もっと読む)

信号処理装置、信号処理方法

【課題】デジタルPLLのループ遅延の短縮化と、そのデジタルPLLによって位相同期が取られた再生データの高精度化とを両立させる。

【解決手段】ビタビ検出用の位相補間フィルタ9と、PLL8にある位相誤差検出用の位相補間フィルタ81とを設ける。位相オフセット演算器84において位相誤差の積算値である位相オフセット量φに応じて、位相補間フィルタ9および位相補間フィルタ81では、タップ係数が逐次更新されるが、位相補間フィルタ81は、位相補間フィルタ9と比較して、タップ数/ビット幅が小さく設定され、PLL8内のループ遅延時間を短縮する。

(もっと読む)

161 - 180 / 213

[ Back to top ]